Tech Tourで判明したRaptor Lakeの内部構造 インテル CPUロードマップ

ASCII.jp / 2022年10月10日 12時0分

前回はZen 4の内部構造の説明だったので、今回はRaptor Lakeの内部構造を説明したい。ちなみに実際の性能云々については今回は触れない(というか筆者もまだ試していない)。このあたりはKTU氏による渾身のレポートが近日中に上がると思うので、そちらをご期待いただきたい。

イスラエルで行なわれたインテルのTech Tour

さて、まず最初にRaptor Lakeの開発体制の話をしよう。9月にIntel Tech Tourなるものがイスラエルで敢行され、今回の情報はこのTech Tourで得たものがメインとなるわけだが、そもそもなぜイスラエルで? というとRaptor Lakeの開発そのものがIDC(Israel Development Center)で行なわれたためであった。

下の画像が、そのIDCが設計を手掛けたプロセッサーの一覧である。2007年あたりまで、つまりPentium 4とPentium Mが並行して設計されていた時代は、Pentium 4系をオレゴン、Pentium M系をイスラエルがそれぞれ手掛けていたのだが、その後開発は別の分け方になったらしい。

ここに掲載されていない製品で言えば、下表がオレゴンの担当になっている。

この一覧を見ると、Bloomfield/Lynnfieldは初のメモリー統合、ClarkdaleはGPU統合(に失敗)、Broadwellは初の14nm、Cannon Lakeは初の10nm、Lakefieldは初のFoveros採用、Tiger Lakeは初の10nm SuperFinといった具合に、プロセスあるいは製造技術で新しい要素を取り込んだケースがオレゴンになりやすい(Haswellは謎だが)。

考えてみるとこれはリーズナブルである。インテルの場合、先端プロセス開発はオレゴンのD1Xのみで行なわれ、そこで製造技術を確立した上で各Fabにその技術を“Copy Exactly(完璧な複製)”の方式で移転する。

オレゴンで開発されていた製品は、いずれも最先端のプロセスや製造技術を使うものばかりであり、つまり製品の開発中にまだプロセスも開発中(量産技術の確立中)ということになる。

こうした場合、CPUの開発拠点とプロセスの開発拠点は物理的に接近している方がなにかと便利である。イスラエルからわざわざオレゴンまで連絡する(あるいはその逆)のは、どうしても連携に支障が出やすいからだ。

インテルのTick-Tockモデル(プロセスの開発とアーキテクチャーの開発を交互に行なう)で言えば、Tickをオレゴン、Tockをイスラエルが担うようなイメージであるが、実際には新アーキテクチャーと新プロセスを同時に投入するような例も多く、「いやもうTick-Tockモデルはやってないから」(VP&GM, Core and Client Development GroupのRan Berenson氏)ということで、新プロセスが「あまり」絡まないものがイスラエルチームの担当という感じである。

もっともIvyBridgeみたいな例外もあるし、今回のRaptor Lakeも厳密に言えばIntel 7ではない(説明会では「Intel 7+というかIntel 6というか、少なくともAlder LakeのIntel 7と同じではない」という説明だったが、公式にはIntel 7として扱うらしい)ので、このあたりの区分けはわりと曖昧らしいが。

プロセッサーパイプラインそのもののIPCは Alder Lakeと同一

そのRaptor Lakeであるが、Intel Innovationなどでも「シングルスレッドで15%、マルチスレッドで41%の性能向上が実現」という数字が出ていた。その内訳が下の画像だ。

実はRaptor LakeもコアそのものはAlder Lakeとほとんど同じ、というかAlder LakeのGolden CoveとRaptor LakeのRaptor Coveは、事実上同一に近いらしい。

もちろんエラッターの修正などは行なわれているだろうから、完全に同一というわけではないし、後述するようにコア外部の変更はいろいろあるが、CPUパイプラインそのものの変更はZen 3→Zen 4よりもさらに少なく、事実上同じとしてみて良さそうである。

それにもかかわらず性能が伸びたのはなぜか? というと、シングルスレッドで一番大きいのが動作周波数の向上で、次がキャッシュの大容量化、最後がメモリーの高速化である。そしてマルチスレッドではスレッド動作そのものの変更が最大の性能向上要因となっている。

まずプロセスについて。上で書いたようにRaptor LakeではIntel 7プロセスそのものが小変更された。あくまでも「小」変更というところがミソで、実際Dan Rogers氏(Senior Director, Mobile Product Marketing)に「なにをいじったの? 構造? 材質? それともジオメトリ?」と突っ込んだものの、明確に「なにをどう変更したか」の答えはなく、その代わり「(結果として)よりチャネルの(電荷の)移動量が大幅に増えた」という返答が戻ってきた。

このIntel 7と改良型Intel 7を比較した場合、以下のようになる。

- 最大動作周波数は5.2GHz→5.8GHzで600MHz向上

- 同じ5.2GHz動作なら50mVコア電圧を下げられる

- 同じコア電圧なら200MHz動作周波数を引き上げられる

実際Alder LakeベースのCore i9-12900KとRaptor LakeベースのCore i9-13900Kを比較した場合、それぞれ1割程度の動作周波数向上が見られる(Base Frequencyだけはむしろ下がっているが)。

もっと興味深いのはこちらの下のスライドだ。241W駆動時のCore i9-12900Kと、65W駆動時のCore i9-13900Kは、ほぼ同等の性能になる、というものだ。

そこから50W増やして115W駆動にすると21%性能向上、176W増やして241Wにすると37%向上する、188W増やして253Wにすると41%向上するというものだが、なんというか筆者だったらこれは間違いなく65W固定で動作させたくなる。

消費電力を3.9倍まで増やしても性能が41%しか上がらない、というあたりが昨今のプロセッサーの最大の問題ではあると思うのだが、もちろん売る側としては「性能が変わらずに消費電力を176W落としました」よりも「消費電力が同じで37%性能が上がりました」の方が売りやすいわけで、性能の伸びは明白とは言え、やや複雑な心境になってしまった。

ちなみにDan Rogers氏によれば、“BIOS SettingでConfigurable TDPを設定して65W動作は可能だし、今後はよりTDPの低いSKUの投入も予定している”とのことで、筆者などにはこうした使い方のほうがありがたい気がする。

キャッシュ容量の大型化とメモリーの高速化などで性能が向上

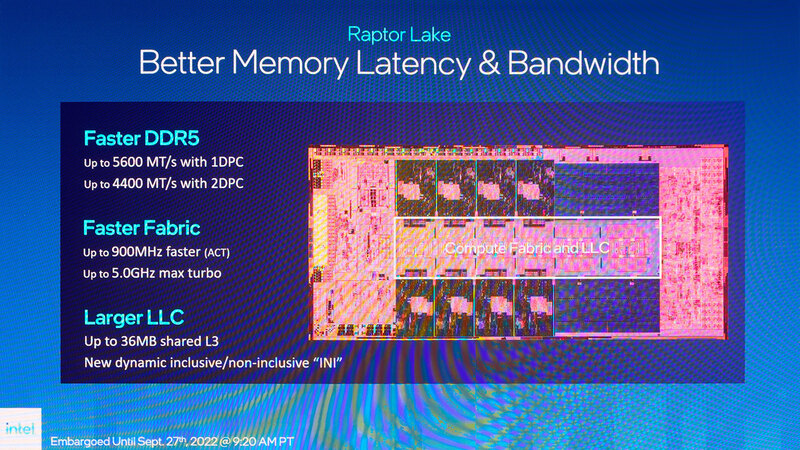

2つ目がキャッシュ容量の大型化とメモリーの高速化である。Raptor Lakeでは 以下の2次キャッシュを搭載しており、2次キャッシュだけで32MBもの大容量キャッシュになった。

- P-Coreあたり2MB

- E-Core Cluster(E-Core×4)あたり4MB(共有)

ちなみにAlder Lakeでは、以下のとおり合計14MBでしかない。

- P-Coreあたり1.25MB

- E-Core Clusterあたり2MB(共有)

3次キャッシュは引き続き、以下のとおりであるが、Raptor LakeではP-Core×8+E-Core Cluster×4になった関係で、3次キャッシュの合計は36MBに増量された(Alder Lakeは30MB)。

- P-Coreあたり3MB

- E-Core Clusterあたり3MB

ただ2次キャッシュと3次キャッシュの総容量がほとんど変わらなくなった関係で、3次キャッシュの扱い方を少し考えたらしい。

今回新たにDynamic INI(Inclusive/Non Inclusive)方式が採用されることになった。動的に2次/3次キャッシュのInclusive/Non-Inclusiveを切り替えられる、というものだ。Alder LakeはNon-Inclusive一択だったが、このあたりに若干の手が入った模様だ。

もう1つの違いは、メモリーである。1DPC(DIMM per Channel)なら最大5600MHz、2DPCでも4400MHzでの駆動が定格で可能になった。

Alder Lakeでは定格ではそれぞれ4800MHz、4000MHzだったから、これも性能に寄与することになる(効果は1~2%のオーダーであるが)。そしてメモリーの高速化に対応するため、内部のファブリックも最大5GHzまで動作周波数を引き上げられるように変更された。

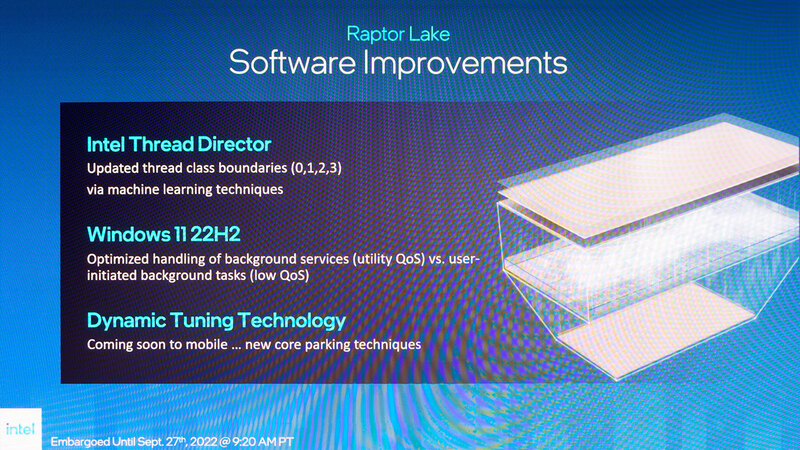

最後のファクターがスレッドである。これはコアそのものではなく、Thread Directorの変更によるものだ。

大きな違いは、Thread Classの管理に、新たに機械学習を利用した仕組み(Perceptronベースという話であったが、詳細は公開されていない)を利用することで、よりE-Coreを積極的に利用できるようになった、というものだ。

もともとのThread Directorの仕組みは、システムの負荷が低い時にはP-Coreを休止させてE-Coreを活用することで消費電力を減らし、一方でシステムの負荷が上がった時にはP-Coreに切り替えて処理性能の向上(というか処理時間の短縮)を図るというものだった。

この原則はRaptor Lakeも変わらないが、これに加えて「さらに負荷が高いときは、P-CoreだけでなくE-Coreもフルにブン回す」というのがRaptor Lakeである。

下の画像はまだ負荷がそれほど高くないケースで、E-Coreは煩雑に負荷が0になる(P-Coreはかなり上に張り付いている)が、さらに高くなるとE-Coreも常時100%に張り付く格好になる。

要するにE-Coreも積極的に利用するようにしたのがRaptor Lakeの変更点で、これによりContents Creationなどの処理では30%以上の性能向上が見られる、というのがインテルの説明である。

説明会では他にもいくつか性能に関するスライドが出てきたが、間もなく実機でのベンチマーク結果も公開されるだろうことと、比較対象がZen 3ベースのRyzen 9 5950Xであり(まだRyzen 9 7950Xの発売前だったから当然だ)、すでにRyzen 9 7950Xが発売されている現時点では今ひとつおもしろくないことを考えて、今回は割愛する。

このあたりはKTU氏のレポートをお待ちいただきたい。全体として言えば、Zen 4とはまた別の方法で「内部構造は大きく変えずに実効性能を引き上げた」のがRaptor Lakeということになる。さて、Zen 4 vs Raptor Lake、どんな結果になるのだろうか?

この記事に関連するニュース

-

Core Ultra 200H/U/Sをあえて組み込み向けに投入するのはあの強敵に対抗するため インテル CPUロードマップ

ASCII.jp / 2025年1月20日 12時0分

-

PCテクノロジートレンド 2025 - Chipset編「Intel」「AMD」

マイナビニュース / 2025年1月7日 10時0分

-

Intelが「Core Ultraプロセッサ(シリーズ2)」のラインアップを一気に拡大 ノートPC向けを中心にデスクトップPC向けや組み込み用も

ITmedia PC USER / 2025年1月6日 23時5分

-

PCテクノロジートレンド 2025 - CPU編「Intel」と「AMD」

マイナビニュース / 2025年1月3日 10時0分

-

PCテクノロジートレンド 2025 - プロセス編「TSMC」

マイナビニュース / 2025年1月1日 10時0分

ランキング

-

1デジ庁、「e-Gov電子申請アプリ」アップデート 更新前に旧バージョンのアンインストール必須

ASCII.jp / 2025年1月20日 16時15分

-

2ソフトバンクが10年ぶりにGalaxyを扱う3つの理由、「月額3円」なぜ実現? 発表会場でキーパーソンを直撃

ITmedia Mobile / 2025年1月23日 11時51分

-

3リアルタイムで文字起こし&翻訳、しかも利用料ゼロ 異色のAIタブレットの実力

マイナビニュース / 2025年1月23日 11時0分

-

4「許さない」 しまむら、“新作ディズニーアイテム”が完売多数で転売 2万5000円での出品も…… 「本当やめて」と怒りの声

ねとらぼ / 2025年1月23日 13時43分

-

5DIYで室温が約10℃変わった「トイレの寒さ対策」が310万再生 コスパ最強のアイデアへ「天才!」「これすごくいい」

ねとらぼ / 2025年1月23日 8時30分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください