Zen 4アーキテクチャー詳細の続報 3D V-Cacheやメモリー、内蔵GPUなど AMD CPUロードマップ

ASCII.jp / 2022年10月17日 12時0分

連載687回でZen 4の内部構造を解説したが、そこで書ききれなかった話を今回まとめて説明しよう。

3D V-Cacheのダイ構造がようやく判明 Zen 4世代でも同じく64MBダイを1個搭載する?

Zen 4のアップデートと銘打っておいていきなりZen 3世代に話が戻るのだが、Zen 4でも3D V-Cache搭載製品が登場する予定になっている。その絡みで3D V-Cacheの物理構造が判明したので説明したい。

3D V-Cacheの最初の内部構造は連載618回で説明したとおり。ついでTech InsightによるTSV周りの解析結果を連載651回で説明した。そして今年のISSCCでAMDが公開した3D V-Cache周りの説明が連載659回である。

これで電気的な接続方法や物理的な構造などはほぼすべて明らかにされた格好だが、唯一不明だったのがダイそのものの容量にまつわる謎である。

もともとZen 3ではCCD上の3次キャッシュの面積はほぼ36mm2ほど。そして3D V-Cacheもやはりダイ1つあたり36mm2ほどになっており、普通に考えたらダイ1つの容量は32MBにならないとおかしいのだが、AMDは一貫して「ダイ1つで64MB」と説明している。この謎を解くにはやはり直接スタッフに聞かないとどうしようもないのだが、やっと今回Zen 4にかこつけてこうした機会に恵まれたわけだ。

さて筆者はこのミスマッチに関し「32MB 3D V-Cacheのダイを2枚積層しており、AMDはこの2枚を1つのダイと称しているのではないか?」とこれまで説明してきたのだが、これは半分正解、半分間違いであった。

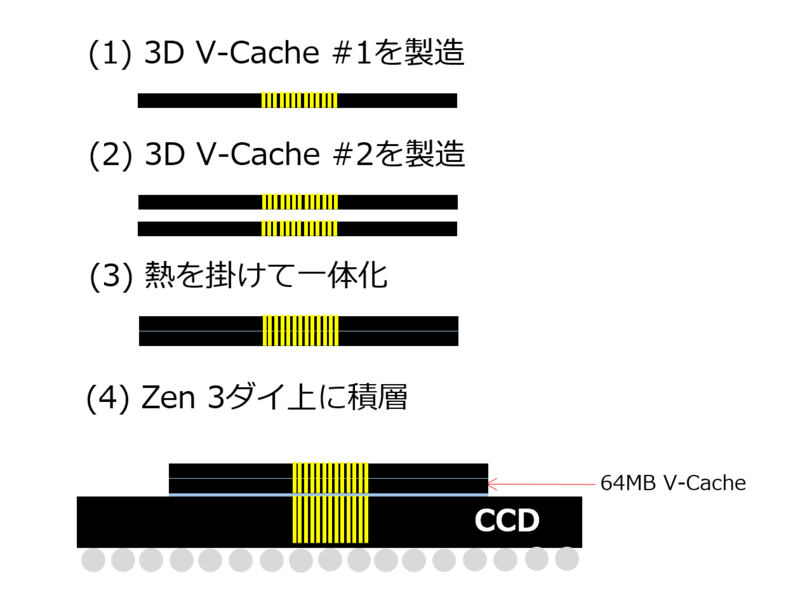

スタッフの説明による3D V-Cacheの製造方法が下図に示す形だ。

まず32MBのSRAMダイを2つ製造する((1)と(2))。このSRAMダイは、複雑な配線層は要らない(SRAMのルーティングはTSVを経由してCCD側で行なう)から、SRAMそのものを構成するのに必要なM1~M2(M3?)+2層程度で製造可能だろう。

ただしCCDと異なり、積層する関係でシリコンそのものは限界まで削る(多分絶縁用のSiO2層を残す程度)必要があるので、CCDよりは製造工程は減る一方で、CCDとは異なる工程が入る格好になる。

こうして2枚の32MB SRAMができたら、これに熱をかけて一体化させる(3)。これによって、AMDのいう「1枚で64MBのSRAMダイ」ができあがる格好だ。最後にこれをCCDに積層(4)して、作業は終了である。なるほど、AMDが「1ダイあたり64MB」と説明するわけである。

なぜこんな構造にしたのか? 逆に言えば、SoICを使って2層を積層する方策を取らなかった理由はなぜか? という話に関しては今回も不明なままである。

ただ可能性で言えば、今でこそSoICはある程度実績も増えてきたが、AMDがZen 3の設計をしていた当時はそこまでの信頼性を確保しきれていなかった、というあたりが正確なところなのかもしれない。

ダイをTSV経由で3D積層することそのものが当時はチャレンジであり、積層するダイを2枚にするのはさらに難易度が上がる、という判断だったとしても不思議ではない。

逆に言えば、Zen 4世代でも同じように1つのダイに集積した上で実装するのか、それとも32MBのダイを2枚積層する形にするのかは、まだ定かではない。ただAMDのこれまでの流れで考えると、自身で開発した新技術をけっこう大事に長期間使う傾向があることを考えると、Zen 4世代でも同じく64MBダイを1個搭載する形になるように思える。

メモリーコントローラーの改善でオーバークロック時に FClkとUClk/MClkの比率を考えなくてもよくなった

AMD Expo(EXtended Profiles for Overclocking)の話は、KTU氏のレビューで詳しく説明されているので繰り返さない。なので、ここではメモリーコントローラー周りの話をしよう。

Zen 3からZen 4で大きく変わったことの1つにDDR4→DDR5への対応が挙げられるが、それとは別にクロックの設定がある。

Zen 3世代では、FClk(Fabric Clock)とUClk(Memory Controller Clock)、MClk(Memory Clock)を独立して設定可能になっていた。もちろんこれは柔軟性を高めるという意味では便利な構造なのだが、特にオーバークロック動作を行なう場合に、場合によってはFClk:UClk:MClkを1:1:1に設定できない場合があった。

一番効率が良いのは1:1:1なのだが、内部の動作速度などの制限もあり、これが可能な最大動作周波数は3600MHzに留まっていた。それがZen 4世代では、ファブリックとメモリーコントローラーの動作周波数が異なっていても、常に最適な速度でデータ交換ができるように変更されている。

この結果として、オーバークロックの際にFClkとUClk/MClkの比率を考えなくても最適な動作が可能になった。したがってオーバークロックの際の設定はAUTO:1:1としておけばよく、この場合スイートスポットはおそらくメモリーコントローラーが動作する上限である3000MHz(=DDR5-6000)ということになる。

ついでにEXPOについても少しだけ触れよう。確かに現状XMPは独自規格であり、秘密保持契約を締結しないと仕様が公開されないのだが、主要なマザーボードメーカーはインテルのマザーボードを設計・製造するにあたってこの秘密保持契約を締結して仕様の開示を受けている。

その意味では、「AMDがXMPの詳細を開示したり、その仕様を拡張したりはできない」のは事実だが、実はマザーボードメーカーがRyzen対応マザーボードでXMPに対応させることそのものは、それほど難易度は高くない。

もちろん秘密保持契約には非インテル系マザーボードへの流用の制限などが入っていると思われるので、これをクリアするためにはブラックボックス的な情報の取り扱いが必要なのは事実だが、ただそれも今に始まった話ではないのであって、そう考えるとEXPOがどれだけ広まるか? というのはやや未知数である。

DDR5そのものはPCやサーバーだけでなく組み込み機器などでも広く使われ始めているし、非x86マシン(Armベースのサーバー)などでも利用されているが、こうした用途向けでオーバークロックメモリ―を利用することはまず考えられず、そうなるとJEDEC標準のSPDで十分用が足りる。

XMPにしてもEXPOにしても、デスクトップPCの、しかもオーバークロック用途向けという非常に限られたニーズに向けた規格である。技術的に言えば、XMPとEXPOの両対応が可能なDIMMというのが存在し得るならば、あるいは普及するかもしれない。

ただXMP/EXPO共にSPDを拡張する形で実装されていることを考えると、現実問題として両対応を謳ったメモリーが出てくる可能性はかなり低い(というか、技術的に可能には思えないのだが、これはXMPの仕様を見ない限り断言はできない)わけで、そうなるとあまり普及しないのでは? という気がしてならない。

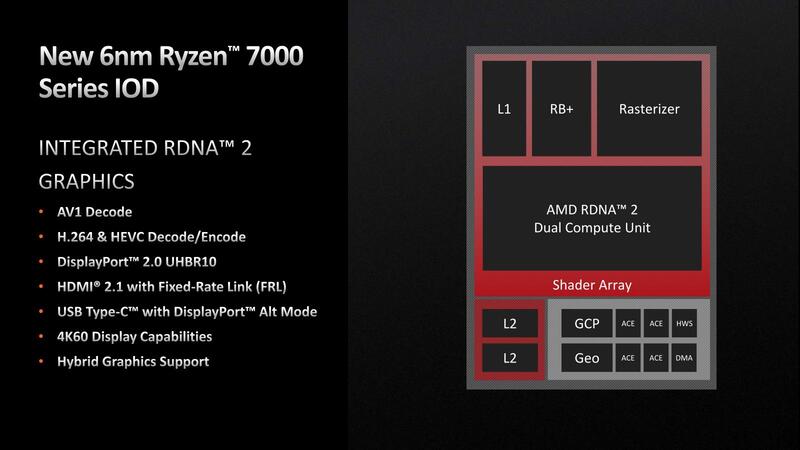

Ryzen 7000シリーズの内蔵GPUは ハードウェア・レイトレーシングに非対応

連載379回で「この内蔵GPUは現行のRDNA 2世代なのでレイトレーシングにも対応するが」と記述があるが、実はこれは間違い。Ryzen 7000シリーズの統合グラフィックは、RDNA 2世代ながらインフィニティー・キャッシュもレイ・アクセラレーターも搭載されない。

これについては質疑応答の中で明確に「実装されていない」旨の返答をいただいている。2 CU/1 WGP構成のGPUにレイ・アクセラレーターを入れたところでほとんど効果がないであろうことは明白だが、それよりも興味深いのはレイトレーシング・ユニットはRDNA 2の必須要素ではない、ということだろうか。

これまでAMDは「RDNA 2ではハードウェア・レイトレーシングが有効になる」という説明をしてきており、ディスクリートGPUやRyzen 6000 Mobileなどでは実際に搭載されていたわけだが、これは必須項目ではなくオプション扱いだったか、Ryzen 7000用のものだけはレイ・アクセラレーターを外す再設計をしたかのどちらか(おそらく前者の公算が高い)であろう。

余談だが、同じく個別の質疑応答の中で、AMD Media Encoderは、ディスクリートGPUを装着している場合でも利用可能だ、という返答をいただいた。なのだが、筆者の環境で試す限りこれを実現できていない。

これはアプリケーション側の対応の問題なのかもしれないが、ディスクリートGPUを装着しながら内蔵エンコーダーを呼び出せるエンコードソフトを今のところ発見できていない(いつも利用しているPegasysのTMPGEnc Video Mastering Works 7では無理だった)。ということで、この情報の正否は当面留保とさせていただきたい。

X670チップセットは 2つのB650を直列でつないだ構造

発売されたRyzen 7000シリーズの最大の難点は価格で、単にCPUだけでなくマザーボードも異様に高価なのがこれに拍車をかけている。特に当初発売されたのはハイエンドのX670Eチップセットのみということで、そもそもX670シリーズと言うだけで高いのに、さらにお値段の張るEモデルということで、「マザーボードが10万円ってどういうこと?」という状況になっている。

いや10万超えのマザーボードそのものはこれまでも多く存在しており、例えば8月の「130万超えPC」のベースである「111万円自腹PC」で利用されたROG MAXIMUS Z690 EXTREME GLACIALは実売26万円近くということを考えれば、安い(?)と言えなくもないのだが。ちなみに筆者はTUF Gaming X670E-Plusを購入したが、これですら5万円弱である。

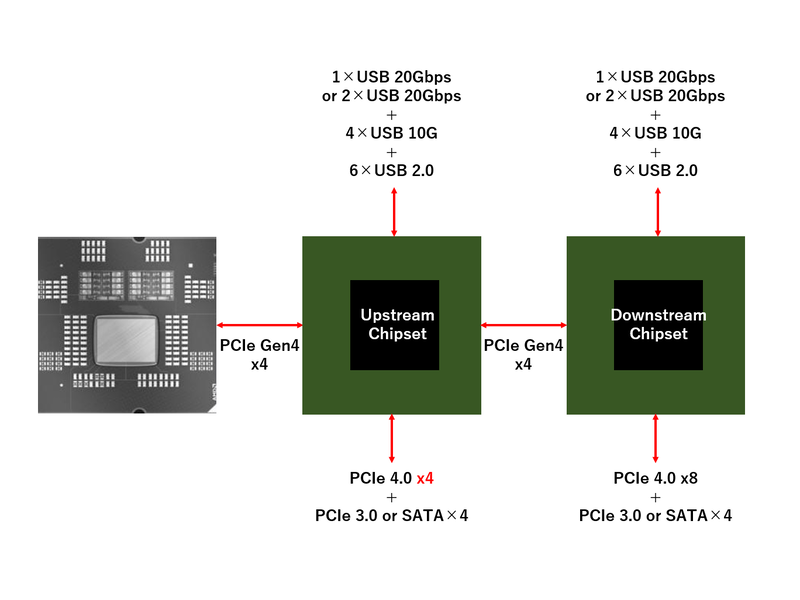

こうした理由の1つは、X670/X670Eが2チップ構成であることに起因する。

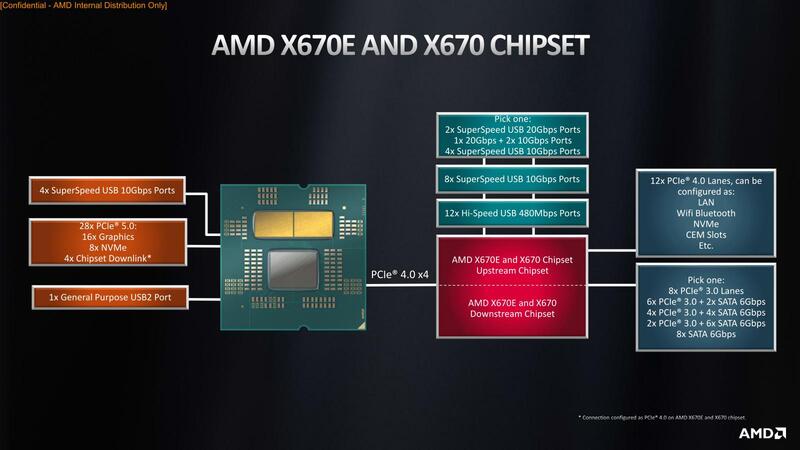

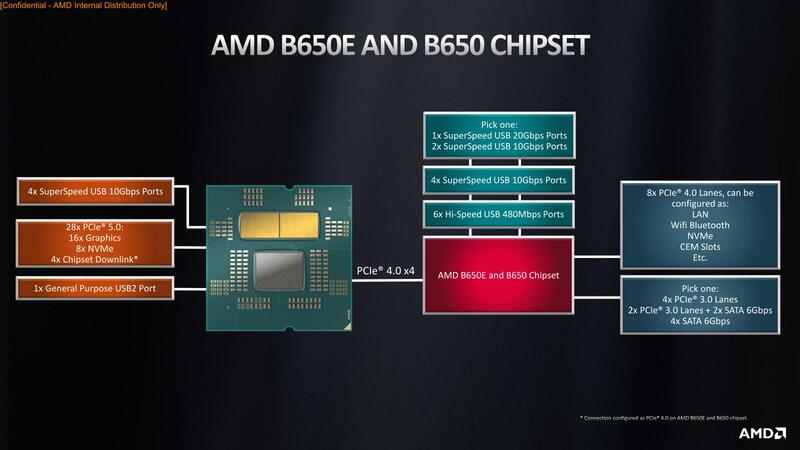

これはどういう構造か? というのが下図である。要するにX670とは、B650を2つ直列につないだ構造と考えれば良い。

この結果として、Upstreamチップセットの方はDownstream側と接続するために、PCIe x4を割り当てる必要がある関係で、外部に出せるPCIe 4.0レーンはx4に減るが、Downstream側はx8なので合計12レーンとなる。

またPCIe 3.0とSATAは自由にポートを割り当て変更可能なので、構成としては以下のようになる(どうもUpstreamとDownstreamで構成を変えるのはNGらしい)。

- PCIe 3.0×8

- PCIe 3.0×6+SATA 3.0×2

- PCIe 3.0×4+SATA 3.0×4

- PCIe 3.0×2+SATA 3.0×6

- SATA 3.0×8

要するに拡張性を確保するためにディジーチェーンでB650を2つつないだのがX670、と考えるのが正しいわけで、そりゃ価格も上がれば消費電力も上がるわな、という感想しか抱けない。

実際のところ、B650で足りないほどの拡張性が必要というケースでなければB650のままで十分であり、価格も消費電力も下がることが期待できると考えると、一般のユーザーにはB650ベースの製品をお勧めしたいところである。

この記事に関連するニュース

-

AMD「Ryzen 7 9800X3D」搭載 TSUKUMOのゲーミングデスクトップPC「G-GEAR」

J-CASTトレンド / 2024年11月18日 12時0分

-

iiyama PC、Ryzen 7 9800X3D搭載ゲーミングPC発売開始

マイナビニュース / 2024年11月15日 13時9分

-

Ryzen 7 9800X3Dを試す - ゲーミングCPUの本命か? 第2世代3D V-Cacheの威力を徹底検証

マイナビニュース / 2024年11月6日 23時0分

-

ゲーミングCPUの真打「Ryzen 7 9800X3D」発表! 第2世代3D V-CacheはCPUの“下”に搭載

マイナビニュース / 2024年11月1日 13時45分

-

ゲーミングに最適化したキャッシュ爆盛りデスクトップCPU「Ryzen 7 9800X3D」正式発表 米国では479ドル

ITmedia PC USER / 2024年10月31日 23時40分

ランキング

-

1Microsoftの「リコール」機能、Copilot+ PCでテスト可能に(要Insider)

ITmedia NEWS / 2024年11月24日 8時23分

-

2iPhone基本の「き」 第629回 ロック画面下部にあるアイコンが削除・変更可能に - iOS 18の新機能

マイナビニュース / 2024年11月24日 11時15分

-

3みんなが狙っているモデルはこれ! 「スマートウォッチ」ほしいものランキングトップ10&おすすめ Xiaomiの人気シリーズがランキングを席巻!【2024年11月版】

Fav-Log by ITmedia / 2024年11月24日 7時15分

-

4“謎スマホ”と呼ばれた中国EVメーカーの新モデル「NIO Phone N2401」を見た

ITmedia Mobile / 2024年11月24日 10時5分

-

5ただの古いパイプ椅子だと思ったら…… JR東日本が販売している“鉄道古物”にツッコミ殺到 「この商品が刺さる層いるのか」「嘘ではない」

ねとらぼ / 2024年11月23日 20時40分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください