Raptor Lakeの開発を半年短縮できたのはイスラエルチームのおかげ? インテルCPUロードマップ

ASCII.jp / 2022年10月24日 12時0分

連載688回に続き、Raptor Lakeの紹介をしていこう。ちなみにKTU氏による渾身のRaptor Lakeベンチマークその1とその2はもうお読みいただけたかと思う。実は筆者は全然ベンチマークが間に合っておらず、今この原稿を書いている横でまだベンチマークが回っている始末である。

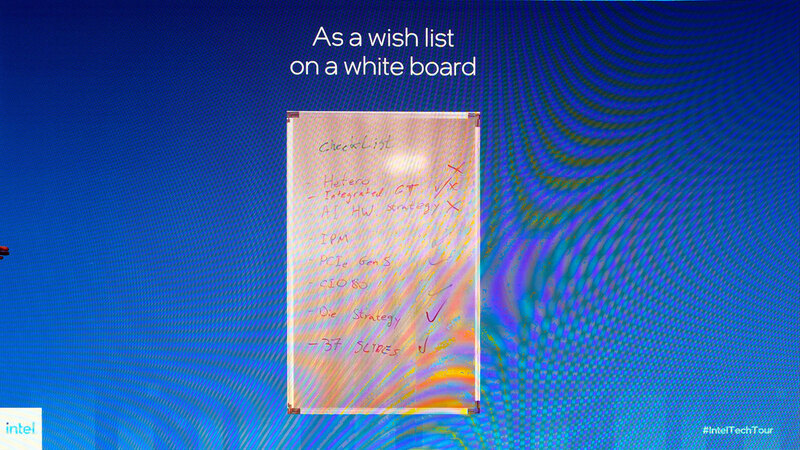

White Boardの謎

イスラエルツアーの初日のスライドはいろいろあったのだが、説明が今一つ足りておらず理解できなかったのが下の画像だ。

このWhite Boardの謎解きをしてくれたのは、連載688回でも名前が出てきたRan Berenson氏(VP&GM, Core and Client Development Group)である。氏曰く、「これは、私やチームのメンバーが(USに居た)Jim Kellerの所に行ってプレゼンテーションしたときのものだ。このミーティングでは(Alder Lakeの)重要となるコンポーネントに対しての判断を行なった。右側に×がついているというのは、当初ヘテロなCPU構成やグラフィック統合、AI H/Wの搭載などがいずれも不要と(Jim Keller氏が)判断したという記録だ」という。

ちなみに氏はそこから2~3ヵ月かけて最高経営責任者に対して、効率的なプロセッサーを作るためにはヘテロ構成にするしかないと説得をした結果として、Alder Lake(やRaptor Lake)のP-CoreとE-Coreの混合構成とすることが決まったのだとか。なかなかおもしろい逸話であった。

Alder Lakeの基本設計は2018年にはある程度終わっていた?

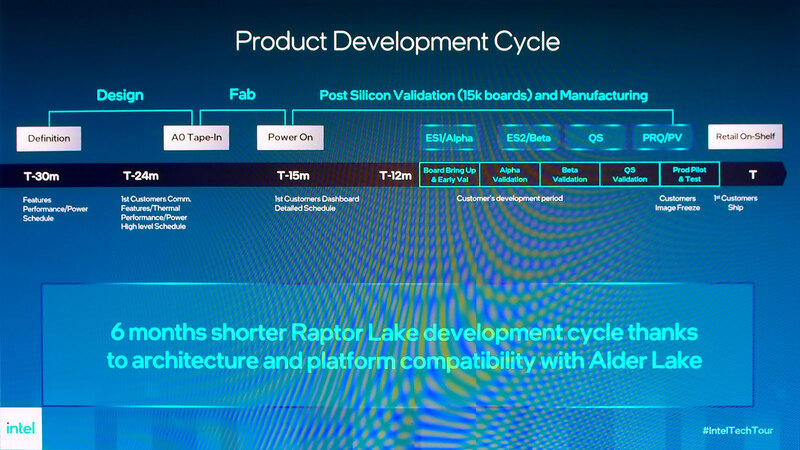

これもイスラエルツアーの初日にあった話である。下の画像はAlder Lakeの開発サイクルである。Alder Lakeでは30month、つまり30ヵ月(=2年半)で要求定義から製品出荷に漕ぎつける、というおそろしく迅速な開発スケジュールが実現した。

このうちテープイン~テープアウトは12~15ヵ月ほどかかるため、要するにディフィニションからテープインまでがものすごく迅速だったことになる。バリデーション、つまり検証にはおおむね1年を要しており、逆算するとディフィニションからテープインまでの期間が猛烈に短かったことになる。

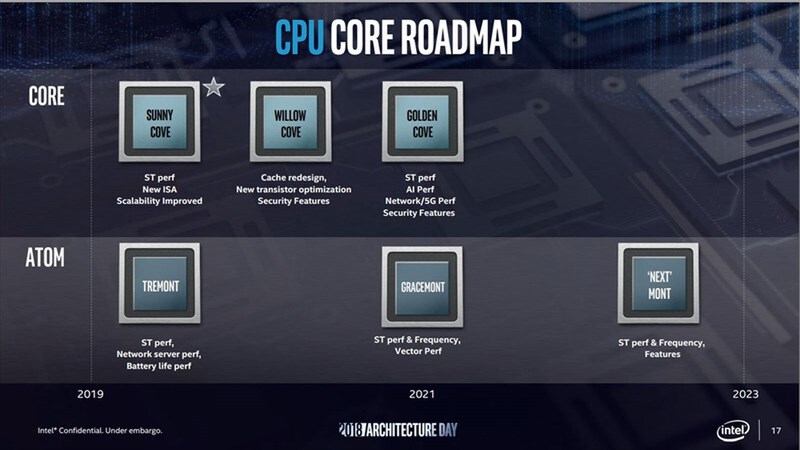

理由の1つは、すでにCPUコアやGPUコアのIPは完成していた、ということもあるのだろう。P-CoreはGolden Coveであるが、このコアの名前そのものは2018年のArchitecture Dayですでに名前が出ている。

ということは、この時点でコアそのものが完成していたわけではないにせよ、ある程度基本設計は終わっていると考えていいだろう。つまり前述のAlder Lake開発サイクルの画像にあるT-30mという時点でコアの論理設計はほぼ終わっており、比較的早く物理設計に入ることが可能だったと思われる。

これはE-Coreの方も同じで、Gracemontコアそのままだから、これも論理設計は容易だっただろう。GPUも基本同じであり、まったく新規だったのはDDR5のメモリーコントローラーくらいのものであろう。つまりディフィニションのステージは、単にこうした「すでに存在するIP」をどう組み合わせるかのみだったからこそ迅速に構築できたという話で、おそらくGolden Coveコアの検討開始時期から数えれば4年以上を要しているものと思われる。

Raptor Lakeの製品開発サイクルを半年短縮できたのは Alder Lakeの物理設計を流用できたため

話をRaptor Lakeに戻すと、この製品開発サイクルを半年短縮できたとしている。

どうしてこんなに短縮が可能になったか? と言えば、Alder Lakeの物理設計のかなりの部分をそのまま流用できたためだろう。連載688回でも触れたが、Alder LakeのIntel 7とRaptor LakeのIntel 7+の違いはチャネルの電荷移動量であって、トランジスタや配線の寸法などに変更はない模様だ。

もちろんチャネルの電荷移動量が変われば回路のタイミングが変わることになるから、検証まで省くことはできないにしても、通常の物理設計の手間を大幅に節約できたと考えられる。

もっとも逆に言えば、これはコアそのものには一切手を加えず、2次キャッシュの容量と動作周波数の変更程度しか差がないから可能だった技であって、同じように基本的な構成は変わらないとしつつ、バッファ容量やOpCacheの帯域などを強化したZen 4コアではやはり物理設計のやり直しが発生したものと思われる。

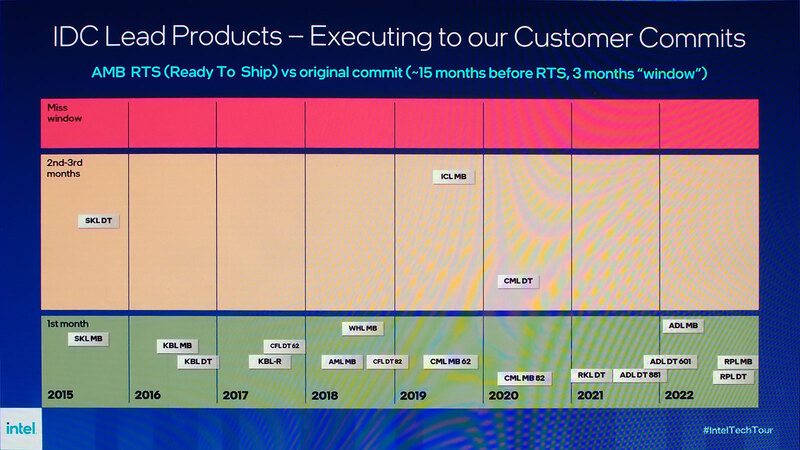

製品開発サイクルの話でもう1つ。下の画像はSkyLake以降のデスクトップ/モバイル向けプロセッサーの出荷状況をまとめたものだ。横軸は時系列、縦軸は「アナウンスした出荷予定日」と「実際の出荷日」の差である。

いくつか例外(Sky Lake DesktopとIce Lake Mobile、Comet Lake Desktop)はあるものの、ほとんどの製品はアナウンスした出荷予定日から1ヵ月以内に出荷ができている、という話だ。

これはイスラエルチームの優れた開発能力を示すものだという話ではあるのだが、前回も書いたように、まったく新しいプロセスやパッケージが絡む場合は基本オレゴンチームが開発しており、そのプロセスが足を引っ張って製品が遅延した、という過去の経緯を考えると、単にイスラエルチームが優秀であるから遅延が少ないと纏めてしまうのはやや違う気もする。

ちなみに今後これがどうなるか? は少し怪しくなっている。10月11日、Pat Gelsinger CEOはInternal Foundry Modelを発表した。

これはなにか? というと、これまでインテルは社内向けと社外向けで別々の対応を行なってきた。外部顧客に対してはTSMCやSamsung、Globalfoundriesと同じようにファウンダリーサービスを提供するが、社内向けは設計部門と製造部門が一体になる形でチップを製造してきたわけだ。

ただここ数年に関して言えば、この社内一体化モデルの弊害がむしろ出ていたと言わざるを得ない。今回のInternal Foundry Modelは、端的に言えば社内向けであっても社外向けと同じように扱うという話である。これまでの場合、製品製造がうまく行かない場合に、その責任を設計部門と製造部門がお互いに擦り付け合うなんてこともあったらしいのだが、今後は設計部門と製造部門の責任範囲がきちんと決まることになる。

これがなにを意味するかと言えば、今後は新プロセスを導入する製品がオレゴンの担当になるとは限らないということだ。プロセスの開発そのものはファウンダリー側、つまりFab D1Xの担当になり、そこにオレゴンの設計チームは原則関わらないことになる(関わったら、設計と製造を分離することにならない)。

そして設計チームは製造部門からPDK(Process Development Kit)を受け取り、それをベースにプロセッサーの物理設計を行なう形になる。こうなると、別に設計センターがD1Xのそばにある必要はないわけで、イスラエルチームが新しいプロセスを採用した製品の担当になることもあり得る。そうなった時に、上の画像がどうなるのか? は少し怪しい気がする。

Z790とZ690チップセットの違いは? 今後はThunderbolt 4を搭載しないマザーが出てくる?

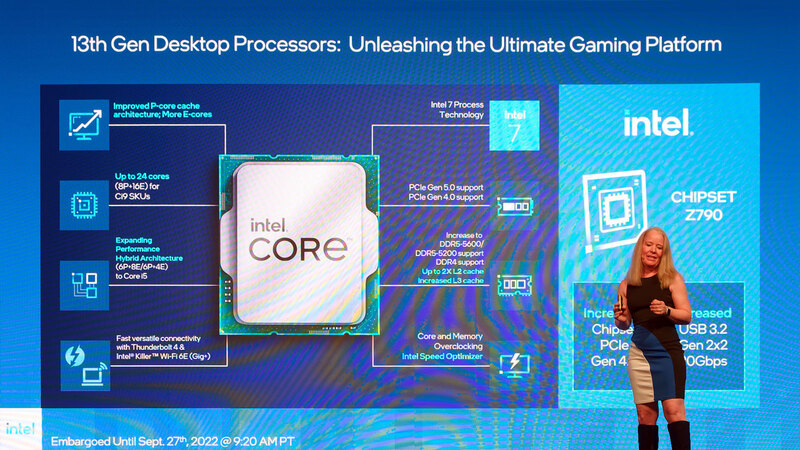

最後はチップセットについてだ。Raptor Lakeにあわせてインテル700シリーズチップセットが投入される。まず商品化されたのはZ790であるが、おそらくはこの後普及帯向けのチップセットも投入されることになるだろう。

ただ気になるのは、Z790とZ690の違いである。これはインテルの担当者に確認したところ、以下の返事が返ってきた。

- USBポート数の増加。ここにはUSB 3.2 Gen 2x2の追加サポートも含まれる

- PCHからのPCIe Gen4レーンが最大20になり、これは600シリーズより8レーン増えている。またPCIe Gen3を8レーンサポート

- Discrete Thunderbolt 4コントローラーをサポート

ただIntel Arkで詳細にスペックを確認すると、下記が正確らしい。

- USBポートの合計そのものは14で変わらず。ただしZ690はUSB 3.2 Gen 2x2が最大4ポート、USB 3.2 Gen 2x1が最大10ポート、USB 3.2 Gen 1x1が最大10ポート、USB 2.0が最大10ポートなのに対し、Z790はUSB 3.2 Gen 2x2が最大5ポート、USB 3.2 Gen 1x1が最大10ポート、USB 2.0が最大10ポートとなっている。要するにUSB 3.2 Gen 2x2として使えるポートが1つ増えた。

- PCIeのレーン数は28のままで変わらず。ただしZ690ではPCIe 4.0は最大20レーンで、残りはPCIe 3.0だった。Z790ではPCIe 4.0でも最大28レーンまで可能になった。ただしうち8レーンはPCIe 3.0としても利用可能。

あと説明されなかった違いとしてIntel Optane Memoryのサポートがなくなった、というのがあるが、これはOptane Memoryそのものがなくなったのが理由であろう。

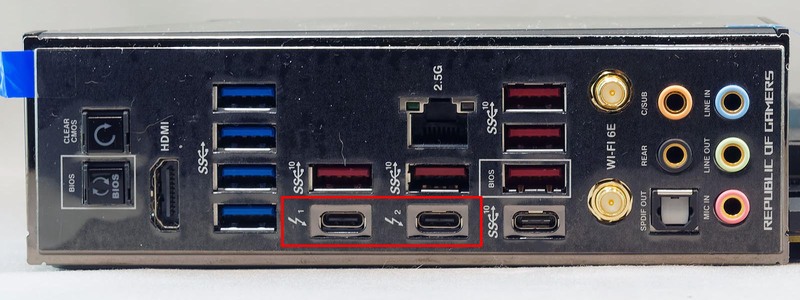

聞いたところZ790マザーボードは(とりあえず当初リリースされるものは)すべてThunderbolt 4コントローラーが実装されることになっているそうだ。実際(KTU氏も評価に使った)ASUSのROG Maximus Z790 HeroのバックパネルにはThunderbolt 4が2ポート用意されているのがわかる。

ただ、そんなオンボードでわざわざディスクリートThunderbolt 4のコントローラーを搭載するくらいなら、いっそチップセットにThunderbolt 4のコントローラーを統合してしまえばいいのでは? と思ったのだが、(これも連載688回で名前がでた)Dan Rogers氏(Senior Director, Mobile Product Marketing)に確認したところ「それをやると(チップセットの)価格が上がるので、ディスクリートのままの方が良いと顧客(=マザーボードメーカー)が主張するのでこうなった」という返事だった。

ということはつまり、Z790マザーボードにThunderbolt 4を搭載するのは最初だけで、そのうち廉価版の(Thunderbolt 4コントローラーを搭載しない)Z790マザーボードが出てくる(でなければ、ディスクリートにしても価格が下がらない)ものと思われる。

ちなみに筆者宅の環境で言えば、Core i9-13900KはASUSのPrime Z690-Aで問題なく稼働した。X670Eほどではないにしても、無理に高価で消費電力の大きめなZ790マザーボードを選ばなくても良いように思われる。

この記事に関連するニュース

-

Core Ultra 7 265K&RTX 4070 Ti SUPER搭載ゲーミングPC、空冷クーラーでも本当に大丈夫?

ASCII.jp / 2024年11月16日 10時0分

-

GEEKOMのMini Air12 LiteミニPCが200ドル以下で販売中

PR TIMES / 2024年11月8日 19時15分

-

GEEKOMのMini Air12 LiteミニPCが200ドル以下で販売中

共同通信PRワイヤー / 2024年11月5日 11時40分

-

【TSUKUMO】インテル Core Ultra デスクトップ・プロセッサー (シリーズ 2) を搭載したプロフェッショナルGPUモデルを発売

PR TIMES / 2024年10月29日 14時15分

-

Arrow Lakeがついに市場投入! ASRock・ASUS・MSI・GIGABYTEが一堂に会して製品アピール、Micronの姿も

マイナビニュース / 2024年10月28日 14時33分

ランキング

-

1「ドラクエ3」HD-2D版にファミコンで挫折したおっさんマンガ家も夢中! ネットで評価が割れた理由とは?

ITmedia NEWS / 2024年11月24日 12時20分

-

2iPhone基本の「き」 第629回 ロック画面下部にあるアイコンが削除・変更可能に - iOS 18の新機能

マイナビニュース / 2024年11月24日 11時15分

-

3Twitter Japanが社名変更、「X Corp. Japan」に

ITmedia NEWS / 2024年11月24日 15時8分

-

4Minisforumが「ブラックフライデー」を開催! 新商品も最大41%お得に買える

ITmedia PC USER / 2024年11月24日 0時0分

-

5みんなが狙っているモデルはこれ! 「スマートウォッチ」ほしいものランキングトップ10&おすすめ Xiaomiの人気シリーズがランキングを席巻!【2024年11月版】

Fav-Log by ITmedia / 2024年11月24日 7時15分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください