フランスの新興企業が開発したIoT向けチップGAP AIプロセッサーの昨今

ASCII.jp / 2022年11月7日 12時0分

久々のAIプロセッサーであるが、今回はフランスのGreenwaves Technologiesが提供するGAPシリーズチップを取り上げたい。ただ、その前に連載684回のアップデートというかニュースを1つご紹介しよう。

TSMCがBirenのBR100/BR104の生産を中断

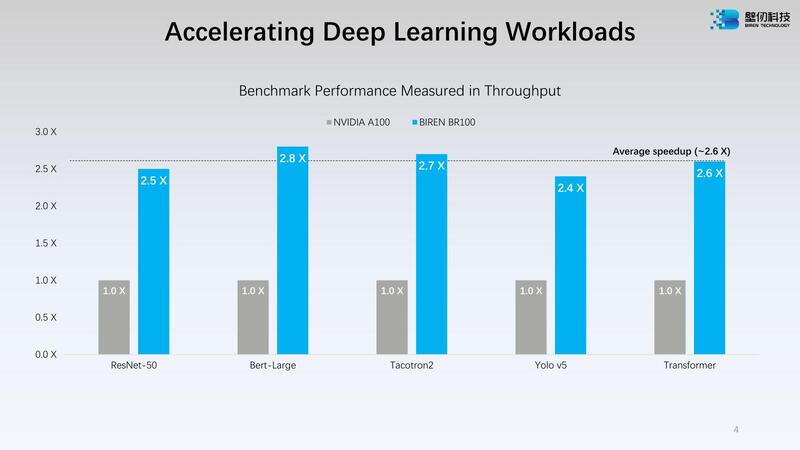

タイトルのとおりなのだが、10月24日のTAIPEI TIMES(台北時報)やBloombergが一斉に、TSMCがBiren TechnologyのBR100/104の生産を中止したことを報道した。

公式な情報ではないのでTSMC、Biren Technology共に今のところ一切リリースを出していないのだが、そもそも現在米国は中国に対して半導体技術の規制を厳しくしており、8月末には米国当局がNVIDIAにA100およびH100の輸出を停止することを要請したという報道があったほどだ。

筆者が連載684回でも説明したように、BR100はNVIDIA A100を上回る性能を発揮するとBiren Technologyは主張しており、仮にこれを野放しにするとA100/H100の輸出規制の意味がなくなってしまう。このためにTSMCがBR100/104の製造を自主規制したということらしい。

連載684回の最後で「こうしたハイエンドGPGPUにはピーク性能ではおよばないが、その分安ければ“Poorman's DGX”的な位置付けで売れそうには思う。」と書いたが、当面米国による中国向けの半導体技術の輸出規制が解けることはない。

しかもウクライナ戦争に絡み、中国からロシアに電子機器が輸出されているという話が報じられている現状では、厳しくなることはあっても緩くなることは考えにくいことを考えると、BR100/104が近い将来に量産が復活する望みは非常に薄いだろう。

RISC-Vコア「だけ」のGAP8とGAP9

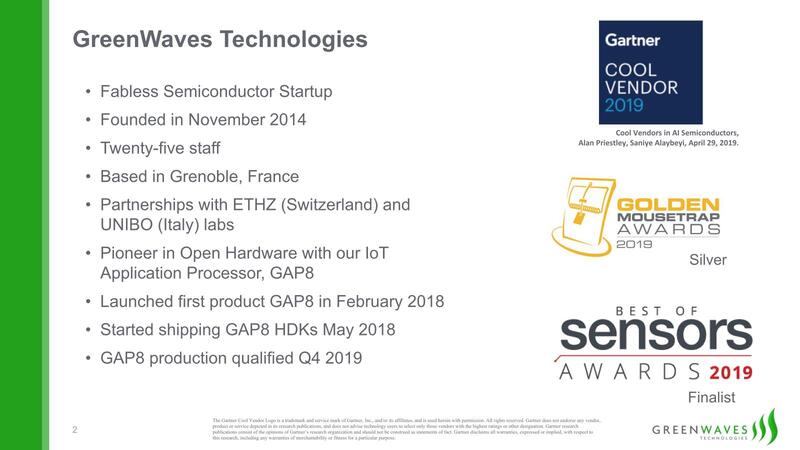

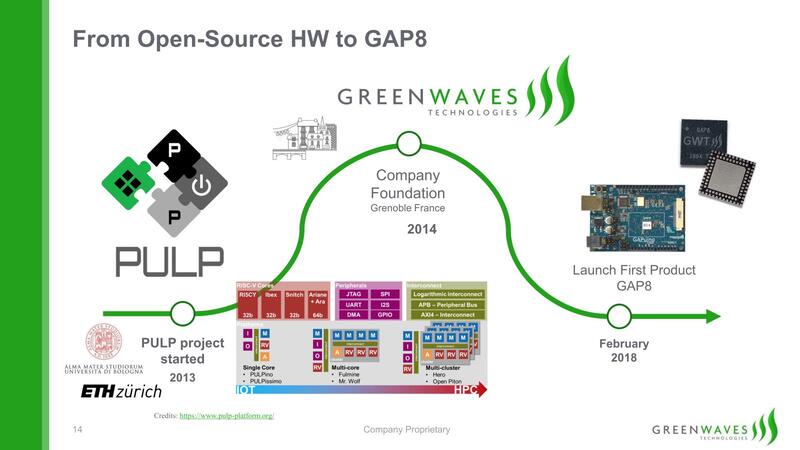

ということで今週の本題はフランスのGreenwaves TechnologiesのGAP8とGAP9である。同社は2014年にフランスのグルノーブルで設立された。

余談だがグルノーブルはアルプスの都と言う別名がある、要するにアルプスの山の中の都市であるが、STMicroelectronicsが工場をここに置いており(Google Mapで見ると見事にモザイクがかかっているし、もちろんストリートビューでも見えない)、その北西にはESRF(欧州シンクロトロン放射光研究所)が位置する。その脇にはGIANT(Grenoble Innovation for Advanced New Technologies)が、またSTMicroelectronicsのすぐ南東にはグルノーブル理工科大学があり、フランスにおける科学や電子産業の中心地の1つとしていいだろう。

創業者であるDenis Mestdagh氏はSTMicroelectronicsのディレクターやST-Ericcsonの最高技術責任者、CEA(フランス原子力・代替エネルギー庁)の特別研究員などを歴任した後でGreenwaves Technologiesを設立、2019年まで最高戦略責任者を務めて離脱された。

ただ共同創業者のLoic Lietar氏(最高経営責任者)とEric Flamand氏(最高技術責任者)、Joel Cambonie氏(開発部門責任者)は現在も同社におられる。2016年の時点では創業者4人を含めて10人のスタッフと5人のパートタイム研究者だった同社も2019年には25人のスタッフを抱え、現在は45人+1匹(Chief Mascot Officerだそうである)から構成される。

約1年半遅れで発売された 監視装置向けプロセッサー「GAP 8」

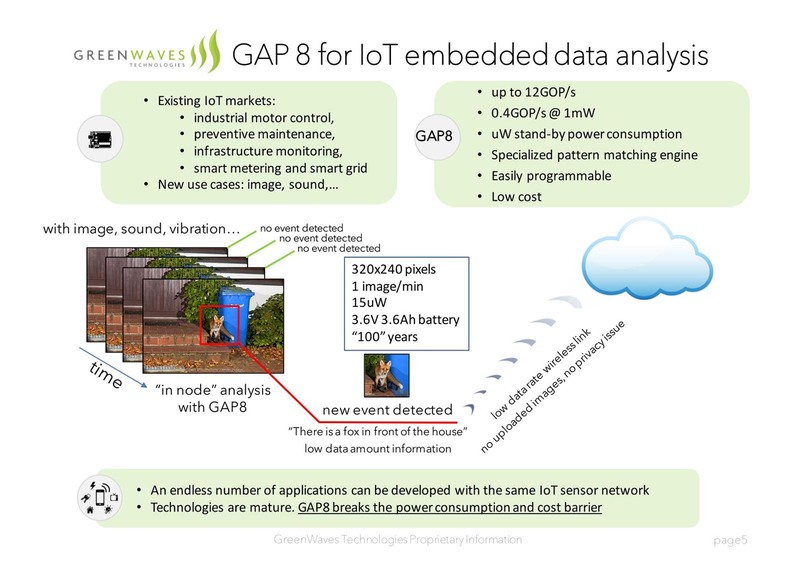

さてそのGreenewaves、ターゲットとするのはエンドポイントIoTである。下の画像が最初の製品であるGAP8のアプリケーション例である。

画像だったり騒音、振動と言ったセンサーで起動し、異常が発生したと検知したらそれをホスト側のプロセッサーに送って通知を送るといったアプリケーションである。こうした用途なので低コスト、低消費電力が求められるのは当然である(ここにあるように100年の電池寿命が必要とはさすがに思わないが)。

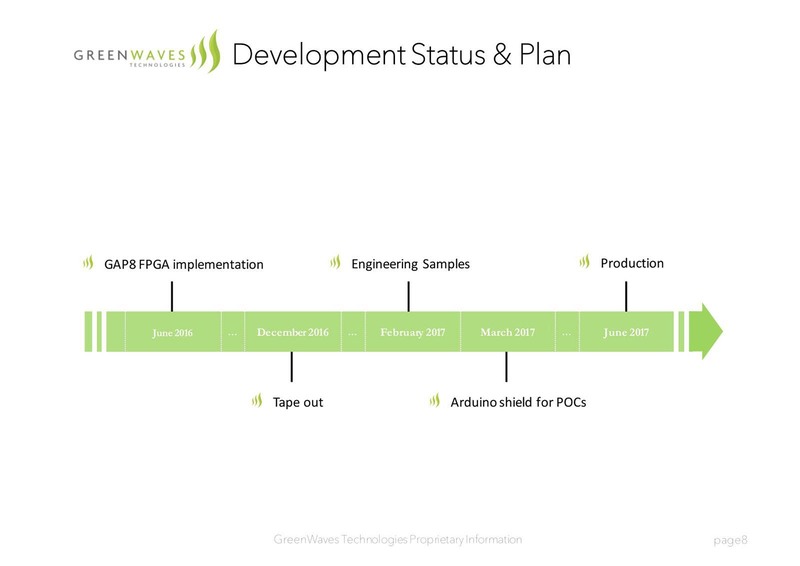

上の画像は2016年のものだが、この時点でGAP8の基本的な部分はFPGAでほぼ実装が完了しており、これをベースに2016年末にテープアウト、2017年6月頃には量産が始まる、というわりと前向きな予定だった。

もっともこれは楽天的過ぎたようで、最初の量産シリコンがリリースされたのは2018年2月、HDK(Hardware Development Kit)が出荷されたのは2018年5月、量産シリコンの品質検証が終わったのは2019年第4四半期とされるため、当初の予定から1年以上遅れた形になるが、少ないエンジニアで量産まで漕ぎつけるのは大変なことを考えると、これはそれほど大きな問題ではないと思う。

すでに同社のオンラインストアでGAP8プロセッサーや開発キット類は購入可能である。

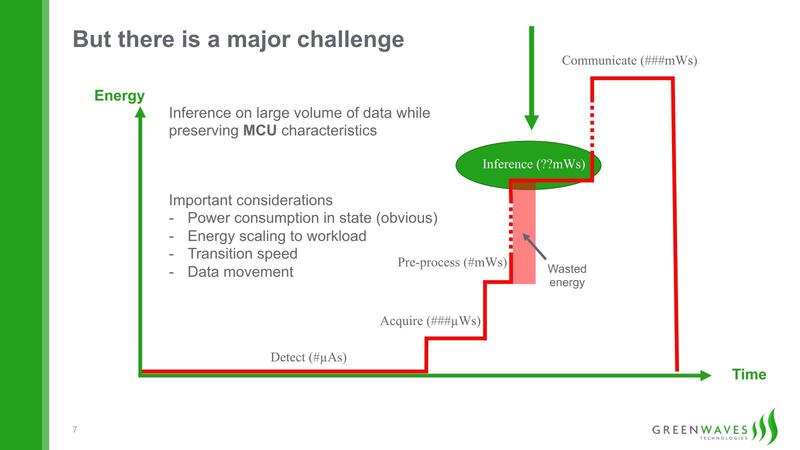

ターゲットアプリケーションとして示されたのは下の画像で、Greenwavesが言うようにもうエンドポイントIoT向けの用途である。これを実現するのに問題になるのは、消費電力というのが同社の見解だ。

要するにMCUベースで推論を実行すると、その消費電力がすさまじいことになり、どうしてもバッテリー寿命が短くならざるを得ない。

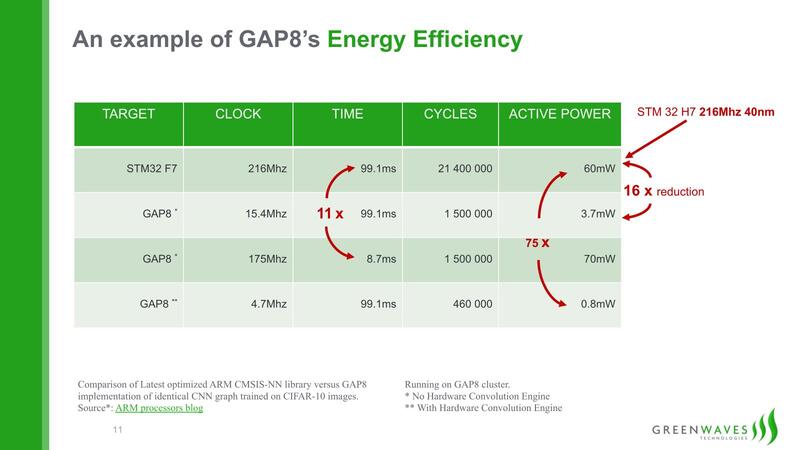

先に結論を書くと、ここでGAP8を併用することで大幅に消費電力を短縮できる、というのがGreenwavesの提案である。STM32 F7、つまりCortex-M7を216MHzでブン回すケースと比較すると、性能が同じで良ければ75倍もの消費電力削減になるし、消費電力が同等なら11倍高速化できるとしている。

RISC-Vコアが外部メモリーを参照せずに処理できる範囲に ネットワークの大きさに留める

では低消費電力をどうやって実現したのかを説明しよう。GAP8のベースになるのは、2013年にスタートしたPLUPプロジェクトだ。これはRISC-Vベースのオープンソースなハードウェアを構築するというもので、IoTからHPCまでさまざまな用途に向けたRISC-Vコアとその周辺回路、さらにはソフトウェアまで手がけるものである。

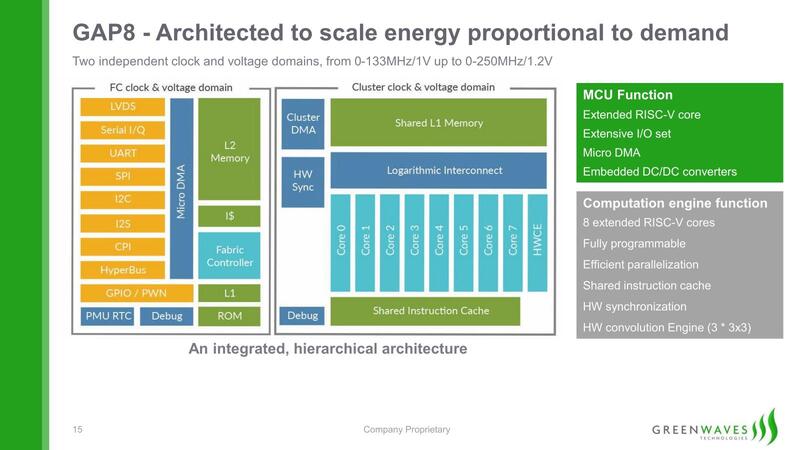

このPULPプロジェクトで提供されるCV32E40P(かつてはRIS5Yと呼ばれていた)コアを9つ統合したものである。

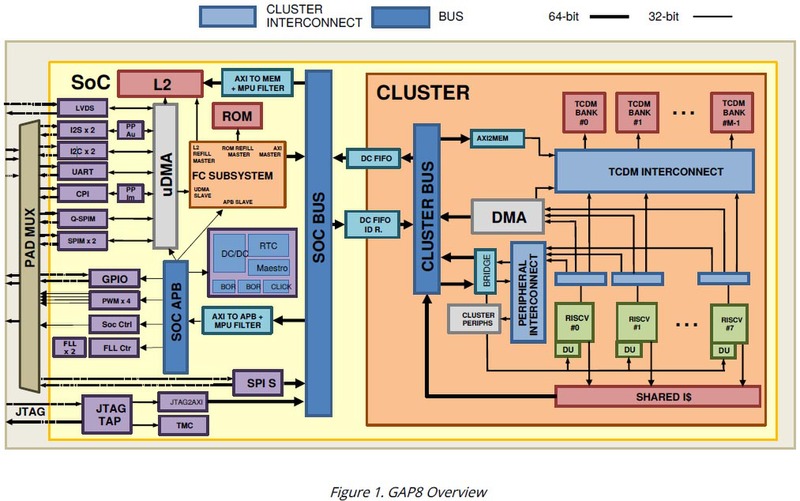

もう少し詳細な構造図が下の画像だ。個々のコアはいずれもRV32ICM(整数演算、縮小命令、乗徐算)をサポートした32bit RISC-Vコアである。CV32E40Pはパイプライン段数4段のインオーダーの構成で、効率はともかくとして絶対性能はそれほど高くない。

もちろん上の画像にもあるように、FC(Fabric Controller)側に512KBの2次キャッシュが搭載され、またクラスターの側には16KBのTCDM(Tightly-Coupled Data Memory)がファブリック経由で複数個搭載されている。

クラスター側のコアはTCDMで処理をして、このバックアップとしてFC側の2次キャッシュが利用される格好だ。命令キャッシュとしてはFC側に1KB、クラスター側に4KBが用意されている。

アプリケーションプロセッサーだとしたらこれはかなり少ない方だが、32bitのMCUコアであればこれで十分であろう。ちなみに、SoCの外にHyperBusと呼ばれるI/Fを利用して、SRAMないしフラッシュメモリーを外部に搭載することもできる。

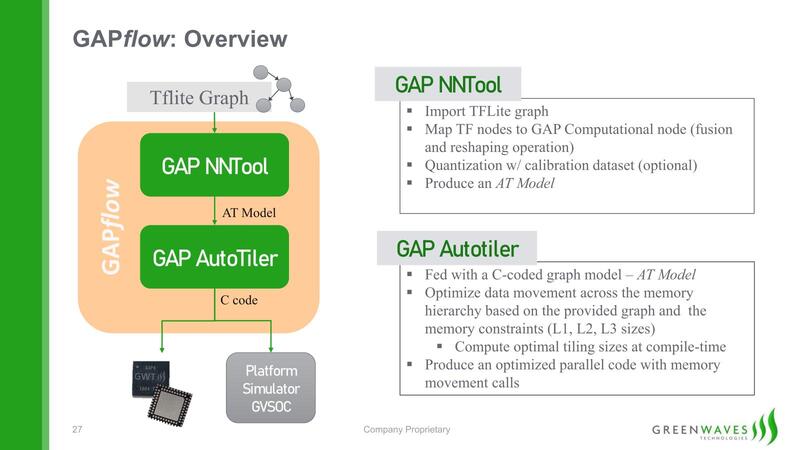

ただこれだけ見ても、なぜこれでAIの推論が高効率に行なえるのかさっぱりわからないだろう。この鍵を握るのが、GreenwavesのGAPflowというソフトウェアである。GAPflowは大きく2つのツールからなる。

最初のGAP NNToolは純粋にTensorFlow Liteのグラフを読み込み、これを続くGAP AutoTiler(AT)用に独自フォーマットに変換する。この際に量子化(Quantization)を可能なら事前に行なうことで処理負荷を減らす形だ。これそのものは珍しくない。

続くGAP AutoTilerがグラフを分割し、8つのタイル(=8つのRISC-Vコア)が外部メモリーを参照せずに処理できるようなサイズに落とし込むことで、個々のタイルはTCDMだけを参照しながら処理するようになる。

当然外部メモリーの参照が必要なければ処理は高効率に行なえるし、そもそもTensorFlow Liteを利用している時点で巨大なネットワークを動かすことはあり得ないので、メモリーが足りなくなるようなケースもない、というわけだ。

おそらく巨大なネットワークを動かそうとすると、AutoTileをかけた時点でエラーが出て、もっと小さなネットワークにするように勧告されることになるだろう。

その意味ではあくまでエンドポイントAI向けのプロセッサーコアに最適化されていると言えなくもないが、無理に巨大なネットワークを動作させるためにアクセラレーターや外部エンジンなどを突っ込み、複雑な構成になって消費電力やダイサイズが肥大化し、最終的なコストを引き上げてしまうより、RISC-Vコア+HWCE(Hardware Convolution Engine)で収まる範囲にネットワークの大きさを留めさせることで、低コストでエンドポイントAIが実行できるようにするという同社の設計方針は、わりと考えさせるものがある。

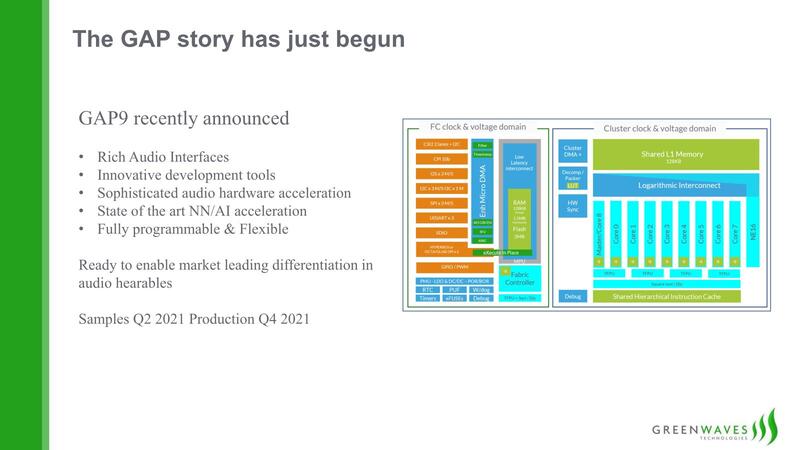

Greenwavesはこれに続き、オーディオインターフェースを搭載したGAP9をすでに発表済みである。

この画像では2021年に量産とされているが、現時点ではまだチップが完成していないようだ。ただすでに設計そのものは終わっているようで、GAP9 StoreではeFused(1回書き込みのみのFPGAのようなデバイス)を利用した評価キットが、契約ユーザー向けに出荷可能になっている。

うまくターゲットを絞れば、複雑なメカニズムや突拍子もないアーキテクチャーを使わなくてもAIプロセッサーは実現できる、という良い例かもしれない。

2022年11月9日追記

Greenwaves Technologies社よりGAP9の現状についての連絡をいただいた。それによれば2022年3月からチップを実装した評価用キットを顧客に提供中で、すでに量産ウェハーも上がってきており、これを利用したGAP9のWL-CSPチップの出荷も開始しているとのこと。すでに量産シリコンの品質検証も完了し、2023年第1四半期から出荷予定とのことである。以上、お詫びして訂正する。

※編注:次回の連載記事は、都合により14日23時に掲載予定です。通常より約半日掲載が遅くなりますことをご了承下さい。

この記事に関連するニュース

-

日本が開発したAIプロセッサーMN-Core 2 Hot Chips 2024で注目を浴びたオモシロCPU

ASCII.jp / 2024年11月18日 12時0分

-

マウザー、STMicroelectronicsの64ビット・マイクロプロセッサの取り扱いを開始

PR TIMES / 2024年11月13日 12時45分

-

Nordic Semiconductor、次世代ワイヤレスSoC「nRF54L15」「nRF54L10」「nRF54L05」をラインアップ

PR TIMES / 2024年11月12日 11時45分

-

わずか2年で完成させた韓国FuriosaAIのAIアクセラレーターRNGD Hot Chips 2024で注目を浴びたオモシロCPU

ASCII.jp / 2024年11月11日 12時0分

-

Metaが自社開発したAI推論用アクセラレーターMTIA v2 Hot Chips 2024で注目を浴びたオモシロCPU

ASCII.jp / 2024年11月4日 12時0分

ランキング

-

1“熱狂”のファミコン版『ドラクエ3』発売日を、当時の新聞各社はどう報じた?後世まで語り継ぐべき名記事も発掘

インサイド / 2024年11月24日 17時0分

-

2Minisforumが「ブラックフライデー」を開催! 新商品も最大41%お得に買える

ITmedia PC USER / 2024年11月24日 0時0分

-

3クルマを停めた位置、実はウォッチで分ります。 「コンパス」アプリの便利ワザ3選|Apple Watch Hacks

&GP / 2024年11月24日 19時0分

-

4「大企業の本気を見た」 明治のアイスにSNSで“改善点”指摘→8カ月後まさかの展開に “神対応”の理由を聞いた

ねとらぼ / 2024年11月23日 8時0分

-

5【格安スマホまとめ】povo2.0、ローソンに行くと月1GB貰える! コラボが本格スタート

ASCII.jp / 2024年11月24日 15時0分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください