インテルが10年先を見据えた最先端の半導体技術を発表 インテル CPUロードマップ

ASCII.jp / 2023年1月2日 12時0分

先週の続きで、今回もIEDM(International Electron Devices Meeting)でのインテルの発表を解説しよう。ただ先週と異なり、今週は直近のロードマップに絡む話が一切ない。そのずっと先、10年先の話である。

IEDMにおけるインテルの発表論文は以下の9本である。

このうち22.5の、巡回セールスマン問題を解くためのIn-Memory Clustered Annealerは、筆頭筆者はジョージア工科大のAnni Lu博士で、インテルは共著者として3人が名前を連ねているに留まるので、ややインテルの発表とは言い難い。さらに、先頭の27.3は先週解説した内容なので、その他の論文を簡単に紹介したい。

TDMを使ってシリコンよりも高速かつ薄いトランジスタを構築

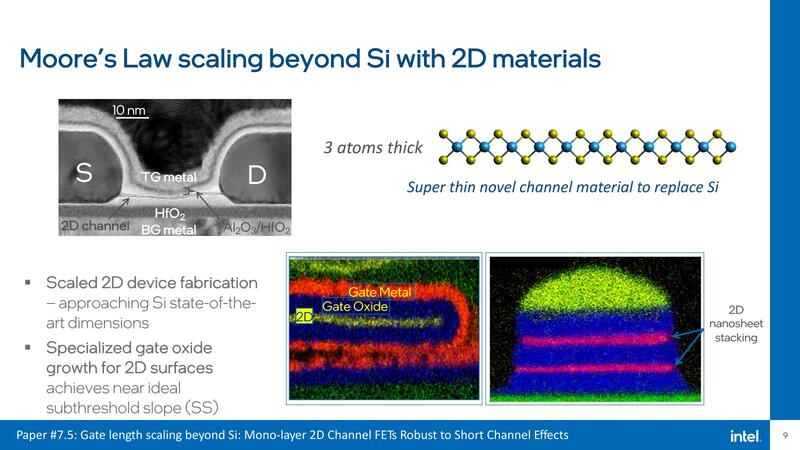

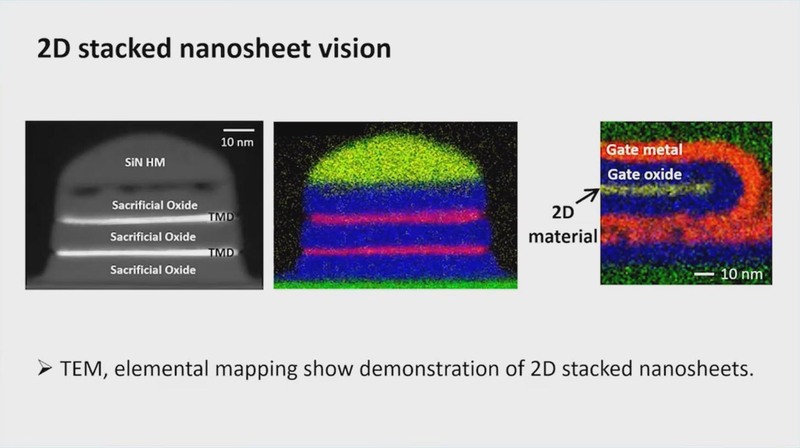

まず7.5は、TMD(Transition Metal Dichalcogenides:遷移金属ジカルコゲナイド)を使って2Dナノシートを構築、これでGAA(Gate All Around)構成のトランジスタを構築するという論文である。

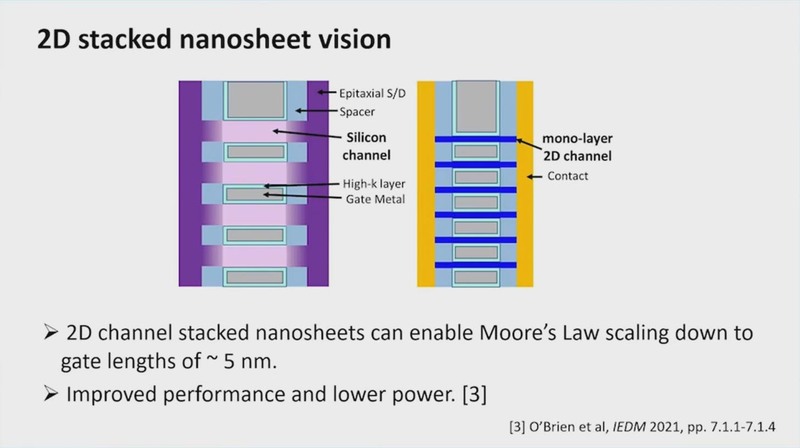

実際にこれを利用するとGAAの効率をずっと引き上げられる、というのが“Vision”である。

GAAというか積層ナノシートは、縦方向にシートを積むことで駆動電流を増やせるが、左が従来型のシリコンベースのGAAで、右は今回の積層ナノシートを利用した場合の構成になる。

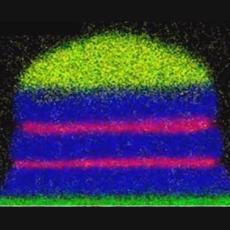

これによりゲート長を5nmあたりまで縮められるとともに、電荷の移動量を増やし、かつ低消費電力にできるというものだ。下の画像は実際にナノシートを挟むかたちでGAAをスタックした試作品の断面構造である。

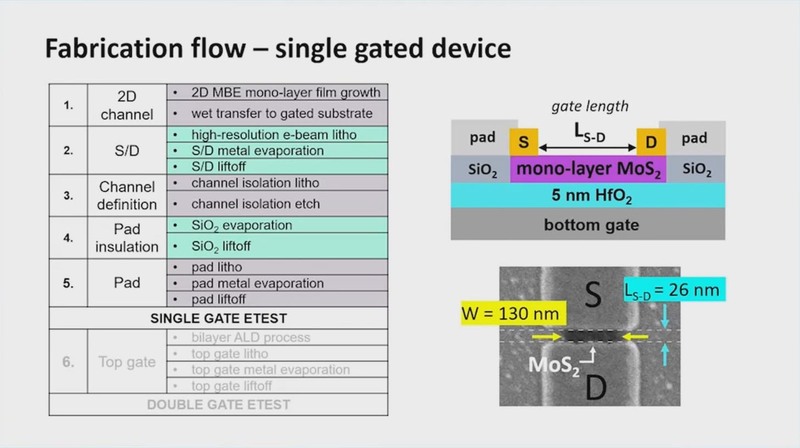

ちなみに下の画像がシングルゲートの場合の作り方である。予想どおりであるが、露光はEUV(極端紫外線)ではなく電子ビームである。

電子ビーム露光はEUVよりはるかに解像度が高いので、微細なパターン描画ができる(電界放出型で0.1nm程度、電子放出型でも1nm未満で描画可能)うえ、高価なマスクを製造する必要もないが、スループットがEUVに輪をかけて低いため、量産にはまるで適さない。

ただ研究用途にはこれで十分であり、逆に言えばこれを量産に持っていくためにはEUVでこの工程を実現するための技術開発が必要になる。今回の発表は、世代的に言えばIntel 18Aの先の先くらいの話であるが、そうした技術開発も怠らない、という内容である。

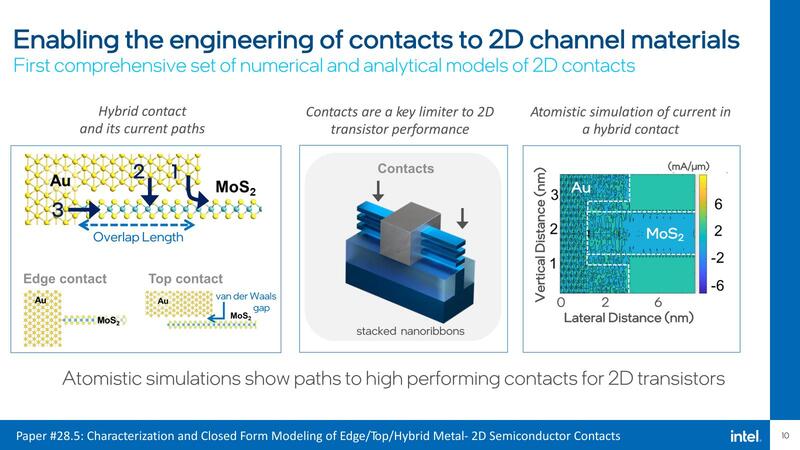

このナノシートに絡む発表が28.5である。

ナノシートはどこかで電極につなげる必要がある。このつなげ方でEdge Contact(端だけを接触する)とTop Contact(面で上から抑え込むように接触する)、それとHybrid Contact(L字型をした電極に差し込む形で、面と端の両方で接続する)の3種類の接続方法について比較した、という話である。

上の画像が、断面のシミュレーション画像で、結果から言えば金の端子に溝を掘り、そこにTMDのナノシートを差し込むような形になる。ここで色が寸法当たりの電流量になる。金の端子とTMDの所が色が濃いことで、ここで電流が大量に流れているのがわかるかと思う。

そもそもGAAで複数のトランジスタを積層する理由は駆動電流を増すためであり、したがってナノシートに大量の電流を流せるようにするためには、端子とシートの間の接続にも工夫が要るというわけだ。

もっともこの論文では、Hybrid Contactにすると電流量は増えるが、同時に抵抗も増えることが示されており、この部分をさらに改善するための研究が今後必要とまとめられているあたり、これもまだ先の先の技術ではある。

記憶容量をSRAMの数倍にできるFeRAM

ここからはプロセッサー内部に積層するメモリー素子の話である。プロセッサー内部で一番高速なメモリーはもちろんSRAMであるが、これは面積効率が悪い(なにせ1bit分で通常6トランジスタ、場合によっては8トランジスタのケースもある)。

もっと高効率で、しかも高速なメモリーが特にL2やL3に期待されているという話はご存じのとおり。これにはいくつかの候補となるデバイスがあるが、今回はここにFeRAM(強誘電体メモリー)を使う話である。

このFeRAMをLLC(要するにL3)に使えば大容量の3次キャッシュが実現できる、という話は以前からあったことであり、実際トランジスタが6~8個必要なSRAMに比べると、FeRAMは1つ溝と1個のキャパシタで構成できるので、面積あたりの記憶容量をSRAMの数倍にできる。

アクセス時間は10ns未満程度と少し遅いので、1次キャッシュやレジスターには不適当だが、LLCにはちょうど良い。ただ、Ramtronなどが実用化したFeRAM(こちらはFRAMという商標で販売されている)はプロセスが一般的ではなく、通常のCMOSプロセスとの親和性が低い。

なのでCypressや富士通はこれを外付け部品として販売しているし、MSP430というマイコンと組み合わせているTIは、がんばってこのFRAM用のプロセスでマイコン回路を実装するかたちで対処しているが、どちらもCMOSプロセスで製造するプロセッサーのLLCに使える技術ではない。

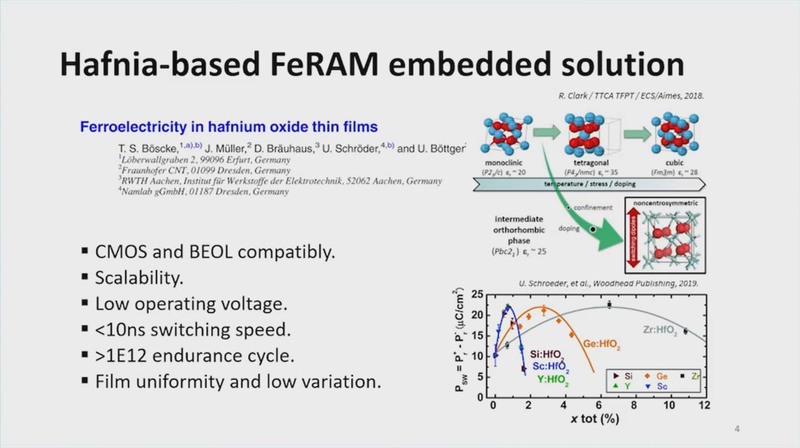

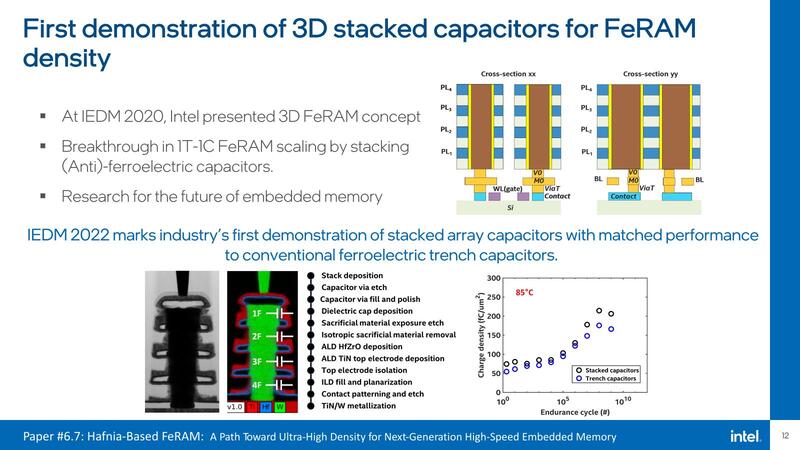

これに関しては、ハフニウム酸化物ベースの薄いフィルムをCMOSプロセスに組み合わせるという技法がすでに発表されており、こちらで実用に向けての研究が行なわれているが、今回の発表はこのFeRAMを3D積層することで、面積当たりの容量を大幅に増やすというものだ。

論文の中では試作した4bit/cellのFeRAMが、シングルセルのFeRAMと変わらない特性であることが示され、3D積層しても特性を悪化させずに容量増加を享受できることが示された。

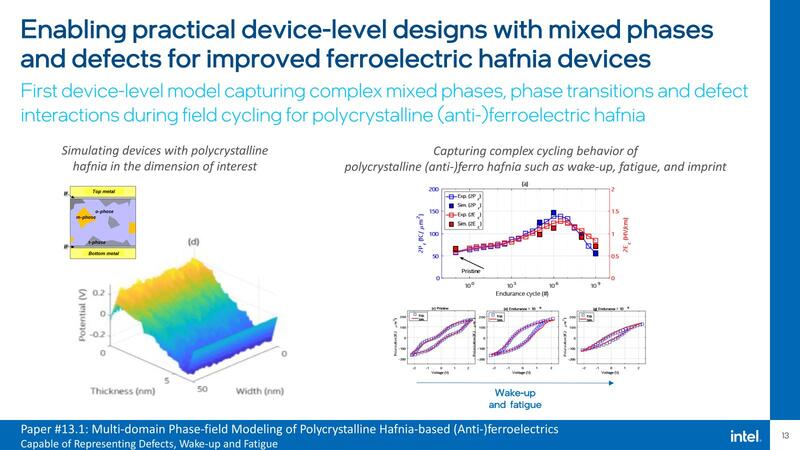

次の13.1だが、こちらはそのハフニウム酸化物の薄いフィルムそのものの話である。

こちらはこれを使ってなにかを作ったという話ではなく、そのハフニウム酸化膜のモデルの構築と、そのモデルを利用した場合の計算が実際の測定結果と良く合うことを示し、デバイスのシミュレーションのための基礎を提供できるというもので、これも実際にFeRAMをプロセッサーに組み込む際には必要となるものである。

次世代の半導体材料GaNを シリコンウェハーやCMOSと混在させる

次は、GaN-on-Siに関するものである。GaN(窒化ガリウム)は、最近では電源アダプターなどに使われ、小型なのに出力が大きく効率が良いとけっこう持てはやされているのでご存じの方も多いだろう。

もともとGaNは通常のCMOSデバイスに比べ、熱伝導性が高い(放熱効果が良い)うえに、高温でも安定して動作、電子の飽和速度(要するに電子移動の最高速)が大きく、かつ絶縁破壊電圧が高いといった特徴があり、飽和速度の高さでワイヤレスなどのRF部に、絶縁破壊電圧の高さからは電源素子にそれぞれ利用される。

ちなみに飽和速度が大きいというのはスイッチング電源の動作周波数を上げやすい=効率を高めやすい、というのが昨今ACアダプターなどでGaNが利用される理由の1つでもある。

さてそんなGaN、現状では通常のCMOSと異なるGaN専用のウェハーを利用するのが一般的だが、これでは通常のCMOSデバイスと混在させられない。GaNウェハー上にロジックを構築する試みもいくつかある。これに果敢にチャレンジしていたのが、ルネサスエレクトロニクスが買収した英Dialog Semiconductorだった。

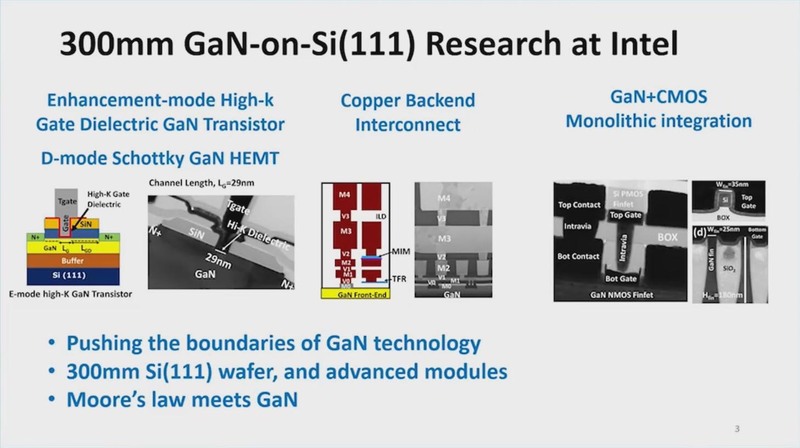

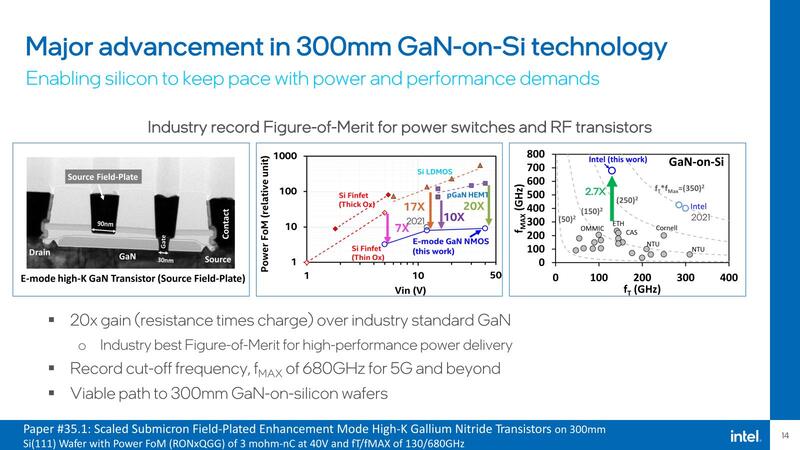

一方、通常のシリコンウェハー上にGaNを構築する研究も当然盛んである。35.1はそうした試みであり、300mmの通常のシリコンウェハー上にGaNトランジスタを構築するものだ。

用途は2つあり、1つはRF回路用。もう1つがパワーマネジメントである。これがうまくいけば、チップの中にDC-DCコンバーターを組み込むことも夢ではなく、さらにプロセッサーへの電力供給効率も引き上げられる。

またRF回路が実装できれば、例えばミリ波帯のトランシーバーをプロセッサーに組み込めることになる。現在Sub 6GHz帯まではCMOSチップに統合可能になっているが、さすがにミリ波帯は別チップとなる。

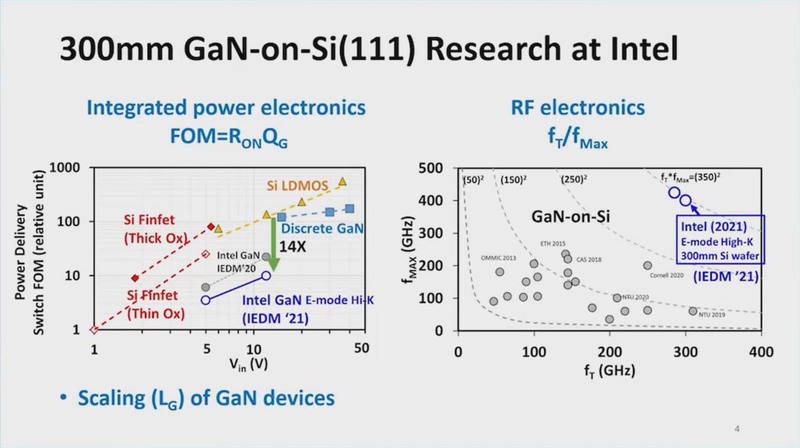

もともとインテルはGaN-on-Siはずっと研究しており、昨年もSi(111)ウェハー上にGaNトランジスタを構築したり、これとCMOSを組み合わせたりしている。

2021年にはfT(スレッショルド周波数)300GHz/fMax(カットオフ周波数)400MHzのトランジスタなどを試作して発表している。

今回のIEDMでの発表はこの延長にあるもので、電源用ではFOMを20倍改善し、40Vまでの動作が可能になったとしており、一方RF用ではfT 130GHz/fMax 680GHzというトランジスタを試作したとする。

ちなみに論文によれば、電源側のトランジスタは40V駆動で10年間の寿命があるとされており、例えばCPUに直接12Vを突っ込んで、CPU上でこれを電圧変換するなんてことも技術的には可能になったことになる。

また680GHzと言えばもう車載用レーダーですらお釣りがくるほどで、6Gワイヤレス(3GPP Release-19~21のどれかになりそうなので、時期的には2024~2027年あたり、普及は2029~2030年ごろ?)で要求されると見られる衛星通信(なにせ高度1万kmでの接続が入っている)にも十分対応できるスペックである。

あくまでもこれは研究段階で、なによりSi(111)ウェハーを使っている時点で現在の量産プロセスとは互換性がないので、まだまだ研究は必要である。

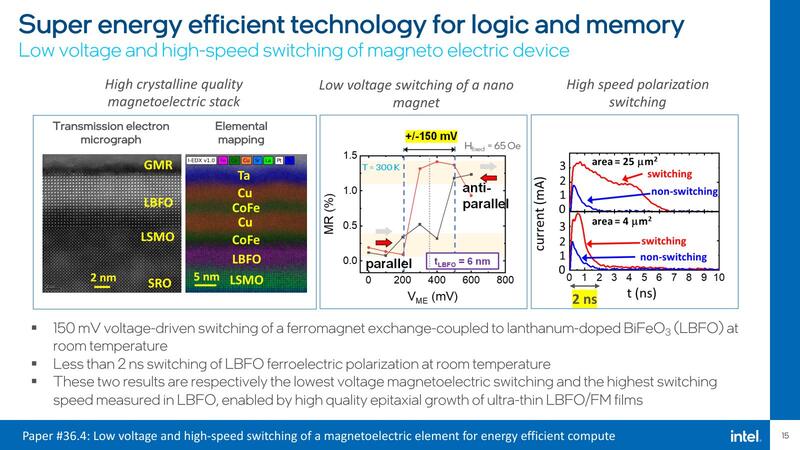

磁気ランダムアクセスメモリーMRAMを試作

36.4はMRAMに関する研究である。昨今では先に述べたFeRAMよりもむしろMRAMの方が実現の可能性が高いと見られており、実際第1世代のMRAM(磁界書込式)に続き第2世代のSTT-MRAM(Spin Transfer Torque MRAM:スピン移行トルク式)が主流になり、最近は第3世代としてこのSTT-MRAMを面記憶ではなく垂直記憶として容量密度を上げる方式が研究されている。

その一方でArmとSamsungが共同で、第2世代MRAMに対応したMRAMコンパイラの提供を2018年に始める(要するにSamsung Foundaryを利用する顧客は、自身の製品にMRAMを搭載できる)など、一部実用化も始まっている。

インテルは今回、厚み6nmのランタンを添加したビスマス-鉄系マルチフェロイック薄膜(LBFO)を利用して、アクセス速度2nmのMRAMを試作し、その結果を発表している。

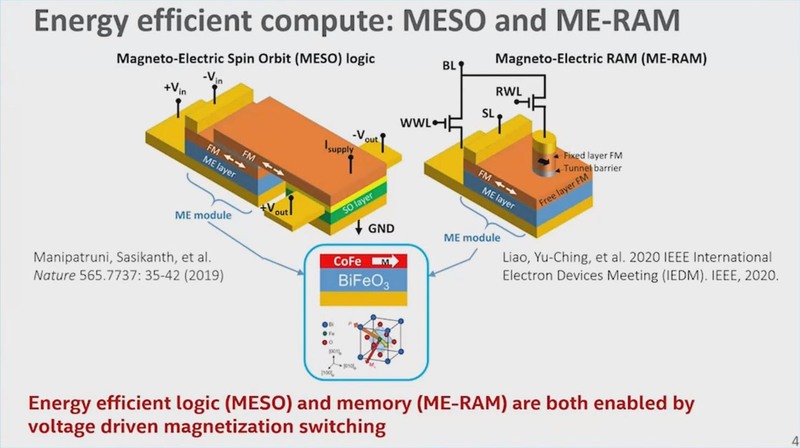

インテルはこのメモリーをME-RAM(MagnetoElectric RAM)としているが、特徴は結構高速なうえに省電力なことであり、単にメモリーだけでなくこれをロジック(MESO:MagnetoElectric Spin-Orbit)デバイスとして使うことも可能であり、非常に省電力なデバイスが構築できる、とする。

ただMESOにしてもME-RAMにしても、CMOSプロセスとの親和性は良い反面、面積効率はCMOSデバイスや前述のFeRAMよりは明らかに悪い。なのでこれは先端プロセッサーというよりもEdge/Endpoint向けという感じで、マイコンなどの構築には良さそうだ。

IFSで将来提供するオプションの1つになるかもしれないという感じではあるが、インテルのプロセッサーにこれが入るという感じにはならなそうである。

発表としてはあと8.4があるが、こちらはQuantum Computing向けの話で、Si/SiGeで構築されるキュービットアレイの欠陥が性能におよぼす影響をどう緩和するか、という話なので説明は割愛する。

以上のようにインテルは、10年先を目指した研究も積極的に行なっている、ということを示した内容であった。

この記事に関連するニュース

-

日本が開発したAIプロセッサーMN-Core 2 Hot Chips 2024で注目を浴びたオモシロCPU

ASCII.jp / 2024年11月18日 12時0分

-

2024年のエリアイメージセンサ市場は前年比12%増の2兆7670億円、富士キメラ予測

マイナビニュース / 2024年11月14日 18時15分

-

米商務省、CHIPSプラス法に基づきコーニングとパワーエックスに助成(米国)

ジェトロ・ビジネス短信 / 2024年11月11日 11時0分

-

Metaが自社開発したAI推論用アクセラレーターMTIA v2 Hot Chips 2024で注目を浴びたオモシロCPU

ASCII.jp / 2024年11月4日 12時0分

-

米商務省、国立半導体技術センター初の旗艦施設、EUVアクセラレーターをNY州に設立へ(米国)

ジェトロ・ビジネス短信 / 2024年11月1日 11時35分

ランキング

-

1クレジットカードを少額で不正利用されていない? 巧妙な新手口を解説

ITmedia エンタープライズ / 2024年11月26日 7時15分

-

2リンク付き投稿は拡散力減?イーロン氏明かすXルール 「告知投稿めっちゃ影響」不満も続々

J-CASTニュース / 2024年11月26日 17時11分

-

3『ドラクエ3』大魔王ゾーマ様、配信者になる―自己紹介では「嫌いなもの:ひかりのたま」とポロリ、「“ほりい”とかいう人間も泣き叫んでた」

インサイド / 2024年11月26日 13時10分

-

4オリエンタルランド、東京ディズニーリゾート販売の“3800円のマイボトル”回収 対象個数は4240個…… 「ご迷惑とご心配」

ねとらぼ / 2024年11月26日 17時12分

-

5アップル「iOS 19」SiriがChatGPTみたいになる?

ASCII.jp / 2024年11月26日 20時0分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください