自動運転に必要な車載チップを開発するフランスのVSORA AIプロセッサーの昨今

ASCII.jp / 2023年1月30日 12時0分

今回は、フランスのVSORAが提供するTyrプロセッサーを取り上げたい。創業は2015年とやや古め。創業者はJulien Schmitt氏とTrung Dung Nguyen氏の2人だが、2人ともフランスのDiBcomという、TV向けのデジタルチップセットを製造するファブレスメーカーに勤務していた。

DiBcomは2011年にParrotというドローンメーカーに買収され、両氏ともそのままParrotに移籍している。最終的なポジションはSchmitt氏がDSP&ASIC group manager、Nguyen氏がSenior Signal Processing Engineerだったようだ。

もともとDiBcomは、高性能・低消費電力なDSPを核としており、これを利用して欧州で利用されているさまざまなデジタルTVの標準規格に向けたチップセットを提供していた。一方のParrotはドローンの製造にあたり、やはり高性能かつ低消費電力なプロセッサー技術を必要としており、なのでDiBcomの保有していた製品ポートフォリオというよりも核となるDSP技術を買収した、というのが正しいところだろう。

Schmitt氏とNguyen氏は2015年にParrotを辞してVSORAを設立する。ちなみにCEOには、DiBcomの創業者兼CTOであり、ParrotでもDigital Tuner部門のCTOだったKhaled Maalej氏が就いているが、なぜかMaalej氏はVSORAの創業者ではないらしい。

5G NRで通信可能な信号処理プロセッサー

そんなVSORAであるが、当初目指していたのはAIではなく信号処理の方向だった。創業から3年後の2018年9月、VSORAはLETI(フランス電子情報技術研究所)と共同で、3GPP Release 15の物理層をマルチコアDSPで実装したことを発表している。

この時VSORAはMPU-801というSingle Core DSP Processorと、これを4つ統合したMPU-3201というMulti Core DSP Processorの2つをラインナップしている。

VSORAは当時はまだ製品売りというよりもIP売りの会社であり、LETIとの共同発表もLETIのニーズに合わせてMPU-3201をカスタマイズしたものを提供し、これを実装(どうも発表を読んでいるとシリコンを製造したというよりはFPGAに実装したようだ)上で5G NRの物理層のアルゴリズムを搭載、これを利用した5G NRの通信実験に成功したようだ。

ちなみにこのMPU-801/3201の内部構造はさっぱり不明なままである。説明によれば以下の特徴を持っているそうだ。

- High processing-power eliminates the need for specific coprocessors and ensures greater flexibility (高い処理性能により、特定のアクセラレーター類を必要とせず、高い柔軟性を確保する)

- Customizable DSP-processing power (DSPの処理能力をカスタマイズ可能)

- Customizable Floating-point Arithmetic Logical Units (FPUもカスタマイズ可能)

- Efficient low power instructions (効率の高い低消費電力な命令セット)

- High level description of algorithms (アルゴリズムを高レベル言語で記述可能)

- Mixing signal processing and embedded software (信号処理を演算命令に混在可能)

- One code for data-link layer & physical layer (データリンク層と物理層を1つのコードで記述可能)

- Separates automatically codes running on the DSP and on the CPU (DSP上で動作するコードとCPU上で動作するコートを自動的に分離)

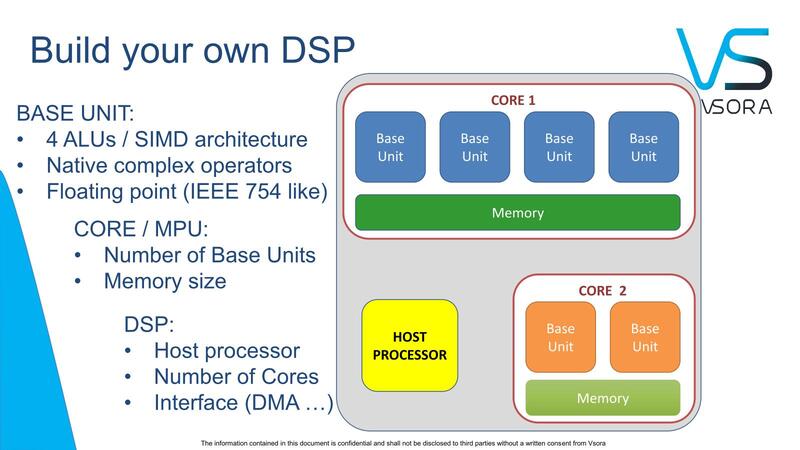

それをどうやって実現したのか? の説明は一切ない。もう少し詳細な説明が下の画像だが、これでも中身がさっぱりわからない。カスタマイズの自由度が高いことはわかるのだが、それだけである。とは言え、5G NRの基地局の処理ができる程度の性能がある(これもその基地局の規模次第なので、性能を一概に議論するのは難しいのだが)ことしかわからない。

自動運転をターゲットとしたAIプロセッサーを開発

VSORAは2018年あたりまではそれこそ通信分野などに向けた信号処理をメインとしていたわけだが、2019年あたりから“A New DSP Approach to Accelerate 5G and AI Design Development”と、ターゲットとする市場に“AI”の文字が入るようになり、2020年になると“AI & Signal Processing/ADAS/Digital Communication”とターゲットにADASが入るようになり、2021年にはついにDigital Communicationの文字が消え、代わりに自動運転をターゲットとしたAIプロセッサーであるTyrを前面に押し出すようになった。

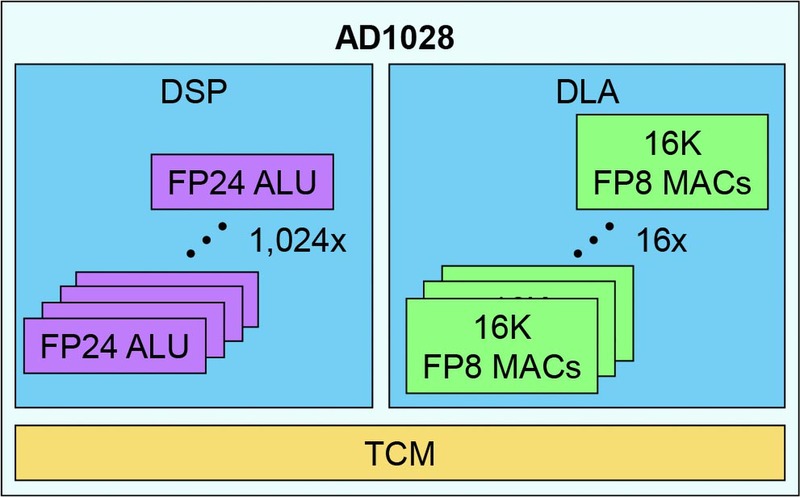

その2020年、AI向けとしてVSORAが発表したのがAD1028である。AD1028は、FP24(16bit仮数+7bit指数+符号)のALUを1024個並べたDSP部と、FP8のMAC演算を16K個同時に演算可能なMACアレイを16個(つまり1サイクルあたり256K個の演算が可能)搭載したDLA部、それにTCM(Tightly Coupled Memory)を組み合わせた構成である。

ちなみにAD1028はVSORAではミッドレンジ向けという扱いであり、ハイエンドは2048 ALUのDSPと512K MACを搭載したDLAから構成されるAD2056という製品が予定されていた。

もっともこのAD1028、2020年の時点で7nmプロセス向けにテープアウトしており、2GHz動作で1PFlopsの演算性能(DLA部:DSP部は4TFlops)を持ち、消費電力は35W未満。ダイサイズはTCMを除いて35mm2とされていた。実際にはこれだけの演算性能を持たせるとなると、相当なサイズのメモリーが必要になる。VSORAの推奨によれば、AD1028の構成であればおよそ105MBのTCMが必要、という計算だそうである。

ちなみにラフな計算であるが、同じく7nmで製造されるRyzen 5000シリーズに利用されていたZen 3コアのL3(32MB)のエリアサイズがおおむね36mm2なので、同じ形で実装すると105MBではおよそ118mm2ほど。それとAD1028自身の35mm2とあわせてダイサイズは153mm2とけっこう大きくなる。

ただSRAMなので消費電力はそれほど大きくはならない。VSORAはこのAD1028で30TOPS/Wを実現できるとしているが、厳密に計算すれば29TOPS/W弱といったあたり。30TOPS/Wも誇大表現とは言い切れない程度、といったところか。たぶんSRAMも込みにして40W程度、実質25TOPS/Wあたりが現実的な線だろう。

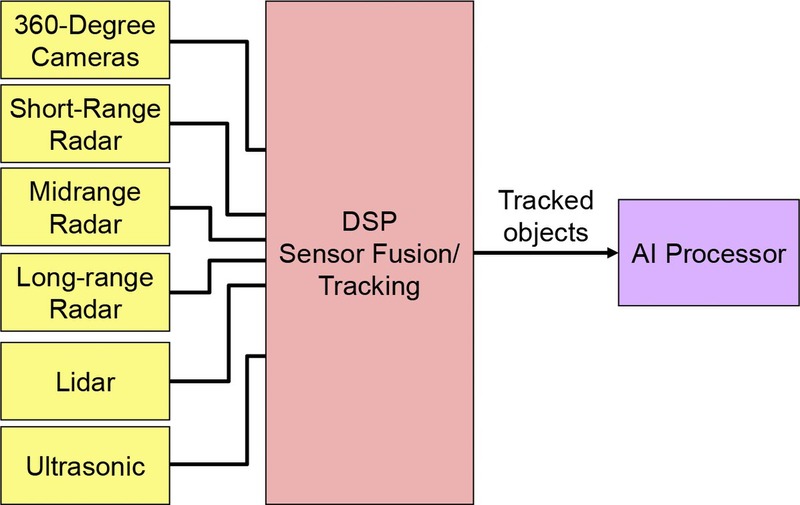

なぜDSPとTLAの2ブロックが必要か? という理由が下の画像だ。VSORAはLevel 4の自動運転をターゲットに置いており、ということはさまざまなセンサー(カメラや長/中/短距離レーダー、LiDAR、超音波センサーなど)を使ってまず周囲や進行方向の状況を取得、これをベースに自動運転の判断を行なう必要がある。そこでまずDSP部で、こうしたさまざまなセンサー情報を処理し、この結果をDLA部を利用して処理する、という構成を狙ったわけだ。

ちなみにVSORAによればDSP部は複雑な処理も可能な汎用のALUをベースにした構成だそうだが、DLA部はもう完全にMAC演算に特化した構成のようで(アクティベーション用の関数があるかどうかも不明)、MACを制御するコントローラーにあたるものがなにかしら搭載されていないとやや処理的に厳しい(これを全部外部のホストから行なっていたら、そこがボトルネックになる)気がするのだが、そのあたりの詳細は一切公開されていない。

製品ラインナップは3種類

このAD1028なりAD2056なりはIPの形で提供する予定であり、自身でチップを提供する計画は2020年の時点では存在していなかったようだ。ただそこから2年経った2022年1月、VSORAはTyrチップの発売を発表する。

ラインナップとしてはローエンドのTyr 1とミッドレンジのTyr 2、ハイエンドのTyr 3の3つが現在あがっている。

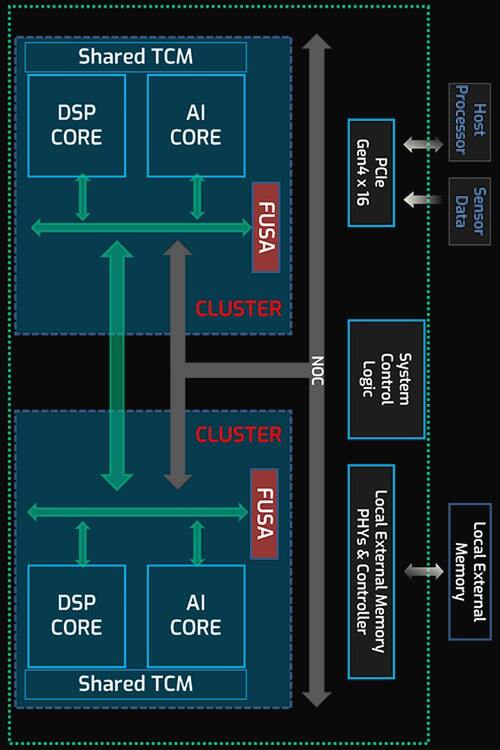

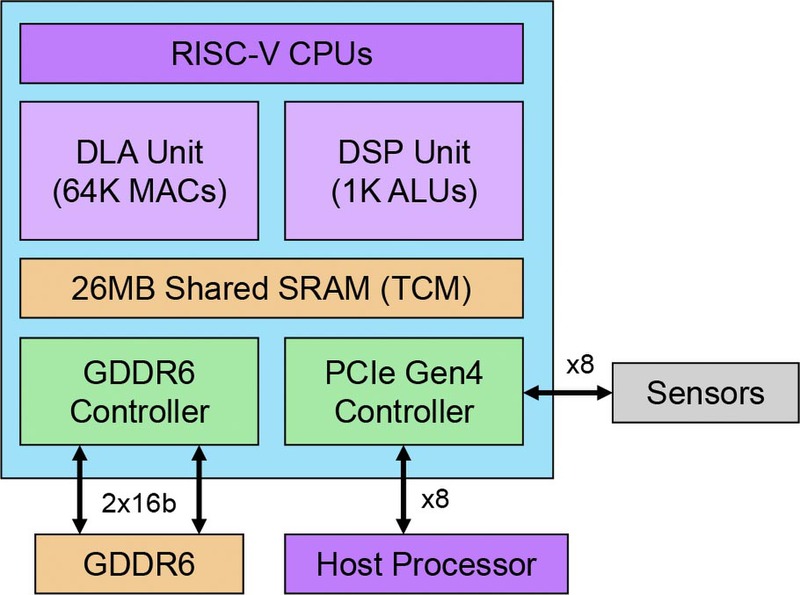

これは内部構成の違いであるが、TyrではAD1028の流れを汲むClusterという新しい処理ブロックが定義された。このClusterにはDSPコアとAIコア(前ページ最初の画像でいうことろのDLA)が搭載されており、Clusterあたりの性能はDSPコアが512 ALU、AIコアが32K MACである。これと13MBの共有TCM、それとFUSA(FUnctional SAfety:機能安全)ユニットから構成される。

TyrプロセッサーはこのClusterに加えて、外部メモリーコントローラーやPCIeコントローラー、制御用プロセッサーが搭載される格好だ。

ラインナップは下表のとおりで、あとはどの程度の演算性能が必要かで選べばいい。

ちなみにFUSAユニットというのは、障害対策のユニットである。自動車の中でも、特に運転に直接関係する部分では機能安全という考え方が取り入れられており、ISO 26262と呼ばれる規格の中でASIL-A~Dまで4レベルの安全水準が定められており、機能や用途に応じてどの水準を満たすべきかが定義されている。

問題はこのうちASIL-Bくらいまでであれば、自動車向けのプロセスと呼ばれるものを使えば故障率を要求水準内に抑えられるが、一番厳しいASIL-Dの場合はこれを満たすのは現状不可能である。

ただし逃げ道があって、複数のユニットを同時に動作させ、片方がおかしくなったらそちらを切り離して正常なユニットで処理を継続する、という実装にすることで要求水準を満たせる。ただしその場合以下の処理を行なう機構が必要である。

- 複数のユニットを協調して動作する

- 故障/障害を検出する

- 故障/障害がどのユニットで発生したかを判断する

- 故障/障害を発生したユニットを切り離す

FUSAはこれを担うものであると考えればいい。DSP部のALUの数とDLA部のMACユニットの数の比率がAD1028と異なるのだが、これはおそらく顧客からのニーズのフィードバックと考えられる。要するにセンサーからの取り込みの処理性能をもっと引き上げる必要があった、というわけだ。

Tyr 1~3とラインナップが3つあるのは、そもそもVSORAがL2~L5までの自動運転とターゲットを広げたためで、Tyr 1はL2の、例えばレーンアシストとか道路標識の認識と通知といった簡単な用途向け。一方Tyr 3はL5の自動運転に向けたもの。その中間がTyr 2と思われる。

上の画像はTyr 1の内部構造で、制御用プロセッサーにはRISC-Vを、外部メモリーは32bit幅のGDDR6を使うとしており、センサーやホストとの接続はPCIe x8構成となっている。ちなみに消費電力はTyr 1が13W未満、Tyr 3が50W未満とされており、Tyr 2はおそらく25Wかそのあたりと想像される。

競合製品(例えばNVIDIAのOrin)と比べると、センサー用のフロントエンド(カメラ用のISPなど)がないなど、制御プロセッサーが本当に最小限の能力なので、Tyrの上位に強力な判断用のプロセッサーが必要など、いろいろ欠けているものもあるが、その一方で本当に最小限必要な要素をまとめているので、むしろカスタマイズがしやすいという見方もできる。

VSORAによれば2022年第4四半期中にサンプル出荷を開始し、量産車には2024年に搭載される見込みとしているが、さてどこまで市場に食い込むことができるのだろうか?

この記事に関連するニュース

-

Lunar LakeではPコアのハイパースレッディングを廃止 インテル CPUロードマップ

ASCII.jp / 2024年7月1日 18時0分

-

「Lunar Lake」Deep Diveレポート - 【Part 1】P-Core&E-CoreとPackageについて

マイナビニュース / 2024年6月29日 12時31分

-

Intel Tech Talkで見えたLunar Lakeにおける低消費電力と高性能の両立へのこだわり

マイナビニュース / 2024年6月27日 6時45分

-

Xeon 6にLunar Lake 全方位で競合をリードする、信用のブランドがIntelだ――基調講演でパット・ゲルシンガーCEOが語ったこと

ITmedia PC USER / 2024年6月5日 17時5分

-

次世代CPU「Lunar Lake」でIntelが目指す“AI PC”とは? 驚くべき進化点と見える弱点、その克服法

ITmedia PC USER / 2024年6月4日 12時5分

ランキング

-

1迷惑メール転送すると送信元が行政処分される? Xでアドレス拡散、宛先の「迷惑メール相談センター」が明かす実情

J-CASTニュース / 2024年7月2日 11時0分

-

2新紙幣「一万円札と千円札の1の字が違う」SNSに違和感覚えるという声も…… 「1」のデザインが違う理由は?

ねとらぼ / 2024年7月3日 18時15分

-

3老後の趣味で気軽に“塗り絵”を始めて1年後…… めきめき上達した70代女性の美麗な水彩画に「本当にすごい…」「感動です」

ねとらぼ / 2024年6月29日 22時0分

-

4藤本美貴&庄司智春、真っ昼間に変装ゼロで“腕絡め”デート 大勢の注目浴びるも“モザイク9割”の結果で「笑った」

ねとらぼ / 2024年7月2日 15時1分

-

5中小企業の社内Wi-Fi接続、約半数が「つながりにくさ」を実感‐対処法は?

マイナビニュース / 2024年7月3日 11時50分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください