推論をわずか20mWで実行するエッジAIチップ「ERGO」 AIプロセッサーの昨今

ASCII.jp / 2023年3月27日 12時0分

Perceiveという会社は2018年にアメリカで創業した。正確に書けば、親会社であるXperi(旧Tessera)から2018年に独立したというべきだろう。ただし当初からステルスモードの形で創業されており、同社が一般にその名前を示したのは2020年に最初の製品であるERGOチップを発表したタイミングである。

まずは親会社である旧Tesseraだが、こちらは1990年にIBMのワトソンリサーチセンターでAdvanced Packaging部門のシニアマネージャーを務めていたThomas DiStefano博士が立ち上げた企業である。もっともDiStefano博士自身はVP of Marketingという立場で、社長兼CEOにはJohn W. Smith氏が就いている。

このTesseraは半導体のパッケージ技術をライセンス提供するという会社で、1997年頃の顧客リストを見るとAnam/Amkor、Flexera、日立、インテル、三井ハイテック、Read-Rite、新光電気工業、TI、3Mといった企業が並んでいる。2010年にはμBGAの商用化を実現したとして、SEMI(もともとはSemiconductor Equipment and Materials Instituteの略だが、すでにSEMIが正式名称になっている) Award North Americaを受賞するなど、半導体パッケージ技術に特化した会社であった。

この方向性が変わってきたのは、1999年9月にCEOがBruce McWilliams氏に代わって以降に思える。もちろん半導体パッケージ技術をないがしろにしたわけではないが、ここからさまざまなテクノロジーを保有している会社の買収を始める。

2005年にはウェハーレベルのイメージセンサーパッケージ技術を持つShellcaseの資産を買収、2006年にはスマートフォンなどのイメージング技術を持つDigitalOptics Corporationを、2007年にはカメラの自動フォーカス/ズーム技術を持つイスラエルのEyesquadを、2016年にはマルチカメラソリューションを持つPelican ImagingとマルチチャネルオーディオのDTSをそれぞれ買収。2020年にはTiVoと合併もしている。

もちろんその合間に、2015年には2.5D/3Dボンディング技術を持つZiptronixを買収したりもしているのだが、そうした半導体パッケージ事業は2011年に立ち上げた完全子会社のInvensas Corporationに集約し、自身は複数のテクノロジーを保有する企業になった。

社名を2017年Xperiに変更したのはそうした戦略の変更もあってのことかと思う。現在はdtsやTiVo以外にHD RadioやIMAX Enhancedといったテクノロジーをライセンスする会社になっている。

20mWの消費電力で推論処理を行なう ERGOチップ

さて話をPerceiveに移す。Perceiveを立ち上げたのは、現在もCEOを務めるSteve Teig氏である。もともとはICの配置配線の技術を持つTangent Systemsの創業者兼CTOで、同社がCadenceに買収されたため、今度はBioCADという分子シミュレーションCADの会社を立ち上げ、それを売却後に今度はCombiChemという創薬開発システムの会社を創業する。

新規株式上場後に離脱し、再び半導体の世界に戻りSimplex SolutionsというEDAの会社のCTOを務めるものの、またもやCadenceに買収。しばらくCadenceでCTO兼Chief Scientistを務めた後でTabulaというFPGAの会社を立ち上げる。

残念ながらTabulaは2015年に破産したが、その後Teig氏はXperiにCTOとして参加する。このXperiの時代、Teig氏はXperiが持っていた技術と機械学習を組み合わせることを検討していたそうだ。

具体的に言えば、オーディオやビデオ向けのソフトウェアに機械学習を組み合わせるという話で、その中には例えば映像向けの赤目補正や手振れ補正なども含まれていたらしい。

これを実装するにあたり、ソフトウェアだけでこれを行なうのではなく、適切なエッジ向けの機械学習用ハードウェアを開発すべきという結論に達し、取締役会に対して「20mWの消費電力で、必要な推論処理を行なえるチップを開発すべきで、そのためには新しく企業を興すべき」という提案をする。これが通った結果としてPerceiveが立ち上げられ、そこで最初の製品であるERGOチップが2020年に完成した形だ。

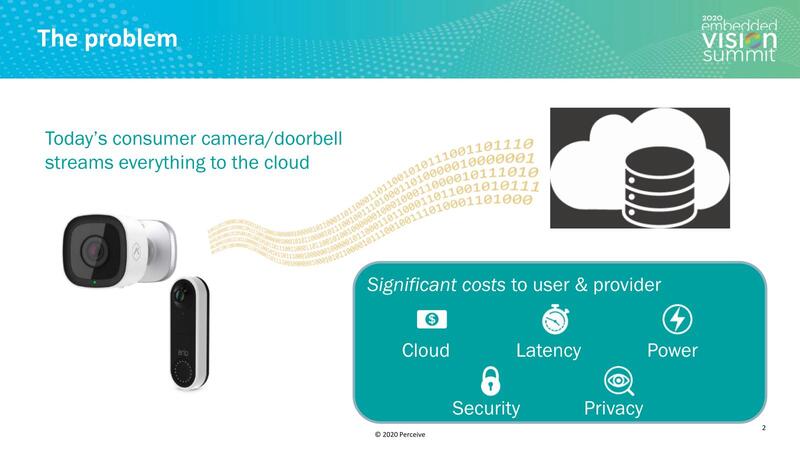

2020年のEmbedded Vision Summitで公開されたスライドによれば、例えばドアベル/ドアカメラの映像をそのままクラウドで処理するのはさまざまな面で無理がある。

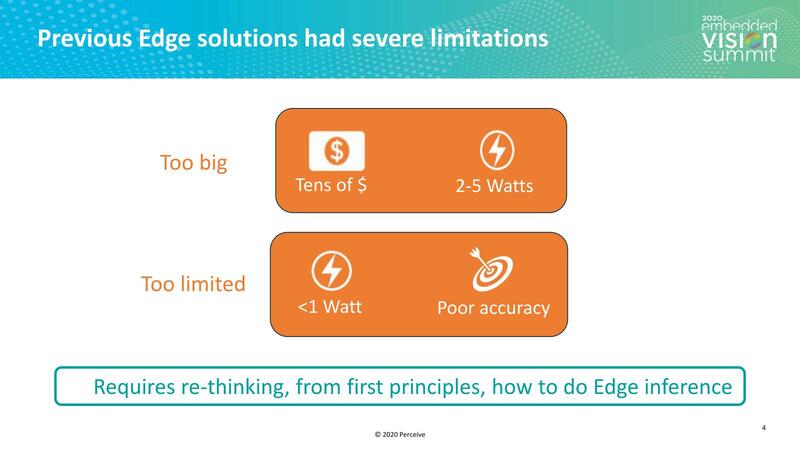

一方で2020年の時点では、エッジAIで十分な精度がある構成というのは、それこそNVIDIAのGPUカードを装着したPCクラスになり、コストと消費電力の両面で機器に収めるのは無理がある。一方でエッジというよりはエンドポイント向けでは、性能はともかく精度が足りないという欠点があるとする。

ちなみにこの精度に関しては、“Accuracy: Beware of Red Herrings and Black Swans,”(精度:誤解と想定外に注意)という、Teig氏自身の講演がやはりEmbedded Vision Summitで行なわれている。この中でTeig氏は精度だけを追求するのは難しいとして、新たにsurpriseというメトリックを導入することで、大外れしにくくなるとしているがこれは余談である。

GPUでいうところの4TOPS相当の性能

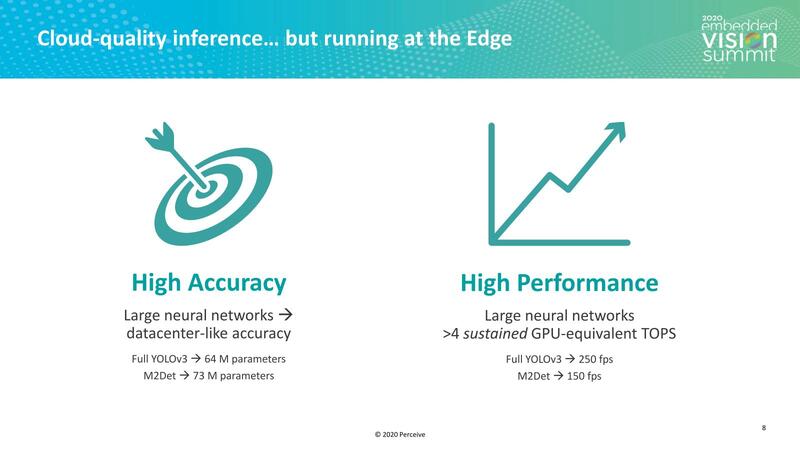

Perceiveの最初のチップであるERGOは、エッジというよりもエンドポイントに利用できるサイズと消費電力でありながら、高い性能と精度を目指したとするが、この精度と性能に関しては明確な指針が出ている。

まず精度については、現状データの持ち方(INT1/2/4/8/FP8/BF16/....)よりもネットワークの規模や、そこで利用されるパラメーター数の方が支配的である。

したがって、フルセットのネットワークが稼働する(≒そのネットワークで利用されるパラメーターをオンチップで保持できる)ことが目標となる。また性能に関しては「GPUでいうところの4TOPS相当」という数字が示された。具体的にはYOLOv3で250fps、M2Detで150fpsとされる。

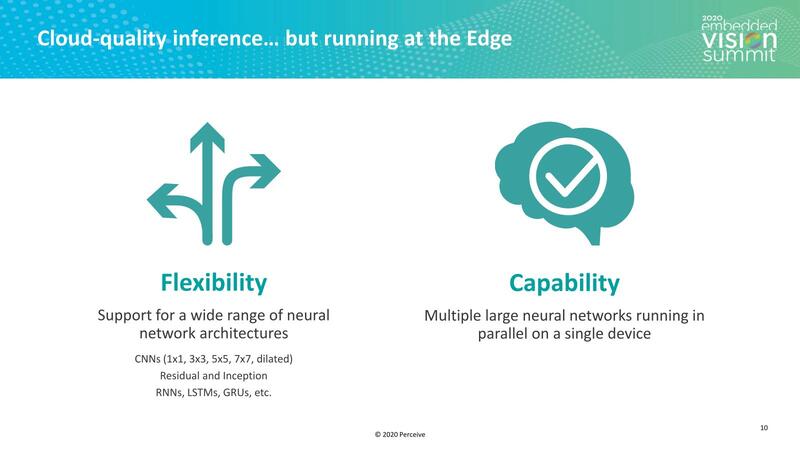

加えて、さまざまなネットワークに対応できる柔軟性と、複数のネットワークを同時に稼働できる容量が必要、という欲張りぶりである。

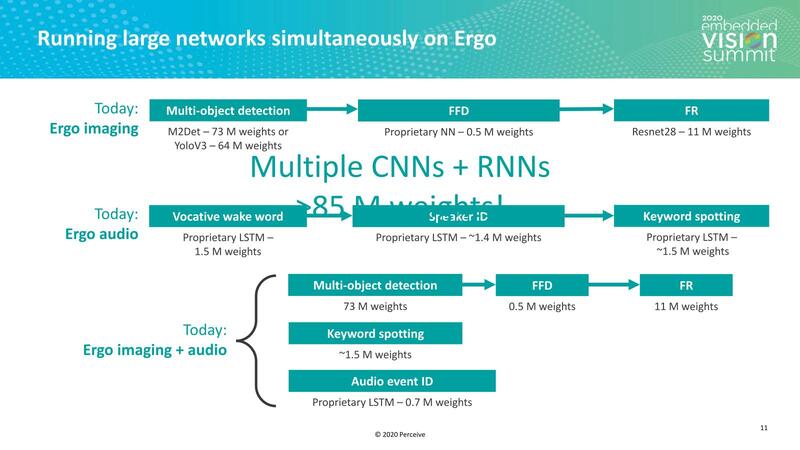

この複数のネットワークに関しては実際に、イメージングだけ、オーディオだけ、イメージングとオーディオという3種類の実装例が示された。

こうした複数のネットワークを同時に動かすとなると、処理性能だけでなくパラメーターを搭載するためのメモリーもそれなりに必要になってくる(さもないとパラメーターのロードがボトルネックになる)。

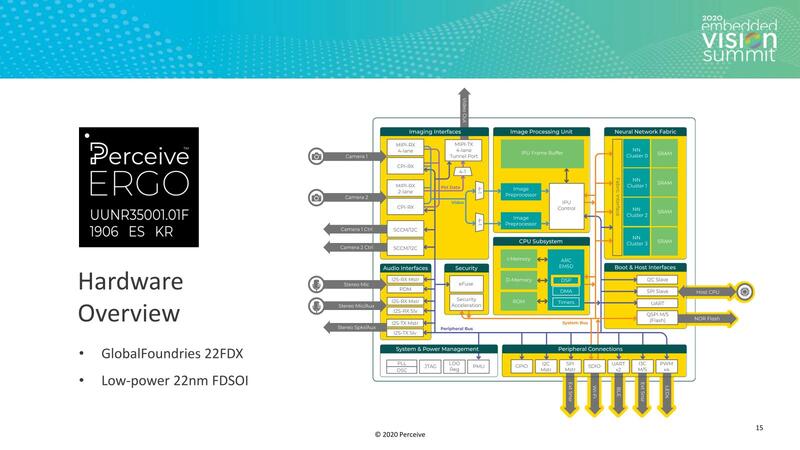

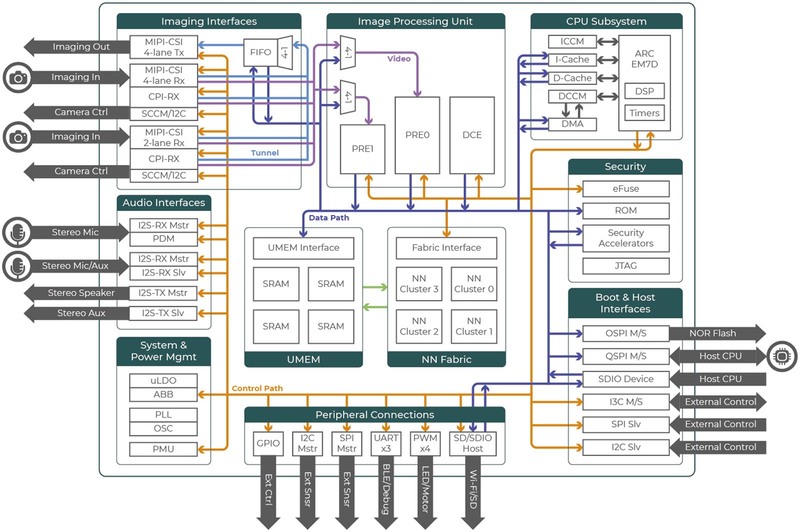

さて、ここまで説明してきておいてなんだが、Perceiveはこれを実現したERGOチップの詳細をまったく明らかにしていない。ERGOチップの内部構造が下の画像で、イメージングI/FとオーディオI/F、IPUとCPUサブシステム、それにNNファブリックがあるが、そのNNファブリックがどんな構成でどのくらいのSRAMが搭載されているか、などは一切未公開なままである。

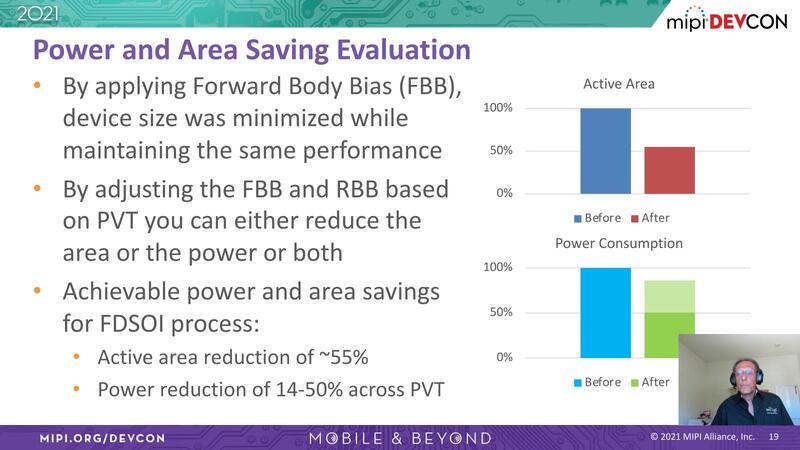

ただ省電力を実現できた理由の1つとして、Globalfoundriesの22FDXプロセスを利用し、さらにFBB(Forward Body Bias)とRBB(Reverse Body Bias)の両方を利用したとしている。

説明によれば、高速動作が必要な部分にFBBを利用することで、アクティブ部分のエリアサイズを最大55%削減、その一方でその他の部分にはRBBを利用してトータルで14~50%の省電力化を図った、としている。

ちなみにチップの外形寸法は7×7mmとされるが、全体の3分の2以上はNNクラスターとSRAMが占めるという説明があった。Globalfoundriesが2017年のVLSI Symposiumで発表した数字によれば、22FDXを利用した場合のSRAM Cellの面積はHD(High Density:高密度)で0.110μm2、HC(High Current:高速)で0.124μm2とされる。

今回の場合はHDを利用しているだろうから、0.110μm2ということになる。パッケージが7×7mmだからといってダイサイズは当然もっと小さいはずだが、具体的な数字は示されていない。

ただ仮に5×5mmとして、そのうち3分の2がNNクラスター+SRAMで、そのSRAMの面積が4分の3くらいだと仮定すると、SRAMのサイズは12~13mm2程度。ざっと計算しても全部で13.5MB程度の容量が精一杯に思われるのだが、これで合計85M以上のパラメーターをどう保持しているのか、はけっこう謎である。

もちろんパラメーターは疎の部分があるので、うまくSparsityを管理して、さらにパラメーター圧縮などを行なっているのかもしれないが。

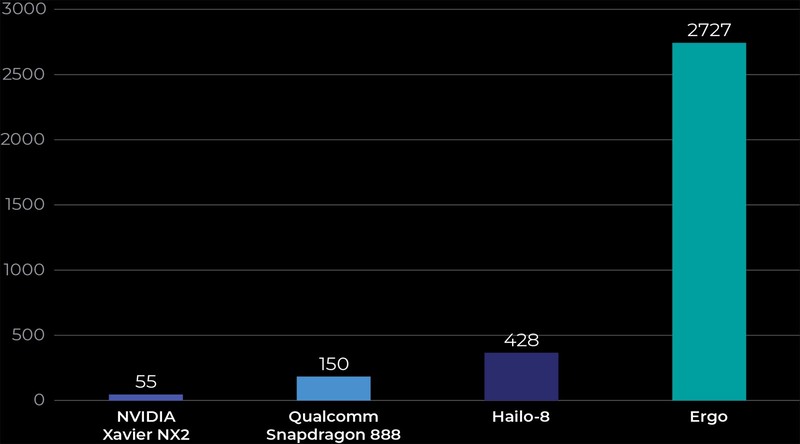

このERGOチップはすでに出荷を開始しており、評価ボードも出荷されている。製品の方は定格(250MHz動作)とLow Power(250MHz動作ながらVDDを0.65Vに下げたもの)、High Performance(310MHz動作)の3つが用意されており、性能/消費電力比は圧倒的に高いとしている。

エンドポイント向けの有力なAIプロセッサー ERGO 2が今年1月に完成

実はPerceive、今年1月に後継のERGO 2チップも完成させている。

今年のCESではバックステージで動作デモも行なったそうで、同社の説明によれば最大処理性能は以下のように大幅に向上している。

ただ性能/消費電力比はERGOの方が多少高い(3つ上の画像と同じ条件ではERGO 2は2465IPS/Wだそうだ)あたり、プロセスそのものは引き続きGlobalfoundriesの22FDXのままなのかもしれない。

肝心のNNクラスターの中身は不明なままであるが、エッジというかエンドポイント向けの有力なAIプロセッサーの1つになるかもしれない。

この記事に関連するニュース

-

低消費電力の色素増感太陽電池ベース光電子シナプス素子を開発 ~エッジAIデバイスの実現に向けて、新たな可能性を開拓~

PR TIMES / 2024年11月26日 12時40分

-

onsemi、65nm BCDプロセスによるアナログ/ミクスドシグナルプラットフォーム「Treo」を発表

マイナビニュース / 2024年11月15日 17時23分

-

フォトネーションが三回目となるマネジメント・バイアウトを完了

共同通信PRワイヤー / 2024年11月14日 10時6分

-

次世代AIアクセラレータIP「ZIA A3000 V2」リリース

PR TIMES / 2024年11月8日 15時15分

-

Metaが自社開発したAI推論用アクセラレーターMTIA v2 Hot Chips 2024で注目を浴びたオモシロCPU

ASCII.jp / 2024年11月4日 12時0分

ランキング

-

1イオンカード、不正利用に関するNHK報道を受け声明 「1日も速く調査結果を報告できるようにする」

ITmedia NEWS / 2024年11月29日 16時52分

-

2LINEアルバム、他人の写真が誤表示される不具合で続報 「30日午前には解消予定」 Android版はアップデートを

ITmedia NEWS / 2024年11月29日 18時51分

-

3飼い主のお仕事邪魔してご満悦?ノートパソコンの上にどっしり座る猫ちゃん

おたくま経済新聞 / 2024年11月30日 7時0分

-

4NHKのネット受信契約(案)が“ダークパターン”過ぎて見過ごせない件(前編) NHKの見解は?

ITmedia NEWS / 2024年11月28日 19時9分

-

5FRONTIERの「ブラックフライデーセール」スタート、高コスパCore i7搭載機やRyzen 7 9800X3D搭載機に注目

マイナビニュース / 2024年11月29日 17時16分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください