EUV露光で堀った溝を削って広げる新技法Sculpta EUVによる露光プロセスの推移

ASCII.jp / 2023年5月15日 12時0分

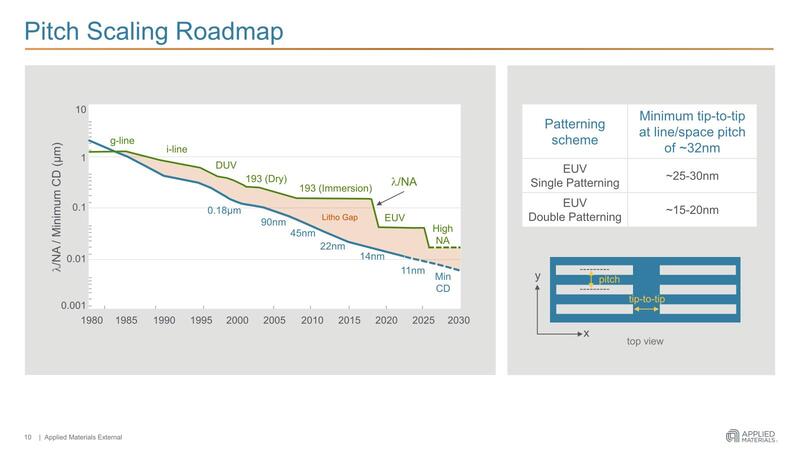

前回は、EUVでも普通に露光できるのは5nm世代まで、という話をした。今回は、ダブルパターニングとSculptaという新技法を解説しよう。

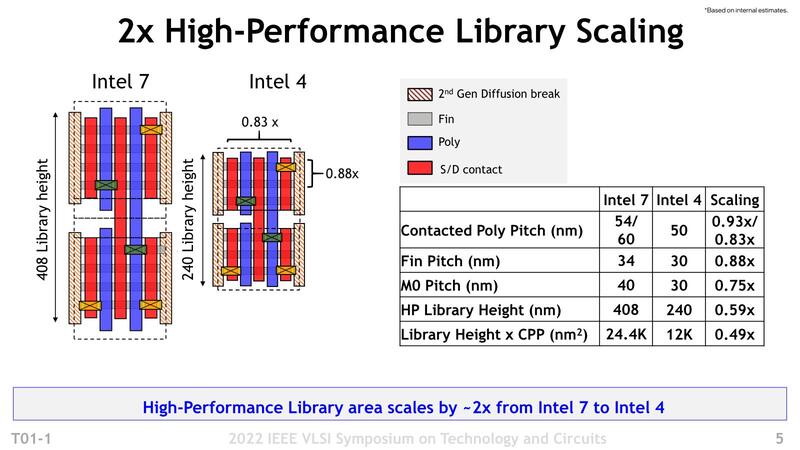

ちなみにTSMCはN5のプロセスジオメトリー(Contact Poly PitchやFin Pitchなど)を一切説明しておらず、ただN7世代と比較するとSRAMセル(HD:High Density)の寸法が0.78倍(0.021μm)になった、という数字のみを発表している。幸いにSamsungの5nm世代(5LPP:現在はSF5という名称になっている)の数字は公開されている。

下の画像と比較してもらうとおおむねIntel 7に近いが、FinやM0はもう少し密度が高いという程度で、Intel 4にはやはりおよばないことがわかる。フィンの間隔などはそろそろEUVのシングルパターニングの限界に近いことがわかる。

そしてTSMCで言えばN3、Samsungで言えば旧3GAE(3nm GAA Early:現在はSF3A)以降、インテルのIntel 4以降ではもうシングルパターニングでは限界に達している。そこでダブルパターニングが登場することになった。

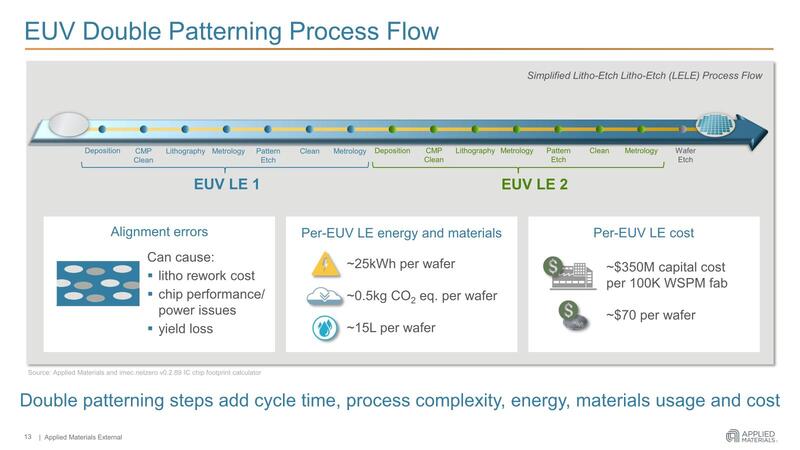

EUV露光を2回実行する ダブルパターニング

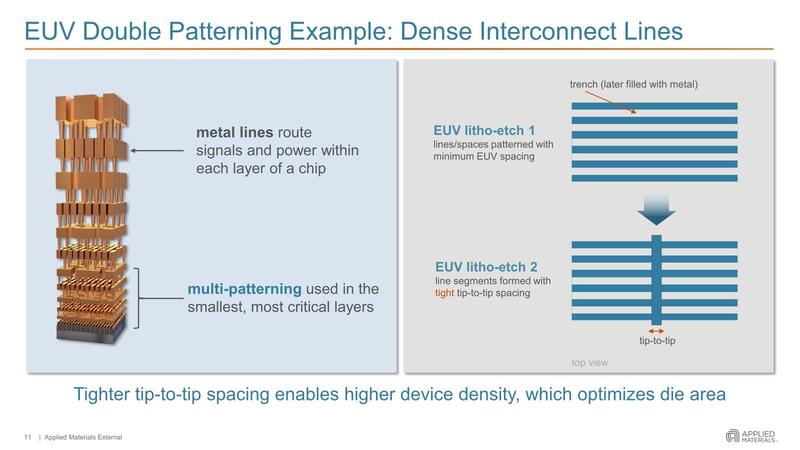

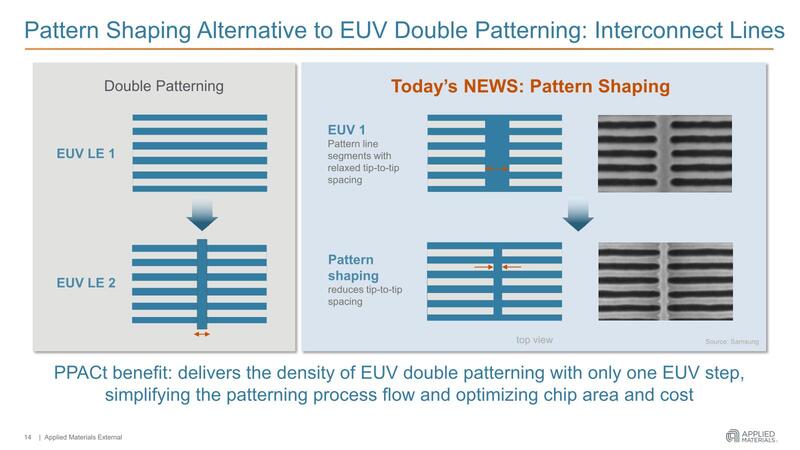

具体的にどうするか? であるが、例えば上の画像にも出てきた上下方向に並ぶフィンを貫くように縦方向に配線を構築するというケースでは、以下の工程で実装することになる。

(1) まずフィンを最初のEUV露光→エッチングで構築する。縦方向の配線は考えない。 (2) エッチングした溝を一旦金属で埋める。 (3) 2度目のEUV露光→エッチングで、今度は縦方向の溝を作る。 (4) (2)で埋めた余分な金属を取り除く。

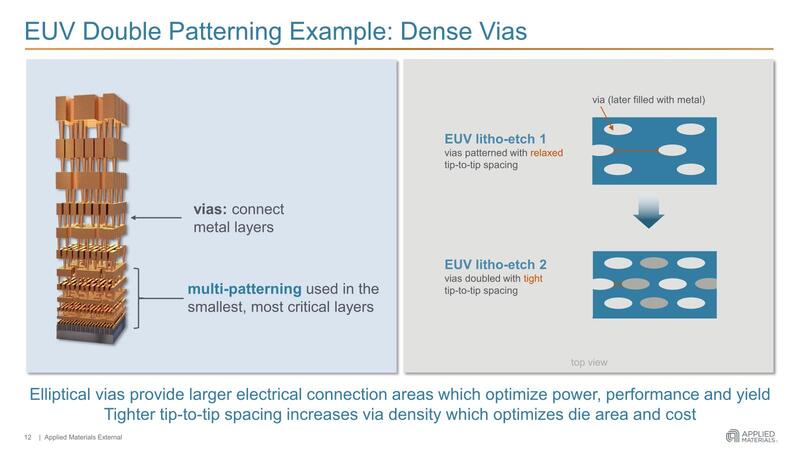

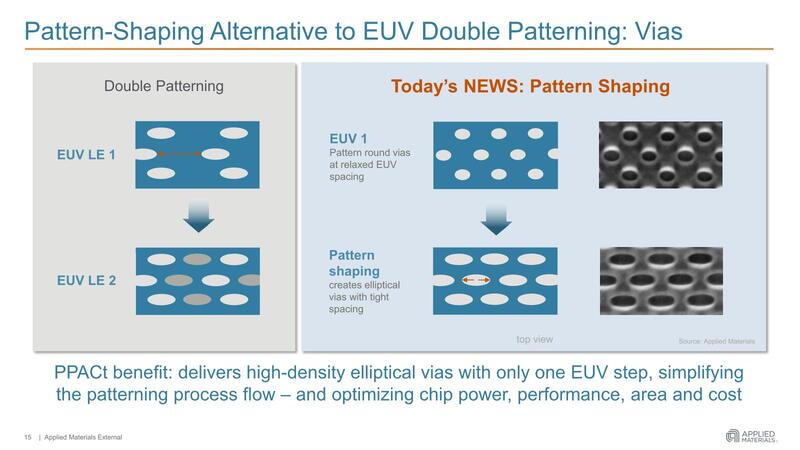

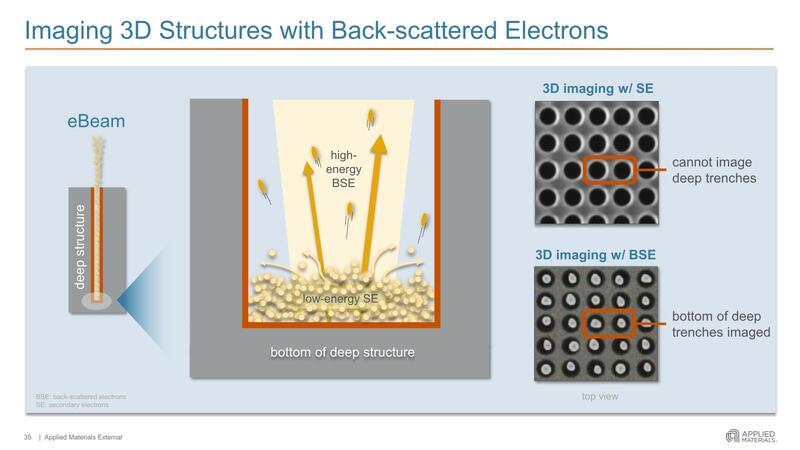

これは穴を掘る場合も同じだ。DRAMやフラッシュでは深い穴を掘る必要があるが、それとは別にロジック向けでもVIA(貫通電極)向けに穴を構築する必要がしばしばある。

これはトランジスタと配線層、あるいは配線層同士の接続に使われるし、最近ではチップ同士の3D積層(AMDの3D V-Cacheなどこの最右翼だ)には膨大な数のTSV(シリコン貫通電極)が使われるから、高密度の穴開けが要求されることもある(*1)。

ただしEUVのシングルパターニングでは穴の直径はともかく、穴の間隔をそれほど詰められなかった。そこでダブルパターニングで2回に分けて穴を開けることで密度を高める方策がとられていた。要するに以下の工程になるわだ。

(1) まず白い穴を最初のEUV露光→エッチングで空ける。 (2) エッチングした溝を一旦金属で埋める。 (3) 2度目のEUV露光→エッチングで、今度は灰色の穴を空ける。 (4) (2)で埋めた余分な金属を取り除く。

この方式の問題はいろいろある。まず2回のEUV露光→エッチングの際に位置のずれがあると、それでアウトである。ダブルパターニングはArF(フッ化アルゴン)時代にはさんざん行なわれていた技術であるが、透過式マスクと反射式マスクではやり方が違うし、位置合わせの精度はArF時代よりもさらに厳しい。

またEUV露光を2回実施するので、それだけ消費電力(や薬品類)の消費も大きく、スループットもそれだけ落ちる。ということはウェハーコストの増大につながるわけだ。1回のダブルパターニングあたりおおむね70ドル程製造コストが上がる、というのがApplied Materialsの試算であるが、このダブルパターニングをどれだけする必要があるのか? というのが次の問題だ。

例えばTSMCのN3の場合、25回のEUV露光が必要で、しかもそのほとんどがダブルパターニングだった。ということは、仮に20回だとしても1400ドルほど原価が上がることになる。

N3Eは露光を19回に減らし、しかもシングルパターニングで済むようにプロセスジオメトリーを変更したことで、大幅に製造難易度とコストを下げたことで広く採用されるようになったことを考えると、できればEUVのダブルパターニングは避けたいという意向が働くのは無理もない。

ただN3Eはともかく、今後登場する予定のTSMCのN3P/N3X/N2やSamsungのSF3(旧3GAP:2024年量産開始予定)、Intel 3/20A/18Aなどではダブルパターニングの利用は避けられないと見られていた。

(*1) 3D積層用のTSVは、現在は双方のダイの熱などに起因する歪みに対応する「遊び」を確保するために、あまり高密度での実装にはなっていない。ただ今はともかく今後も密度が低いままか? というのはまた別の話である。

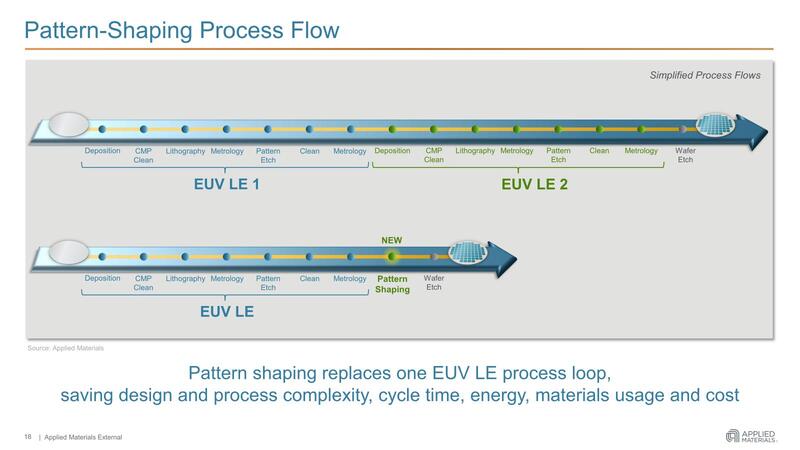

堀った溝を削って広げる新技法 Sculpta

こうした問題に対する解決策として今年2月末から3月頭にかけて開催されたSPIE Advanced Lithography + PatterningというイベントでApplied Materialsが発表したのがCentura Sculpta Patterning Systemである(長いので以下Sculpta)とする。

“Pattern-Shaping Technology”とされるこのSculpta、要するに「EUV露光+エッチングで堀った溝を広げる」仕組みである。例えばダブルパターニングの例の写真にあるような溝を作る場合、まずは同じように横方向の溝に加え、縦方向の配線も同時に構築する。

ただそのままだと縦方向の配線が太いままである。そこでSculptaを使って縦方向の配線を細く削り込むという仕組みだ。

同様にダブルパターニングの例の写真にあるような楕円穴の場合、まず小さな穴を規定の位置にEUV露光+エッチングで空けたうえで、その穴をSculptaを使って広げることで、高密度な穴の実装が可能になる。

この削り込み作業、Applied Materialsが公開した動画の1分44秒あたりからを見てもらうとわかりやすい。

これは空けた穴を広げる手順を示したものだが、EUV露光とエッチングが終わった後のウェハー全体に対して、「ピンク色の怪光線」を当てると穴がどんどん広がっていく様が示されている。これにより、EUV露光→エッチングを1回で済ませられる、というのがApplied Materialsの主張である。

この「ピンク色の怪光線」はなんだ? という話はApplied Materials自身は一切公開していない。可能性として考えられそうなのは2種類ある。1つはeBEAM(電子ビーム)だ。

低コスト、高解像度のeBEAM(電子ビーム)で削り込む?

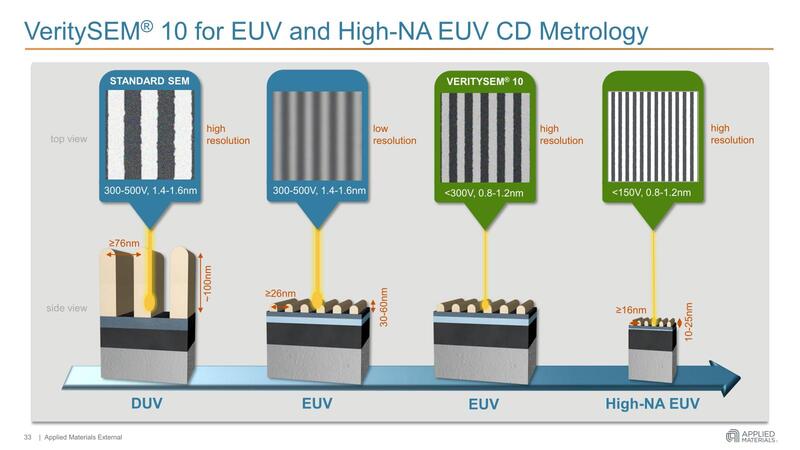

2月28日にApplied Materialsが発表したのはSculptaだけでなく、もう1つVeritySEM 10というシステムがある。こちらはなにをやっているかというと高精度測定を行なうためのシステムである。

よくトランジスタの断面積を示すのにSEM(Scanning Electron Microscope:走査型電子顕微鏡)と呼ばれるものが使われているが、従来型のSEMを使うとEUVではくっきりとした画像にならないという問題があった。

Applied MaterialsはeBEAMの線源を工夫したCFE(Cold Field Emmition)eBEAMという方式を開発して昨年末に搭載製品を発表しており、今回のVeritySEM 10もこのCFE eBEAMを利用したものと想像される。

このVeritySEM 10はあくまで測定用なので対象物を削るにはつたないわけで、ビーム径は絞りつつも出力は抑えめにしていると考えられるが、もしCFE eBEAMの出力がもっと上げられるならば、電子ビームを絞り込むことでパターンを削ることそのものは可能と思われる。

懸念事項は、その出力である。もともとeBEAMはEUVと並び、次世代半導体の露光方式として検討あるいは開発が行なわれていた。実際連載700回で説明した、インテルがIEDMで発表した技術のほとんどは、その製造はeBEAM露光で行なっている。

原理的に物理的なマスクが要らない(eBEAMの照射パターン制御にマスクの情報を喰わせてやるだけで良いので、マスクを物理的に製造せず、設計だけをしてそのデータをeBEAM露光機に与えれば済む)から低コストであるとか、解像度そのものがはるかに微細(電解放出型で0.1nm、電子放出型でも1nm)といったメリットがある。

その半面、「完成するまで欠陥があるかどうかわからない」「スループットが絶望的に低い」という問題があった。特にスループット、2010年頃の数字ではまだ1枚/時未満、少し前の数字でも数枚/時程度で、EUV露光機の160~170枚/時と比べて2桁の開きがある。

今回のCFE eBEAMで出力を上げた時、どの程度のスループットが出るのかはかなり謎である。もっともウェハーを丸ごと露光するのではなく、穴を広げるだけならもう少しスループットが上げられるのかもしれないが、正直どの程度のスループットで「穴を広げる」処理が可能なのかに関しての情報は一切公開されていない。

加えて言えば、先の動画の2分13秒あたりで、「ウェハーを任意の角度に回転させることで全方位で削れる」としているが、実際には何らかの制約がありそうな気もする。

従来のプラズマで削り込む

もう1つの可能性はプラズマを利用して削る方法だ。もともと半導体業界では、プラズマを利用してウェハーの表面を削り取るプラズマドライエッチングという手法が広く利用されている。もちろんApplied Materialsでもプラズマドライエッチングの機器を提供している。

問題は、今回のような細かい寸法のエッチングが本当に可能か? というあたりである。同社はすでにProducer Selectra Etchという微細なエッチング装置を提供しているが、これはプラズマではなく化学薬品ベースのエッチング手法である。プラズマベースで同じ微細さを提供できるのか? は判断が付かない。

Sculptaは下の画像にある4つの装置から構成される。

普通に考えると以下のあたりだろうか?

(1) 削りたくない場所に保護膜を形成 (2) eBEAMないしプラズマでシャープニング (3) 保護膜除去 (4) 後処理(削りカスの除去や保護膜削除後の表面の荒れの平滑化とか)

仮にSculptaを導入する場合、これは顧客の設計にも関係してくる。というのはマスクの作り方が変わるからで、現在EUVのダブルパターニング向けにテープアウトしたマスクではSculptaのフローに適合しない。

従って、改めてシングルパターニング向けのマスクを作り直す必要がある。これは場合によってはPDK(Process Development Kit)の変更もともなうものになるので、「既存の設計のまま使えます」ということにはならない。それもあってか、先のプレスリリースを読むとインテルとSamsungからのメッセージが寄せられているのに、TSMCからはない。

これは裏を返すと、すでに大量のEUVダブルパターニングでテープアウトした顧客を抱えているTSMCは、現行の3nm世代にはSculptaを突っ込む余地はなく、仮に導入したとしてもN2のさらに先になるのに対し、インテルやSamsungは今からSculptaを導入しても間に合うことを意味している。

といってもSamsungで言えばSF3、インテルならIntel 4/3に関してはさすがに間に合わず、導入するとしてもSamsungなら2025年のSF3P(旧3GAP+)ないしSF2以降、インテルならIntel 20Aないし18A以降になるのではないかと想像する。

EUV露光を完全にモノにしたTSMCと、まだ悪戦苦闘しているインテル/Samsungという対比が透けて見えるのはおもしろいし、このSculptaがどこまで広く利用されるようになるかは不明だが、この先GAA世代を踏まえて半導体製造装置メーカーもいろいろ工夫している、ということを偲ばせる発表であった。

この記事に関連するニュース

-

アプライド マテリアルズ エネルギー効率に優れたコンピューティングのサミットで先進パッケージング新コラボレーションモデルを発表

PR TIMES / 2024年11月22日 12時45分

-

ファーウェイの最新AI半導体、来年初めに量産開始へ=関係筋

ロイター / 2024年11月21日 16時37分

-

アップル「iPhone 17」A19チップ、3nmプロセスでチップ製造か

ASCII.jp / 2024年11月20日 20時0分

-

米商務省、CHIPSプラス法に基づきコーニングとパワーエックスに助成(米国)

ジェトロ・ビジネス短信 / 2024年11月11日 11時0分

-

米商務省、国立半導体技術センター初の旗艦施設、EUVアクセラレーターをNY州に設立へ(米国)

ジェトロ・ビジネス短信 / 2024年11月1日 11時35分

ランキング

-

1AppleのSafariに関し、英CMAが「ブラウザ市場に悪影響」と調査勧告

ITmedia NEWS / 2024年11月25日 7時25分

-

2新機能がいっぱい!iPadOS 18で進化した「メモ」アプリを使いこなそう - iPadパソコン化講座

マイナビニュース / 2024年11月25日 11時34分

-

3スタバ福袋当選発表に悲喜こもごも SNS「3度目の正直来た」「外れてうつになりそう」

iza(イザ!) / 2024年11月25日 12時11分

-

4「この子出世する」 小学5年生、社会のテストで漢字をド忘れ→ひねり出した“天才的な回答”が240万表示「上手いwww」

ねとらぼ / 2024年11月25日 8時10分

-

5「なんでだよww」 “究極のブルベメイク”をしてみたら……? 衝撃の仕上がりが1600万再生 「腹筋持ってかれた」「面白すぎるw」

ねとらぼ / 2024年11月24日 8時10分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください