Meteor Lakeには4次キャッシュが存在する インテル CPUロードマップ

ASCII.jp / 2023年5月22日 12時0分

4月27日にインテルは2023年第1四半期の決算発表を行なった。売上は1170億ドル(約15兆8900億円)で、28億ドル(約3800億円)ほどの営業赤字を記録するといった大変な状況ではあるのだが、これは事前予測よりも良かったということで、むしろ株価がわずかながら上がる(29ドル→31.79ドル)という、おもしろい事態になっている。

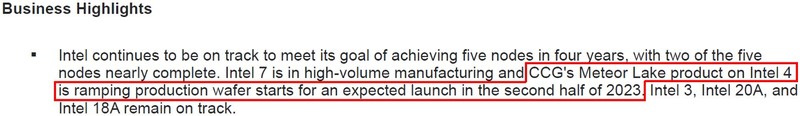

それはともかくとして、この決算発表のリリースの中にこんな一節がある。

表現を見る限り、まだフル稼働状態にはかなり遠い感はあるが、とにかくIntel 4を利用しての量産がスタートしたことを正式に表明した格好だ。5月30日から始まるCOMPUTEX TAIPEIでは、あるいはMeteor Lakeの動作プロトタイプにお目にかかれるかもしれない。そのMeteor Lakeの話がいろいろ流れてきたので、今週はまとめて説明したい。

特許取得で判明したMeteor Lakeの内部構造

Meteor Lakeの内部構造の推定は、連載682回で解説したが、ひょんなところからこの内部構造が出てきた。ネタ元は米国特許US20210081538A1である。Google Patentsを見ると、2020年12月にまず米国で出願され、その後欧州/日本/中国でも出願されている。

発明者の筆頭はインテルのVincent Zimmer氏(Senior Principal Engineer)。タイトルは“Early platform hardening technology for slimmer and faster boot”で、要するにブートの際の時間を高速化するために、ハードウェアとファームウェアを協調動作させる手法に関するものである。

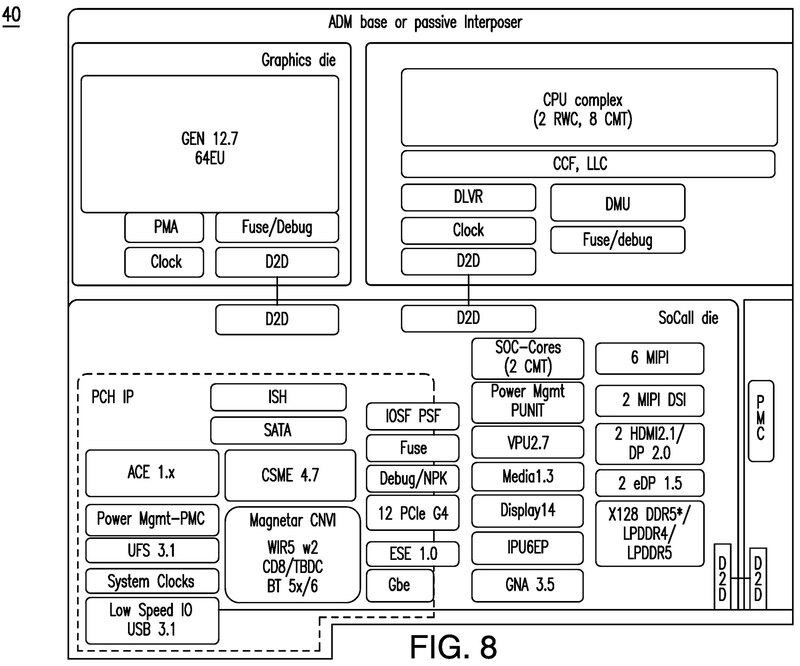

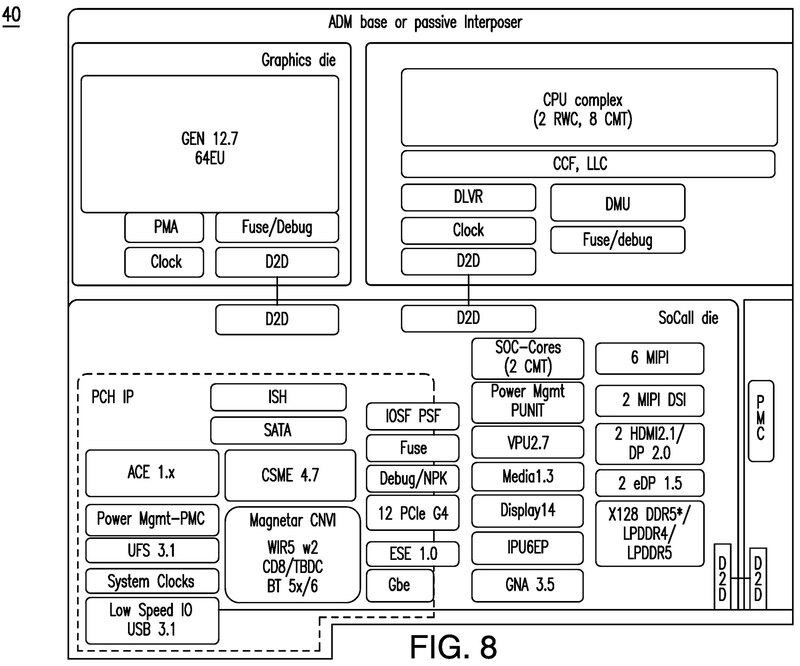

特にセキュア・ブートではどうしてもブート時間が長くなりがちであり、これを高速化するためのテクニックだ。この特許のFigure 8を見ると、これはどうみてもMeteor Lakeだな、と考えざるを得ない。

もっともこれはトップエンドモデルではなく、ディスクリート・グラフィックス用のPCIeも省き、またP-Coreは2つのみなので、U/Y SKU向けのものと思われる。

まず右上のCPU complexはRWC(RedWood Cove)×2とCMT(Crestmont)×8という構成。RedWood CoveはRaptor Coveの延長にあるコアで、大きなアーキテクチャー上の変更はない模様。一方のCrestmontはTremontの延長にあるGracemontと異なり、アーキテクチャーを刷新したとされているが、こちらも詳細は不明なままである。こちらの分析は後ほど。あと、LLCはSoCダイではなくこのCPUダイに搭載されている。

次いでグラフィックス・ダイ。こちらにはGen 12.7で64EUの構成のものが搭載される。このGen 12.7ってなに? という話だが、扱いとしてはIntel DG2に属するものになる。

要するにAlchemist世代のGPUだ。Alchemist世代ではXe-Core1個あたり16EUなので、これは4 Xe-Coreということになる。Intel Arc A380の半分であるが、統合GPUで専用メモリーを持たないことを考えれば、これ以上強化しても性能向上は見込みにくいだろうから、妥当な構成と思われる。

ちなみに以前の想像図ではGPUダイに3次キャッシュを入れておいたのだが、これを見ると3次キャッシュがない(CPU タイルの方にはLLCの表記があるので、ここに3次キャッシュが入っていると考えられる)。全SKUでLLCがなしなのかどうかまでは正直判断できない。

Crestmontはインテルの工場だけではなく TSMCの工場でも製造できる

次いでSoCダイであるが、左下のPCH IPはいわゆるPCH用の機能を全部統合したもので、SATAやUSB、GbE、PCIe Gen4、パワー・マネジメントなどに加え、Magnetar CNVIという大きなブロックがあるが、これはWi-Fiブロックである。

CNVIはConnectivity Integration(インテル統合接続)と呼ばれる、インテルが自社のWi-Fiモジュールを容易に接続するためのI/Fである。

おもしろいのはその右側だ。まず上からCrestmont×2のCPUコアがある。これはSoCの制御用で、冒頭に述べた特許の中ではセキュア・ブートの中でも使われているが、別にセキュリティ制御専用と言うよりは、SoC側の諸々の処理をCPUタイル上のCPU Complexを動かすことなく行なえるようにしよう、ということのようだ。

逆に言えば、このCrestmont×2はブート後にOSから認識されるのかどうかはやや微妙である。個人的にはこのCrestmont×2は見えない形になっているのではないかと考える。

ところでこのSoCタイル、製造はTSMCのN6を利用するはずである。つまりCrestmontはインテルの工場だけではなく、TSMCの工場でも製造できるように工夫されているということだ。

Crestmontがアーキテクチャーを一新したというのは、この「工場を選ばない」特性を実現するために、物理的な設計だけでなく論理的な設計も配慮されている(インテルの工場でしか実現できない速度設計にしないなど)という意味なのかもしれない。

その下のパワー・マネージメントはSoCの、というよりはCPUタイルの電力管理用に見える。その下のVPUはMovidius VPUを指しているものと思われる。実はインテルの第3世代VPUであるMobidius VPU、現状Mobidius 3700Vのみ発売されており、上位の3800V/3900Vは先日販売終了になってしまった。

どうもインテルは今後ディスクリートの形でのMobidiusのVPUは、限られた顧客にのみ提供するに留めて、その代わりMeteor Lake以降のSoCタイルにこのVPUを統合する形で提供するらしい。

続くMedia 1.3はビデオ・エンコーダー/デコーダー、Display14はGPUと対になるディスプレーエンジンのことである。IPU6EPはISP(Image Signal Processor:カメラ映像エンジン)で、これはAlder Lakeの世代と違いがない。

次のGNA 3.5は以前説明したとおりのものだ。その右にあるMIPI/MIPI DSI/HDMI/eDPはどはどれも映像出力用の端子。その下にあるのは128bit幅のDDR/LPDDR5/LPDDR4対応メモリーI/Fである。

このSoCタイルのさらに右にはPMC(Power Management Controller)が配されるが、これはCPU全体の電源管理用だろう。上位機種にはこれとは別に、やはりD2D(Die to Die)I/F経由でIOEタイルが接続されるはずだが、先に述べたように、UあるいはY-SKU向けということでここでは省かれているものと思われる。

Meteor Lakeには4次キャッシュが存在する

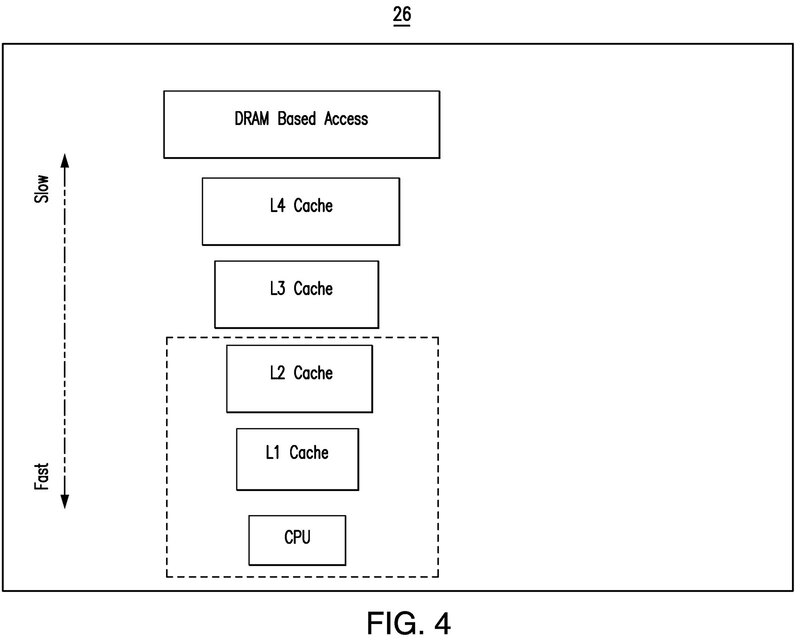

これとは別に、やや気になる記述が特許の中に存在する。それが下の画像である。

この図の脚注は単にメモリーの階層化を示したもの、としか書いていないのだが、この特許の本題である起動の高速化の手法の一部で、DRAMの初期化をしてからブートすると遅くなるので、DRAM初期化は最後に回すとしたうえで、仮に初期化中のみ4次キャッシュをSRAMとして扱うようにすることで、DRAMを利用するよりも高速アクセス可能で、かつブート用のコードを全部4次キャッシュ中に展開できるというテクニックを披露している。

ここで3次キャッシュでなく4次キャッシュを名指しにしていることがポイントで、ということはMeteor Lakeには4次キャッシュが存在する(少なくとも存在するSKUがあり得る)ということになる。

他にも「次世代のClient SoCのアーキテクチャーには、大規模なオン・パッケージ・ジャッシュが導入される可能性があり、これによって斬新な使い方が可能になります。4次キャッシュ(例えば、“Adamantine”または“ADM”)のアクセス時間は、DRAMのアクセス時間よりもはるかに短い場合があり、これはホストCPUとセキュリティコントローラーの通信を改善するために使用されます。」という文章が入っている。

ちなみに“Adamantine(アダマンタイン)”は「堅固・強固」の意味で、あまりこの業界で使う用語ではないのだが、とりあえずインテルはこのMeteor Lakeの4次キャッシュをADMキャッシュと呼んでいるらしい。

実はこのADMキャッシュこと4次キャッシュ、もう1つ情報源がある。今年4月11日にインテルのFei Yang氏(Software Architect:その前はMotorola Mobilityに在籍しており、Android Kernel周りの作業に携わっているらしい)がポストしたグラフィックスドライバー用のパッチがこちらなのだが、冒頭に「Meteor Lakeでは、グラフィックスはもうLLCをアクセスしない。

この対応パッチを、ADM/4次キャッシュのサポート、およびMOCS/PATテーブルアップデート(のパッチ)と併せて投稿する」とあり、やはりMeteor Lakeにはなにかしら4次キャッシュ/ADMキャッシュを搭載するSKUが予定されているのは間違いなさそうだ(最終的に製品として出てくるかどうか、はまた別の話だが)。

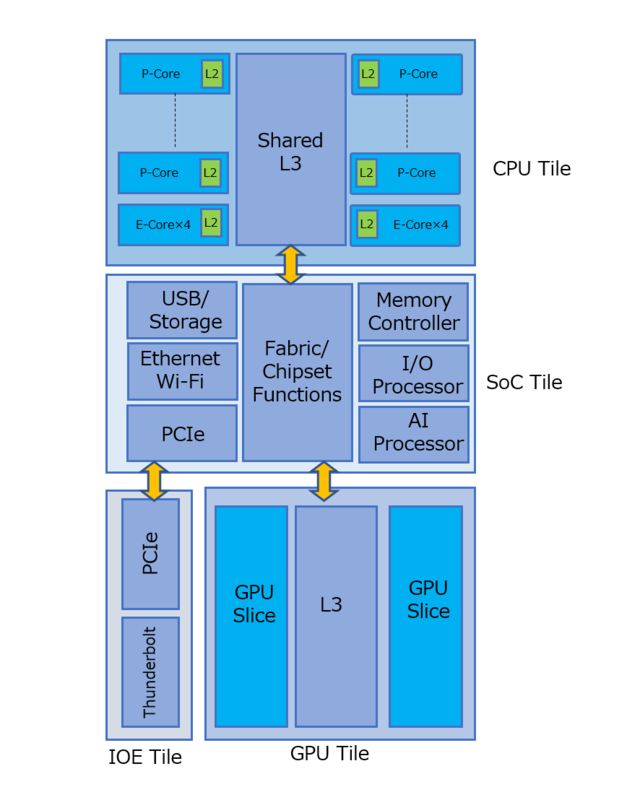

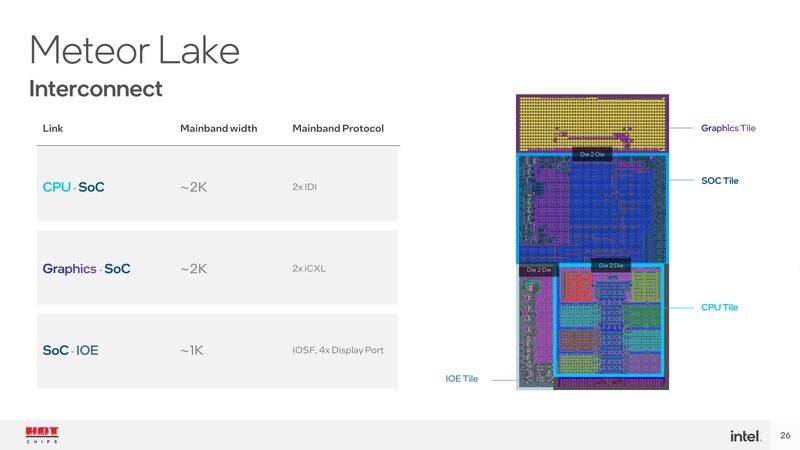

ところでこの4次キャッシュ、一体どこに置かれるのだろう? というのが次の疑問。「大規模なオン・パッケージ・キャッシュ」というあたりは、CPUタイルではなさそうである。可能性があるのはSoCタイルかベースタイルのどちらかである。もう少し細かく言えば

(1) SoCタイルの一部に4次キャッシュを搭載

TSMCのN6をキャッシュに使うというアイディアは、例えばAMDのRadeon RX 7000シリーズでも行なわれている。現在のプロセスではN5以下に微細化しても、SRAMに関してはほとんど容量が増えないので、N6というのはバランス的にちょうど良いとされる。

連載682回でMeteor Lakeのパッケージを掲載したが、どう見てもSoCタイルが大きすぎる。4次キャッシュの容量次第ではあるが、64MBクラス程度ならギリギリSoCタイルでまかなえるように考えられる。この方式が、構造的には一番楽である。

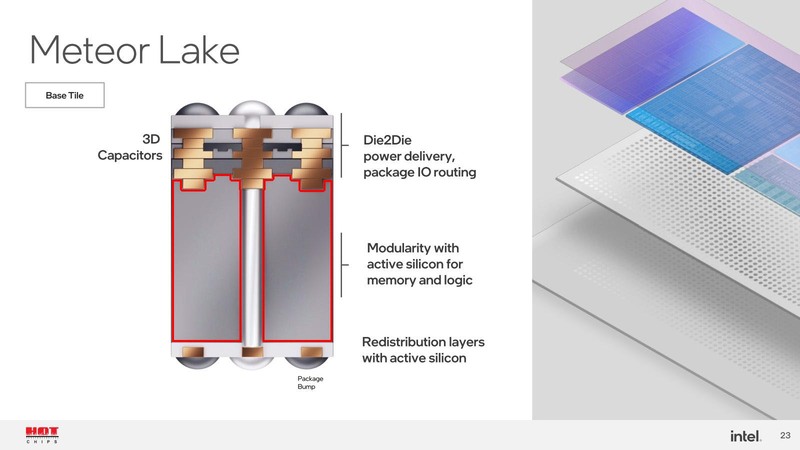

(2) Base Tileの一部に4次キャッシュを搭載

ベースタイルの目的はタイル同士の接続に加え、電源供給を改善する目的があるという話は連載682回で説明したとおりだが、全部が全部電源供給にしなくてもいいだろう、という気はしていた。

CPUタイルの直下は電源供給用に必要だろうが、SoCタイルやIOEタイルの真下はそこまで電源供給に充てなくても普通に足りると思われるからだ。したがって、この一部を4次キャッシュにするというアイデアはあり得る。

ただこの方法の問題は、インテルの22FFLプロセスでベースタイルが構成されていることを考えると、フルスピードでのアクセスはまず間に合わないと思われる。もちろん4次キャッシュなので、例えばコアの半分の速度で動かすといった形でも許容される可能性はある。

もしもべースタイルの一部を4次キャッシュとして割り当てるのであれば、下の画像になにかしら言及があっても良かったように思える。

以上のことから、筆者としては(1)説を推したい。ただこの場合だと、容量はせいぜいが64MB程度で、やや少ないかもしれない。逆に(2)説だと128MBなどの構成も比較的容易だろう。なお、繰り返しになるが全SKUで4次キャッシュが有効になるかどうかは不明である。

Meteor LakeはCore iではなく Core Ultraという名称になる?

最後に小ネタを1つ。5月1日付けのtom's Hardwareが、ブランド名の変更の可能性を報じた。曰く、Core Ultraという名称になるのではないか? とのこと。

昨年9月、インテルはPentium/Celeronに代わる新しいブランドとして“Intel Processor”という名称を発表したが、これに続く形なのかもしれない。

現状Intel ProcessorはNシリーズとUシリーズで合計6製品のみがラインナップされているが、あるいはこのタイミングでさらに増えるのかもしれない。

この記事に関連するニュース

-

Core Ultra 7 265K&RTX 4070 Ti SUPER搭載ゲーミングPC、空冷クーラーでも本当に大丈夫?

ASCII.jp / 2024年11月16日 10時0分

-

Lunar LakeはMeteor Lake比でどこまで性能向上? 最新ドライバ適用「Core Ultra 7 258V」搭載ノートを試す(後編)

マイナビニュース / 2024年11月14日 15時0分

-

Lunar Lake搭載で約946g! 超軽量ビジネスPCとして格が上がった新型「MousePro G4」を試す

ITmedia PC USER / 2024年11月6日 15時0分

-

薄軽VAIOの旗艦モデル「VAIO SX14-R」の“数値以上の変化”を知る

マイナビニュース / 2024年11月1日 8時0分

-

Arrow Lakeがついに市場投入! ASRock・ASUS・MSI・GIGABYTEが一堂に会して製品アピール、Micronの姿も

マイナビニュース / 2024年10月28日 14時33分

ランキング

-

1HD-2D版『ドラクエ3』勇者「俺だけバラモス倒せなかった…」←なんで? 嘆きの声続出の理由

マグミクス / 2024年11月25日 17時25分

-

2ビューカード、顧客との通話内容を録音したSDカード20枚を紛失

ASCII.jp / 2024年11月25日 17時5分

-

3メルカリ、不正利用へのサポート強化と補償方針を発表 ネットで意見「当たり前」「個人的には期待」「悪意のあるやつは排除して」

iza(イザ!) / 2024年11月25日 13時21分

-

4スタバ福袋当選発表に悲喜こもごも SNS「3度目の正直来た」「外れてうつになりそう」

iza(イザ!) / 2024年11月25日 12時11分

-

5「不要なスマホなどをdポイントと交換」 ドコモ、小型機器の買い取りに挑戦 都内の25店舗で

ITmedia Mobile / 2024年11月25日 16時21分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください