インテルの最新パッケージング技術でCPUが100×100mmに拡大 インテル CPUロードマップ

ASCII.jp / 2023年6月5日 12時0分

5月18日、インテルは突然Advanced Packagingと題した説明会をオンラインで開催した。タイミングとしては突飛というか、なぜこの時期にこのテーマを? となるし、初めて聞く話はないのだが、それでも以前からの疑問がいくつかクリアになったので説明しよう。

ちなみにインテルのパッケージング技術は、連載627回のほかに、連載682回にHotChipsでの発表をベースに紹介しているので、これらからの差分という形での説明となる。

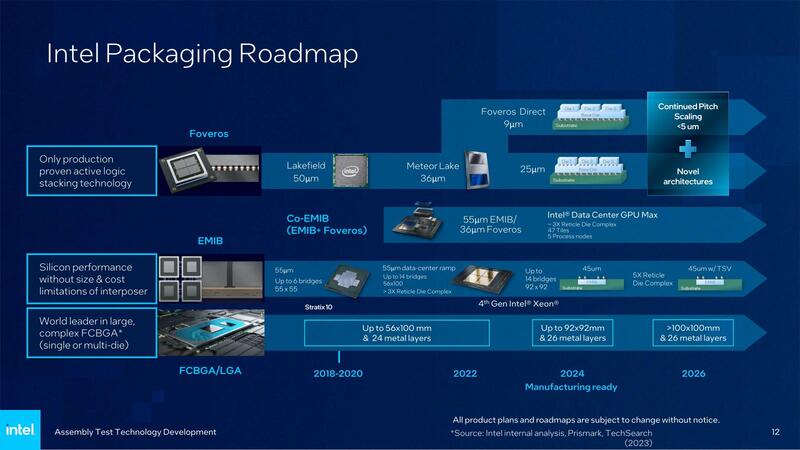

連載682回の時点ではまだ第2世代Foverosに関しては量産製品は存在していなかったのだが、今年1月にPonte VecchioがIntel GPU Maxとして発売になったことで、Bump pitch 55μm EMIBと36μm Foverosの組み合わせ技もちゃんと量産できることが実証された格好になる。

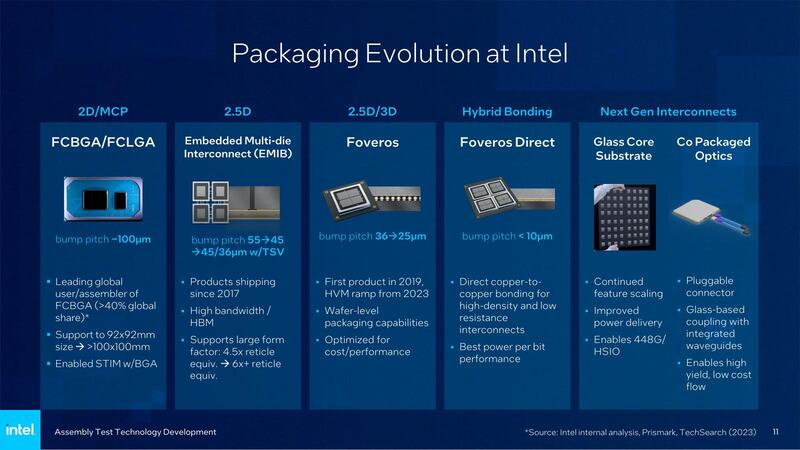

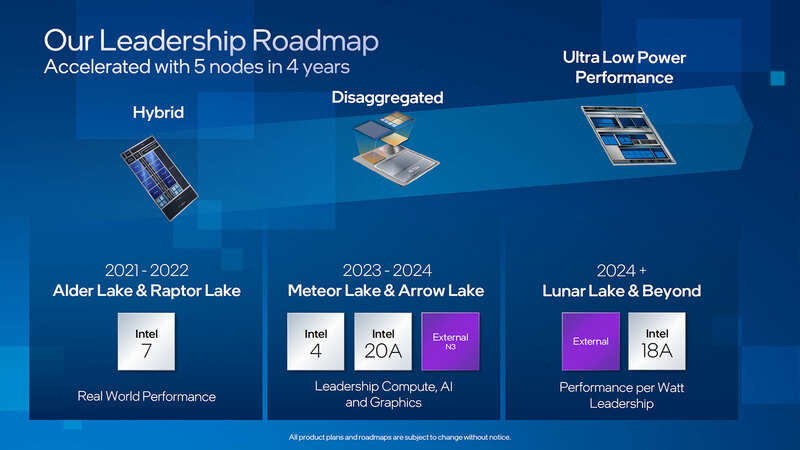

さて、ここからの話が若干のアップデートである。下の画像がそのアップデートの項目だ。

(1) FCBGA/FCLGAパッケージの寸法が最大92×92mmから100×100mmに拡大 (2) EMIBはBump Pitchの微細化ロードマップが55μm→45μm→36μmに変わり、36μm世代ではTSVが利用できるようになることが明らかにされた (3) FoverosはBump Pitchが36μm→25μmになるとされた (4) Foveros Directの第2世代はBump Pitchが9μmになると明らかにされた (5) 次世代パッケージとしてガラスベースのSubstrate、およびCo-Package Opticsが提供される(予定)

基板のパッケージサイズを順次大きくしていく

順に見ていくと、まず(1)のFCBGAの話だが、基板のパッケージサイズを今後100×100mm以上に引き上げられるとしている。もっともこれは一気にではない。まず2024年にこれまでの56×100mmという寸法を92×92mmまで拡張、また配線層を従来の24層から26層に引き上げるとする。次いで2026年にはこれを100×100mm超に拡張するという形だ。

この92×92mm、という数字はEMIBでも出てくるあたり、2024年度に向けて新しい製造装置を導入、これが92×92mmに対応ということなのかもしれない。

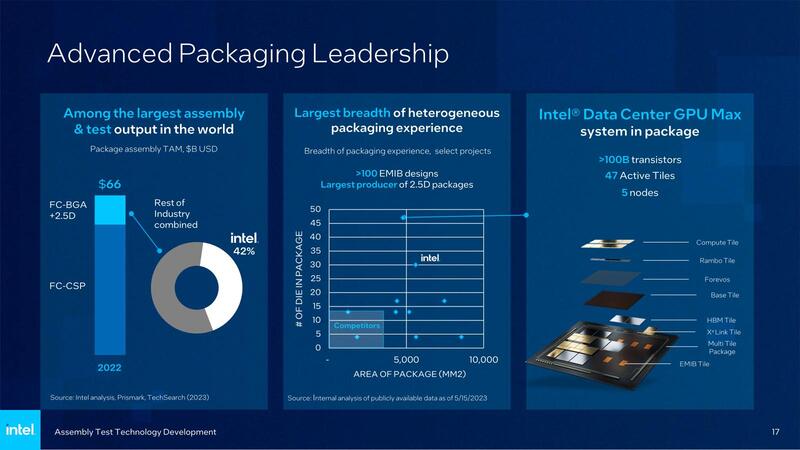

余談だが、インテルはこのFCBGA/FCLGAパッケージのシェアで4割を超えており、業界トップであるとしている。もっとも同社の提供しているFCBGA/FCLGAのBump Pitchはおおむね100μm程度なので、AMDがRadeon RX 7000シリーズの接続で利用できるレベルか? というと少し怪しい。

さらに余談になるが、昨今OSAT(Outsourced Semiconductor Assembly & Test:要するに後工程の処理)を担うベンダーの技術開発もすさまじい。というのは、CoWoSでもEMIBでも良いのだが、シリコン・インターポーザーを使ってダイ同士を接続する方式が流行ってしまうと、こうしたシリコン・インターポーザーはそれこそTSMCだったりSamsungだったりUMCだったりインテルだったりといった、前工程を製造するファウンダリーが手掛けている関係で、ここの部分をファウンダリーに持っていかれてしまうことになる。

そこで、従来のオーガニックパッケージを使いながら、シリコン・インターポーザーに負けないBump Pitchと配線密度を実現する、といった解決策を打ち出し始めており、Radeon RX 7000シリーズもこれを利用した格好だ。

インテルは、今後もFCBGA/FCLGAパッケージ市場で存在感を維持したければ、こうした動きに対抗していかなければいけないわけだが、これはEMIBと思いっきりぶつかるという話でもあるので、このあたりをどういう方針にするつもりなのか興味ある部分だ。

EMIBのBump Pitchが55μm→45μm→36μmに 36μm世代ではTSVが利用できる

次いで(2)のEMIB。2021年8月の時点でのEMIBのロードマップはBump Pitchが55μm→45μm→40μmとされていたはずだが、この40μmがなくなり、45μmのままで行くことが明らかにされた(36μmはFoverosの方の数字)。

また、より大きなEMIBのインターポーザーを作れるようになる、としている。この「現在はreticleから4.5倍どまりだが、6倍以上に引き上げる」は説明が必要だろう。

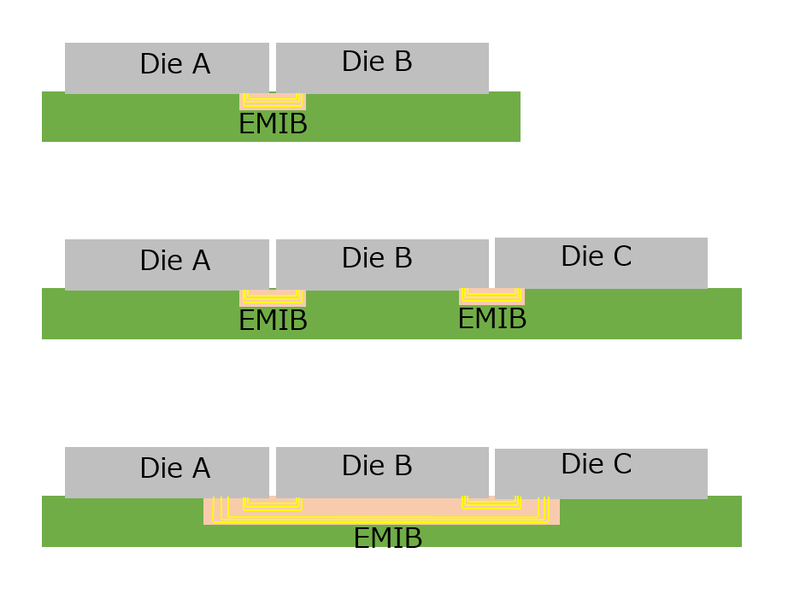

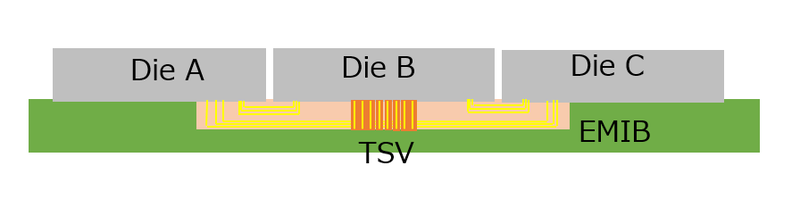

EMIBも、例えばSapphire Rapidsの場合ではダイ同士のPoint-to-Pointで済んでいるから図1の上段のように小さな構造で構わなかったが、今後UCIeなどで複数のダイを複雑につなぐことを考えると、図1の中段のようにDie AとDie Cを直接接続できないので、Die Bの中にDie AとDie Bをつなぐ配線を仕込む必要が出てきてしまう。

これは不便であり、図1の下段のようにしたいところだ。ただこうなるとEMIBの大きさはどうしてもチップより大きくなる必要がある。

EMIBはシリコン・インターポーザーの一種なので、製造は普通のLSIと同じで、マスクを作って露光をし、エッチングする……という一連の過程を経る。トランジスタを作るわけではなく配線層だけなのでそれほど難しくはないが、必然的に製造できるEMIBの大きさは限界がある。

とはいえ、そもそも今のLSIを作るためのマスクは、もちろん回路の大きさと同じでは作れない(配線幅30nmのマスクなど作れるわけがない)ので、例えば10倍のサイズのマスク(配線幅を300nmにする)を作って、それを露光の際に10分の1の寸法に縮めて転写するわけだ。

この縮める比率を緩めれば、より大きな寸法を作ることは簡単である。これまでは、最大Reticle Limit(1回で露光できる限界の面積:おおむね800mm2)の4.5倍(おおむね3600mm2)までのインターポーザーを作れたが、これを6倍以上(4800mm2以上)まで広げる、という話である。

それともう1つTSVの話。EMIBでTSVをどうやって使うのか? という話で、まさかEMIBからTSVを生やすことで複数のチップを垂直にスタックできるのか? と思ったらそういう話ではなかった。

先ほどの図1に戻るが、この構造ではDie Bは完全にシリコン・インターポーザーの上に載ってしまう。したがって、外部に出す信号や電源/GNDなどもシリコン・インターポーザー経由で配線する必要があるわけだが、TSMCのCoWoSだとその下のパッケージに接続できるので比較的容易である。

ところがEMIBでは基本ダイ間の接続で、パッケージへの接続がない。そこで、図2のようにEMIBの上に載ったチップから直接パッケージにつなげられるTSVを用意し、これを利用して外部への信号あるいは電源/GNDを接続できるようにする、というためのものだそうだ。

このTSVは2026年に利用可能となっている。またEMIB自身の寸法も、現行は55×55mmが最大であるが、2024年の45μm Bump Pitchの世代では92×92mmまで拡大されることになるそうだ。

第3世代のFoverosが2024年頃を目途に立ち上がる FoverosのBump Pitchは36μm→25μmに

次は(3)のFoverosである。先に書いたようにすでに第2世代のFoveros(第1世代はLakefield)がIntel GPU MAXで採用されており、また間もなく発表される(はずの)Meteor Lakeも第2世代のFoverosを利用することが明らかになっているが、これに続き第3世代のFoverosが2024年頃を目途に立ち上がるとされている。

こちらはBump Pitchを25μmに縮小したものである。インテルの以前のロードマップに従えば、Meteor Lakeが第2世代、Arrow Lakeが第3世代に相当することになるのだが、Intel 20Aと組み合わせる形でこの第3世代Foverosがお披露目になる予定なのかもしれない。

Foveros Directの第2世代は Bump Pitchが9μmになる

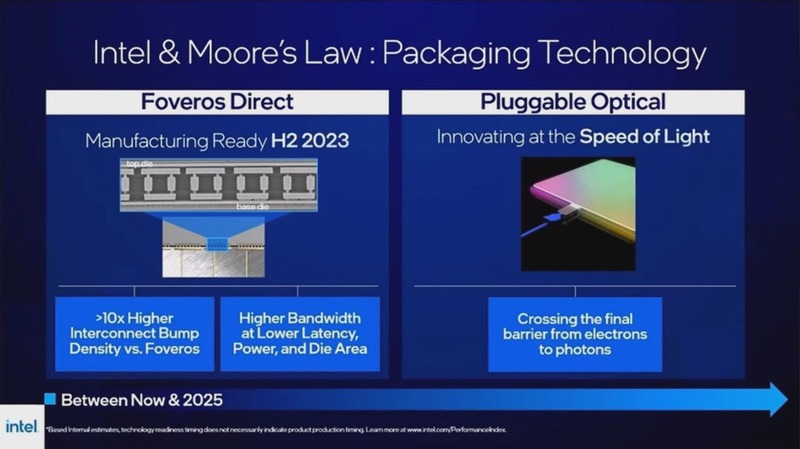

次が(4)のFoveros Directについて。連載第682回では「9μmピッチかどうかは将来公開する」という話だったが、今回ついにこれが9μmであることが明示された。

ちなみにこの先に関して言えば、Foverosは微妙だがFoveros Directは5μm未満のBump Pitchを目指していることも今回示された格好だ。

ガラスベースのSubstrateと Co-Package Opticsが提供予定

最後が(5)の次世代インターコネクト向け。これは要するに、より高速な信号を通すための仕組みである。現在ではPCIeやUCIeでもだいたい32Gbpsあたりが信号速度のピークであり、GDDRも20Gbpsくらいであるが、すでにイーサネットの世界ではレーンあたり100Gbps(56G PAM-4)を超えて200Gbps(112G PAM-4)に対応したチップがサンプル出荷を開始しており、さらにこの先の400Gbps(224G PAM-4)も視野に入り始めた。

ちなみにこれは1レーンあたりの速度である。PCIeもPCIe 6.0ではレーンあたり64Gbps(32G PAM-4)、PCIe 7.0は128Gbps(64G PAM-4)になることが決まっており、より高速な信号をハンドリングする必要がある。

こうした高速な電気信号を扱うのに、従来の基板材料では損失が大きすぎて到達距離が稼げないということで、ガラスベースの基板は従来からいろいろ検討されてきているのだが、ここにきてインテルがパッケージオプションでガラス基板に言及し始めた、というのはもう他に方法がないということもあるが、ガラス基板にまつわる問題(温度変化に起因する歪がLSIチップと異なることによる問題や強度、製造方式など)にある程度目途が立った、ということかもしれない。

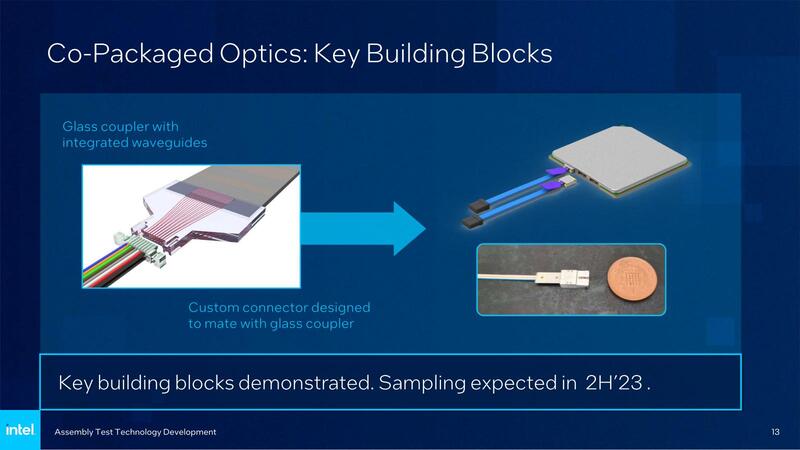

これに絡んでくるのがCo-Package Opticsである。イーサネットそのもので言えば、現状標準化されている銅配線ベースの最大速度は100Gbps(ただしド太い同軸ケーブルを複数使い、配線距離も数m)、CAT-8を使う配線では40Gbps(40GBASE-T)が一番最高速であり、それ以上高速なイーサネットはすべて光ファイバーを使う形になる。この場合のトランシーバーの構造が図3である。

MACはデジタル電気信号の形でイーサネットの入出力を行ない、これをアナログに変換した上で光信号の形で入出力するのがPHYである。この2つは基板上でつながることになるので、ここの信号の高速化のためにガラス基板を使おう、という話である。

実際大規模なスイッチなどでは、こうした構造になる可能性が非常に高い。ただここで図4のようにMACとPHYを同一パッケージ内に押し込めれば、もっと効率が良くなる。

ただMACまでは通常のCMOSプロセスで製造されており、一方PHYの方にはレーザーLEDやフォトディテクターなど通常のCMOSプロセスでは製造できないコンポーネントが含まれる。したがってPHYをCMOSプロセスと親和性のある方法で製造する必要がある。

Silicon Opticsと呼ばれるこの新技術をインテルはもうかれこれ20年くらい手掛けており、連載699回でも触れたように、2022年のIEDMの基調講演の中で2025年までにPluggable Opticsのソリューションを提供する予定であることが公表されている。

今回のCo-Package OpticsはこのPluggable Opticsのソリューションのためのものである。上の図に戻ると、PHY/MACが一体化したチップに光コネクターが接続されているが、現在業界には標準的な「LSIに直接接続するための」光コネクター/レセプタクルというものが存在しない。

これは精度(なにしろ光ファイバーが細いので、きちんとLED/フォトディテクターと位置合わせができないと効率が急激に落ちて通信不能になる)など強度の点で難易度が高く、けっこうがっちりした金属製のコネクター/レセプタクルが利用されているためであり、LSIチップの10倍くらいの厚みがあったりするからまるで適さない。

今回インテルが発表したのは、やや厚みのあるLSIに直接接続できるようなコネクター/レセプタクルである。こちらのサンプルは今年後半に詳細が明らかにされるようだ。

ということで、インテルのパッケージ技術は相変わらず進歩を続けており、今後のプロセスの進化にも対応できるようになっている、という話であってそのことそのものは良いのだが、問題はなぜこの時期にこんな話を突然したのか? である。これがなにかの目くらまし、という話でなければいいのだが……。

この記事に関連するニュース

-

プラネックス、低消費電力&低発熱の2.5Gbpsスイッチングハブ

マイナビニュース / 2024年11月26日 16時0分

-

≪アーカイブ講座≫ AndTech WEBオンライン「半導体基板におけるめっき技術の基礎と材料技術・課題~めっき浴管理やトラブル対策をじっくりと学ぶ~」Zoomセミナー講座を開講中です

PR TIMES / 2024年11月22日 18時40分

-

【ライブ配信セミナー】半導体製造における後工程・実装・設計の基礎 12月12日(木)開催 主催:(株)シーエムシー・リサーチ

PR TIMES / 2024年11月20日 11時15分

-

液状封止材に関する特許維持が決定

PR TIMES / 2024年11月6日 15時45分

-

12月11日(水) AndTech「先端半導体デバイスにおけるCu/Low-k多層配線技術、および 2.5D/3Dデバイス集積化技術の基礎から最新動向と今後の課題」Zoomセミナー講座を開講予定

PR TIMES / 2024年10月29日 10時15分

ランキング

-

1クレジットカードを少額で不正利用されていない? 巧妙な新手口を解説

ITmedia エンタープライズ / 2024年11月26日 7時15分

-

2リンク付き投稿は拡散力減?イーロン氏明かすXルール 「告知投稿めっちゃ影響」不満も続々

J-CASTニュース / 2024年11月26日 17時11分

-

3『ドラクエ3』大魔王ゾーマ様、配信者になる―自己紹介では「嫌いなもの:ひかりのたま」とポロリ、「“ほりい”とかいう人間も泣き叫んでた」

インサイド / 2024年11月26日 13時10分

-

4オリエンタルランド、東京ディズニーリゾート販売の“3800円のマイボトル”回収 対象個数は4240個…… 「ご迷惑とご心配」

ねとらぼ / 2024年11月26日 17時12分

-

5アップル「iOS 19」SiriがChatGPTみたいになる?

ASCII.jp / 2024年11月26日 20時0分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください