RISC-Vの仕様策定からSiFiveの創業までAsanovic教授の足跡をたどる RISC-Vプロセッサー遍歴

ASCII.jp / 2023年10月30日 12時0分

RISC-Vプロセッサー遍歴シリーズは、前回から2ヵ月以上空いてしまったが、今回はそのRISC-Vプロセッサー遍歴の3回目をお届けしたい。

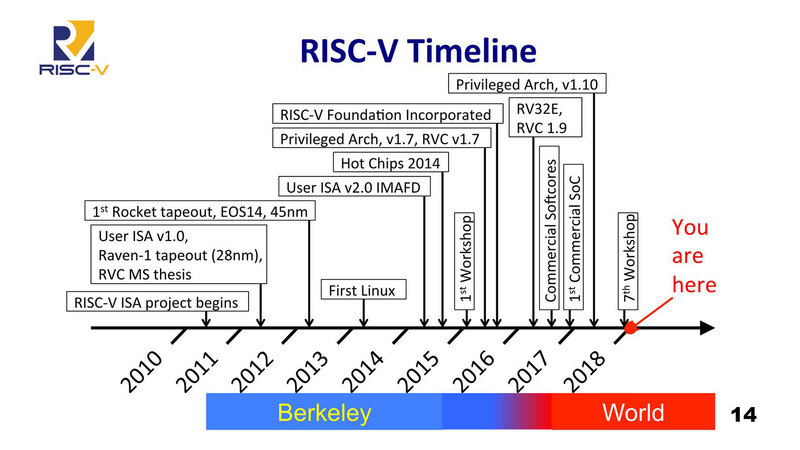

実はRISC-V ISAの基本的な仕様を定めた2011年から、RISC-V Foundationが立ち上がるとともRISC-Vプロセッサー遍歴にSiFiveが創業する2015年までの5年間、Asanović教授は相当忙しかったと想像される。下の画像が2018年までのRISC-Vのタイムラインである。

この時期Asanović教授は以下の業務に携わっていた。

本来の教授としての業務

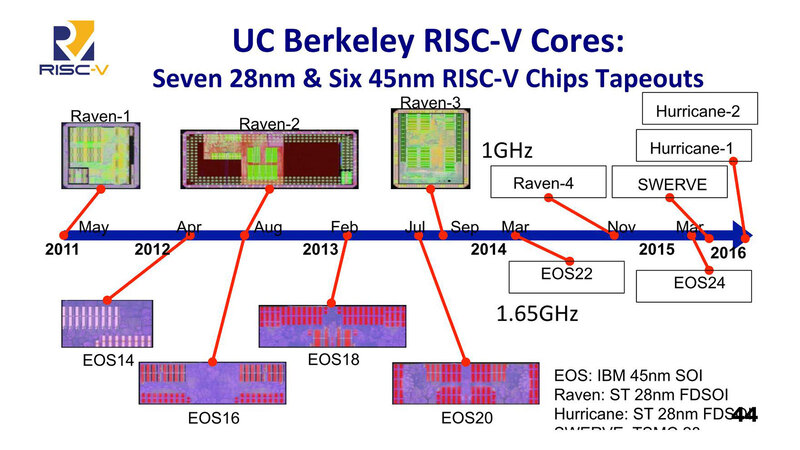

下の画像は、Raven-1以降にUC Berkeleyで開発されたさまざまなRISCプロセッサーの一覧である。

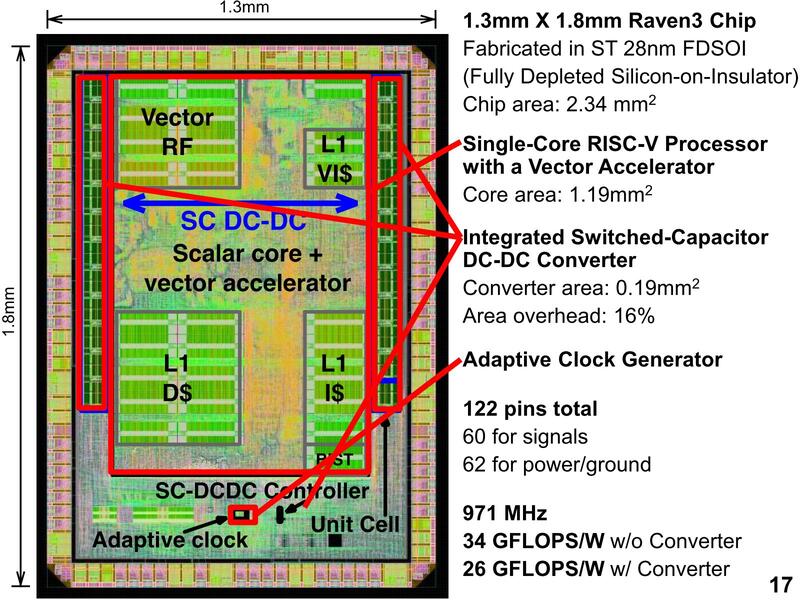

あくまでもこれはテープアウト、つまり物理設計を終わらせただけであってすべてのチップが実際に製造したわけではないし、ついでに言えばすべてにAsanović教授が関係しているわけではないが、ここのリストのRaven-3はAsanović教授の研究プロジェクトであり、実際にチップが製造され(製造はSTMicroelectronicsの28nm FD-SOI)、その特性を評価してHot Chips 27で発表もされれている。

ということは2015年くらいまで、Ravenを利用した研究がずっと行なわれていたわけで、当然このために相応の時間を割いているはずである。

RISC-V環境の充実

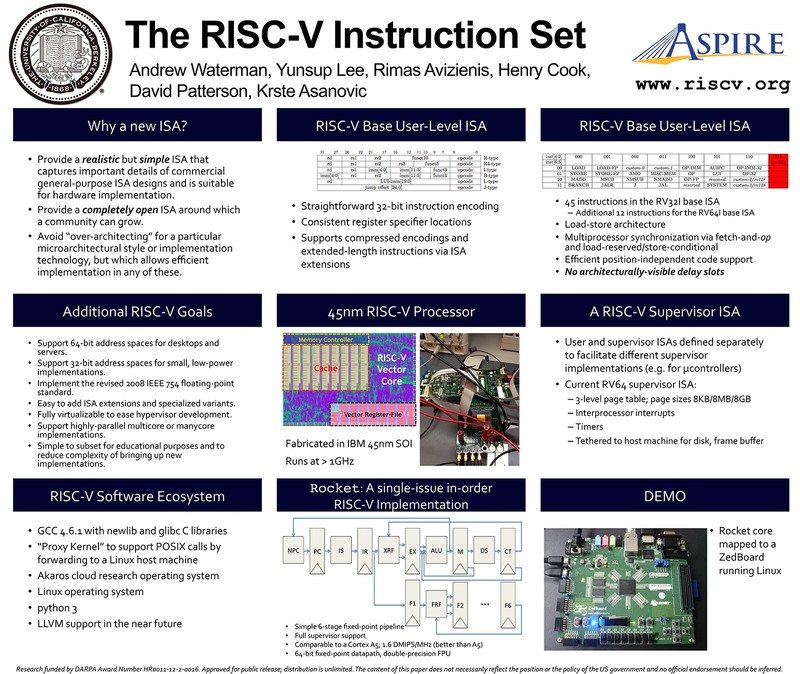

2014年までの間は、RISC-V ISAのブラッシュアップや「動くもの」の完成に注力することになる。実際基本的なISA(User ISA)は2011年中に完成し、2014年にはIMAFD(連載733回にあるスライドように、Standard Extentionの全部入り)まで定めたVersion 2.0がリリースされる。

ただこれはUser ISA、つまりアプリケーション向けの命令セットであり、これとは別にOSなどカーネルモードで動作する際に必要な特権命令(Privileged Arch)設置と縮小命令セット(RVC:RV Compressed)も2015年には完成している。

これに先立ち、Linuxの移植も始まっており、2013年中にはとりあえずブートするところまで完成している。この時のターゲットは、Raven-3の前段階の試作用で、ASICではなくFPGAボード上で動作していたコアのようだし、Linuxといってもとりあえずカーネルが動いたというレベルの話で、まだQEMUやブート用ファームウェアなどのビジネス用途に必要な環境がそろうには遠い状況ではあったが、とりあえず動作するOSが存在する、というのは重要なマイルストーンの1つを達成したことに間違いない。

単に「命令セットを定めました」だけでなく、「その命令セットを利用したプロセッサーが存在し、その上でLinuxも動きます」となると説得力が大幅に増す。というのは、性能やコストを現実的に算定できるベースができることになるからだ。

このコストに絡む話ではもう1つ、Chiselの存在がある。Raven-1の設計は、Verilogで行なわれていた。Verilogはこの連載でもちょくちょく名前が出てくる言語であるが、分類としてはHDL(Hardware Definition Language:ハードウェア記述言語)に属する。

Verilogは回路を設計するための「高級」言語である。なにをもって「高級」なのかは難しいが、CPUの世界で言えばC/C++やJava、今ならPythonなどが「高級」、アセンブラが「低級」になる。品質云々の高級/低級ではなく、抽象度が高いのが高級、ハードウェアに依存するのが低級と考えて欲しい。

HDLと対を成すのがRTL(Register Transfer Level)と呼ばれる記述法で、このRTLのデータを元にマスクが製造され、ファウンダリーで製造されることになる。さてRaven-1ではそんなわけでVerilogで直接CPU回路の記述がされていたが、Raven-2ではChiselと呼ばれる新しいツールが投入される。

Chiselは言ってみれば「Verilogにカバーを被せたもの」で、Scalaという言語を基にしたHDLではあるが、それでも基本的なコアをカスタマイズ(キャッシュやレジスターの容量、演算ユニットの数などを増減)して派生型を作る作業がVerilogを使うよりも非常に簡単になるというメリットもある。

さすがにVerilogを知らないエンジニアがChiselで直接CPUを構築するというのは無理があるが、Verilogに慣れたエンジニアであればCPUの構成を直接Verilogで記述するよりもずっと容易に構築できるようになった。このChiselは、その後SiFiveでも大活躍している。

なおRaven-3からはChisel2、Hurricane-2からはChisel3とより進化したChiselが利用されているほか、Raven-3からはBAG(Berkeley Analog Generator)、Hurricane-2からはBAG2と呼ばれるPythonで記述可能なアナログ回路生成用ツールが利用可能になり、2020年からはこれらを包括してハードウェアの上位設計からチップの物理設計までをまとめてハンドリングできるChipyardと呼ばれるツールも登場している。

こうしたツール群はもちろん徐々に整っていった格好なので2014年までの範囲であればいろいろ足りない部分はあったのだが、それでも他のCPUアーキテクチャーに比べると、RISC-VはCPUを設計するためのコストを低く抑えやすいという特徴が生まれることになった。

また記事冒頭の画像で2012年に“1st Rocket tapeout”とあるが、これはChiselの上で提供されるRocket Chipと呼ばれるCPUジェネレーターを利用したチップである。その下のUC Berkeleyで開発されたRISCプロセッサー一覧の画像でいえばEOS系列がこのRocket Chipをベースとしたコアとなっている。

Rocketそのものは5段のパイプラインを持つシングルイシューの比較的シンプルな構成のコアながら、RV32Gの命令セットに加え、マシンモード/スーパーバイザーモードなども搭載されており、ほぼRISC-Vコアの基本ともいうべきものになっている。このRocketコアに周辺回路のIPまでまとめた物がRocket-Chipであり、これはBSDライセンスで提供されている。

このRocketを利用した商用製品は多い(そもそもSiFiveの最初の評価ボードであるHiFive 1に搭載されたEF310というSoCも、このRocketベースである)。BSDライセンスなので、もちろんSiFive以外のベンダーもこれを自由に利用可能である。

これに引き続き、アウト・オブ・オーダー構成をもつBoomという実装の開発も始まっているが、こちらは登場するのはもう少し後の話である。ただこんな具合に、さまざまなRISC-Vを現実するためのプロジェクトも、研究と同時に走っていたわけだ。

RISC-V Foundationの立ち上げ

いくらAsanović教授が優れた命令セットを策定したと言っても、そのままではUC Berkeley以外では誰も使ってくれない。業界を巻き込んで広範に利用してもらうためには、そうした働きかけをする場所が必要である。

といってもまずは“RISC-Vとはなにか?”を知ってもらう必要がある。まず2013年7月にRISC-Vのウェブサイトが立ち上げられた「らしい」。らしい、というのは2013年7月にブログのエントリーがあったらしい形跡はあるのだが、すでに消えているためだ。2014年3月付のRISC-Vのページを見ると、2013年7月26日にドラフトのウェブサイトが立ち上げられたとしている。8月13日にはISA Specification 1.999が公開。2013年8月のHotChips 25ではポスター展示もされている。

2014年に入るとしばらくは先に書いた「RISC-V環境の充実」に注力することになるが、そうした中で水面下でRISC-V Foundation結成に向けてメンバー集めをしていた気配がある。というのは2014年の時点ではRISC-V関連のプロジェクトを進めるにあたり、かなり軍関係からの資金援助を受けている。

公開されているだけで、DoE Isis Project、DARPA PERFECT program、DARPA POEM programの3つからの資金援助があったほか、C-FAR(STARnet Center for Future Architectures)やLBNL(Lawrence Berkeley National Laboratory)といった組織からの資金も入っている。

加えて業界スポンサーとしてGoogle、Huawei、Intel、LG、Microsoft、NEC、Nokia、NVIDIA、Oracle、Samsungといった企業からの資金も入っており、こうしたスポンサー企業のいくらかはそのままRISC-V Foundation設立にあたりファウンダーメンバーになった。実はこの当初の軍関係からの資金援助、というのが今になって火種になっているのだが、その話はまたいずれ。

2015年に入ると、こうした活動の結果としてRISC-V Foundationが8月5日に結成される。もっともこの時点での説明はこんな感じで、体裁もなにもない。なにせトップページにRISC-V Foundationの名前が出てきたのは2016年2月16日のことである。

要するにいろいろと作業が間に合っていなかったのだと思う。ただそういう体裁はともかく、2015年にRISC-V Foundationが設立されたことで、明確にRISC-Vの普及に向けてのトラクションがかった格好だ。

SiFiveの立ち上げ

このRISC-V Foundationの立ち上げとほぼ並行して行なっていたのが、RISC-Vコアの商用販売を目的としたSiFiveである。創業メンバーはAsanović教授のほかにYunsup Lee博士とAndrew Waterman博士の2人だが、要するにLee博士とWaterman博士はAsanović教授の元で研究をしていたUC Berkeleyの学生であり、Raven-1以降のチップの開発などにも携わってきていた。

したがってRISC-V Foundationの立ち上げにも関係しており、実際Lee博士はついこの前まではRISC-V FoundationのTechnical Steering Committeeの議長を務めていたし、Waterman博士はPrivileged Architecture Task Groupの議長を現在も務めている。こうした活動と並行して、SiFiveを立ち上げたわけだ。

Asanović教授一人ではないとはいえ、よくこれだけの活動を2015年までの間にこなせたな、とは思う。こうした超人的な活動の成果として、2015年にはRISC-Vを広めるための器が形成され、2016年からはその成果が次第に出始めることになる。

この記事に関連するニュース

-

吉川明日論の半導体放談 第307回 米中関係で注目されるHygonのx86プロセッサー

マイナビニュース / 2024年7月5日 13時35分

-

リブランドした「Intel Xeon 6」はどんなCPU? Intelの解説から分かったことを改めてチェック

ITmedia PC USER / 2024年7月2日 16時5分

-

Intel Tech Talkで見えたLunar Lakeにおける低消費電力と高性能の両立へのこだわり

マイナビニュース / 2024年6月27日 6時45分

-

インテルが「Lunar Lake」のチップ実物を披露 実は現行「Core Ultra」の直接後継ではない その理由は?

ITmedia PC USER / 2024年6月26日 20時55分

-

RISC-V搭載ノートPCが登場、モジュール式ノートPCの米Frameworkから

マイナビニュース / 2024年6月19日 15時54分

ランキング

-

1「どう見てもセガのアレ」 コンビニうどんの容器トレーが「圧倒的既視感」「コントローラーの抜け殻」と話題

ねとらぼ / 2024年7月7日 17時0分

-

2「静岡40度」がトレンド入り「まだ梅雨明け前だってのに…」「そんな暑くなるところだっけ?」「酷暑日って初めて聞いた」

iza(イザ!) / 2024年7月7日 16時6分

-

3モトローラが日本市場で急成長している理由 1年で出荷台数2倍以上、「edge」「razr」の販路拡大がカギに

ITmedia Mobile / 2024年7月6日 11時45分

-

4「わろてる」 人気VTuberが部屋で“でかめのやらかし”をした様子を公開し話題に 「どうなってんのこれw」「想像以上」

ねとらぼ / 2024年7月7日 18時0分

-

5『ドラクエ』苦労して入手したのにガッカリ! 残念すぎた装備たち リメイク版で劣化も?

マグミクス / 2024年7月7日 15時25分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください