41社でRISC-V財団を創立 RISC-Vプロセッサー遍歴

ASCII.jp / 2023年11月6日 12時0分

RISC-V財団の創立メンバーは41社 活動資金を自前でまかなえる規模

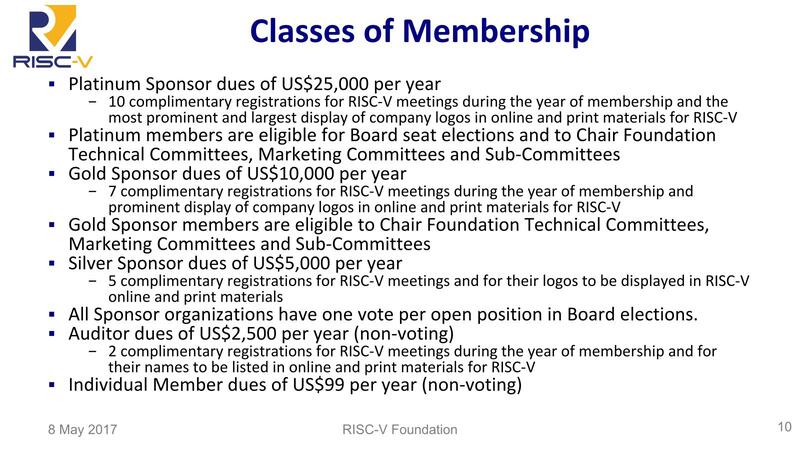

前回の続きとなる、RISC-Vプロセッサー遍歴の4回目をお届けしよう。2016年に入ると、RISC-Vの普及は加速していく。そもそもRISC-V Foundation(財団)の創立時点では、4種類(Platinum/Gold/Silver/Audit)+1(Funding)のレベルがあった。Platinum~Auditの各レベルの説明は下の画像になるが、要するに毎年2万5000ドル支払えばプラチナスポンサーとして取締役会に参加できるし、1万ドル支払えばゴールドスポンサーとなり、委員会の議長に就くことが可能である。年間5000ドルのシルバースポンサーではミーティングへの参加資格が得られる。PCI-SIGなどとよく似た、わりと一般的なシステムである。

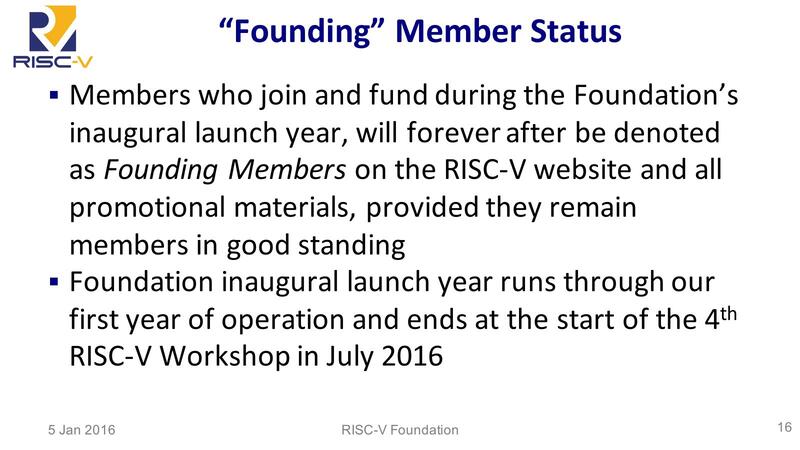

これとは別にFounding Memberという「ステータス」があるのだが、これは2016年7月までに出資した企業に与えられるもので、レベルは必ずしもプラチナである必要はない。

実際2016年11月のMember Directoryを見ると、41社がFounding Memberであることが示されており、例えば台湾のAndes Technologiesは2016年7月時点ではFounding Memberであるものの、Silverでしかない。ちなみに41社を並べると下表のようになっている。

この時点でインテルこそ名前を連ねていないものの、AMDやIBM、Qualcomm、NVIDIAなどのCPUメーカーに加え、Googleやマイクロソフトなどのソフトウェアベンダー、MellanoxやWD、IDTなどのメーカーまで参画しているのは、少なくとも第一歩としては大成功として良いと思う。またFounder Member以外でもMicronやNXPがともにプラチナで入っており、RISC-V Foundationの活動資金を自前でまかなえる目途が立ったことも大きい。

メンバーの中で、わりと初期から前向きになっていたのがNVIDIAとMicrosemi、WDといった独自のASICを製造する企業(これらの企業は自社製品の組み込み用にRISC-Vを利用するつもりだった)と、そのASIC向けのプロセッサーコアを提供するメーカーだった。

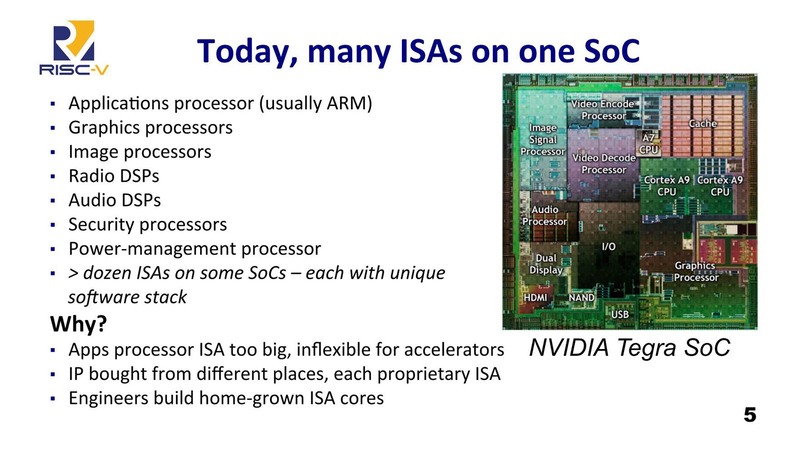

一番最初にRISC-Vが目指した市場は、ASICの組み込み用だった。下の画像はこれを端的に示したものだが、例えばNVIDIAのTegra SoCではCPUコアはCortex-A9で、これにNVIDIAのGPUコアを組み合わせたものである。ただそれ以外に多数の機能ブロックが存在する。

Tegraの場合でもISPやWi-Fiなどの無線系、オーディオ、セキュリティー、パワーマネジメント、画面出力など多数のブロックが存在するわけだが、だいたいにおいてこういう機能ブロックには「1つ以上の」プロセッサーコアが搭載されている。

上の画像で言えば、NANDのコントローラーには、NANDのアクセスやエラー訂正/ブロック代替処理、ランダムアクセスをブロックアクセスに変換などさまざまな機能が要求される。もう少し後の時代になると、このあたりを全部フラッシュメモリー側でハンドリングするUFSストレージが出てくることで処理が楽になるが、この当時はまだUFSが存在しておらず、SoC側で全部ハンドリングする必要があった。

当然このフラッシュの制御のためには、相応の性能のCPUが必要である。ここをケチると処理が間に合わないから、フラッシュのアクセス速度が全体的に低下することになる。これは他のブロックも全部同じことであって、機能ブロックのCPUには次の特徴がある。

機能ブロックCPUの特徴1 拡張性はなくてもいい

NANDならNAND、Wi-FiならWi-Fiの制御や通信が間に合えば問題ない。より高速な規格などが出てきたとしても、ハードウェアがそのままで対応できるケースは非常に限られるので、仮に新規格の対応が必要になるとブロックの置き換えになる。逆に言えば後から高性能化や高機能化が要求されるケースは基本考慮の必要がない。

機能ブロックCPUの特徴2 互換性も無視できる

こうした機能ブロックに搭載されるCPUは、アプリケーションプログラマーやユーザーには開放されない。その機能ブロックに搭載されたプログラムを実行するだけである。なので、ISAの互換性はなくても構わない。あくまでその機能ブロックを開発するベンダーがプログラミングできれば十分だからだ。

機能ブロックCPUの特徴3 高効率であること

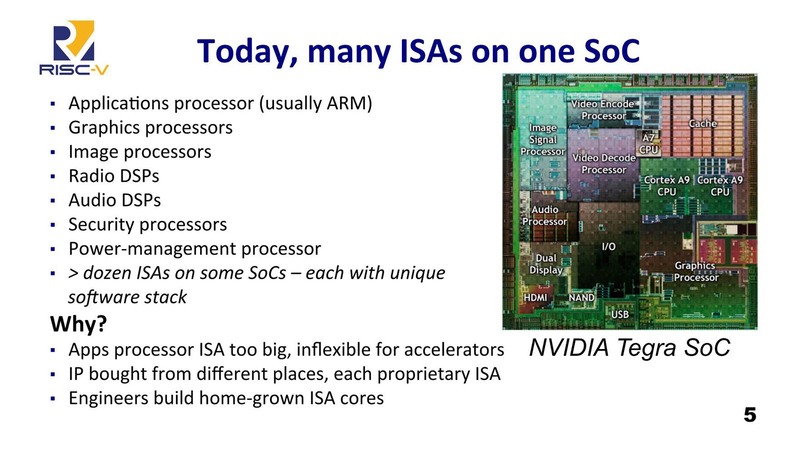

上にも書いたように、処理性能は相応に高い必要がある。ただし「高ければいい」というわけではない。ブロックに組み込まれるわけなので、あまり巨大なエリアサイズを食うようなプロセッサーでは困ってしまう。下の画像で見ると、Cortex-A9に比べると、制御用のCortex-A7(“A7 CPU”というブロック)はかなりコンパクトだが、それでもUSBの制御ブロックと同じくらいのサイズがある。

ということは、仮にUSBの制御用にCortex-A7を使うと、USBブロックのサイズが倍になってしまうことになる。これはいくらなんでも許容できないだろう。したがって、制御ブロック用のプロセッサーはなるべく小さな回路サイズで収まることが望ましい。それでいて、先に述べたように性能は相応に必要だが、そのために消費電力が増えることは許容されにくい。

汎用プロセッサーでは、性能を上げるためには動作周波数を引き上げるのが早道で、消費電力を抑えながら動作周波数を引き上げるためにプロセスを微細化するという方策がとられることが多いが、ASICに搭載される機能ブロックではそもそも利用するプロセスはASICの設計に依存するので、ある機能ブロックの要望に合わせて微細化したプロセスを採用するわけにはいかない。となると、どんなプロセスであっても相応の性能が出せる&消費電力を増やさないためには、CPUコアが高効率である必要がある。

機能ブロックCPUの特徴4 低価格に抑えること

これは高効率ともつながる話であるが、機能ブロックは通常外部のIPベンダーがASICベンダーに売る形になる。Tegra SoCにしても、この回路全部を自社で開発していたら、設計の手間が猛烈にかかってしまうし、NVIDIAにしてもすべての分野に十分な知見があるわけではない。

例えばNANDフラッシュにしてもラジオにしても標準的な規格であるから「それがないと話にはならない」が、「差別化要因にはならない」。自動車の窓の開閉機構がないのは普通に不便(レースカーくらいのものだろう)だから、窓が開かない自動車は普通選ばれないが、窓が開いたからといって別に差別化はできない。「できて当たり前」だからだ。これと同じような扱いである。

したがって、機能ブロックを販売するベンダーとしては、なるべく価格を抑えて提供するようにしたい。このためには、販売価格そのものもさることながら、そのブロックを顧客が自社のASICに組み込む際に、なるべく小さな面積で収まるように工夫する必要がある。大容量のキャッシュなどを必要とするCPUコアは、その時点で機能ブロックに組み込むには不適当である(SRAMは非常に面積が大きくなる)。

この結果として、機能ブロックにはさまざまなベンダーが提供するCPUが入り乱れ、それらは必ずしも標準的なコアではないものが多かった。

機能ブロックCPUの特徴5 標準的なコアはISAが複雑すぎる

x86もArmもそうだが、命令数はかなり多い。MCU向けのCortex-Mはアプリケーション向けのCortex-Aに比べたらだいぶ命令数は少ないものの、汎用という縛りもあり、基本命令だけで113個。これに加えてアクセラレーター(FPU/DSP)命令まである。

問題は、機能ブロックに使うCPUでこの命令を全部サポートする必要があるか? である。答えは否で、互換性はそもそも必要ないから「機能ブロックで使う一部の命令だけをサポート」するようにしたい。しかしこれはx86にせよArmにせよ、許されない(昔のPowerPCなども同じであった)。これを許すと互換性がなくなってしまうからだ。

そして多すぎる命令は実装の負荷がかかる。命令デコードをハードワイヤードで実装していれば、その分回路が複雑になるし、マイクロコードであればマイクロコードROMの容量が増え、どちらにせよ回路の面積増大につながる。これはコスト削減には好ましくない。

機能ブロックCPUの特徴6 勝手に命令を増やせない

逆に機能ブロックを構成する際に、アクセラレーターを簡単にアクセスできるような命令を追加したいと思っても、これまた互換性を保つ観点から許されない。Armは2019年になってやっと、Cortex-M用のArm v8-MにCustom Instruction Extensionと呼ばれる機能を追加。16命令までの独自命令がサポートされるようになったが、それまでは一切独自に命令を増やせなかった。

機能ブロックCPUの特徴7 ロイヤリティーが安くない

x86はそもそも論外として、Armの場合はまずそのコアを採用する際にライセンスを取得(これも決して安くない)したうえで、そのコアを使って量産に入る場合、利用するコアの数に応じてロイヤリティーを支払う必要がある。

これはASICコアに組み込む場合も同じで、契約の形態に応じていろいろ支払い方法はあるようだが、一般には機能ブロックを提供するベンダーではなく、そのASICを製造するメーカーがArmと契約を結んで、コアの数にあわせたロイヤリティーをArmに支払う必要がある。このロイヤリティーがArmの大きな収入源であるわけで、逆に言えばそれだけ機能ブロックのコストが上がることになる。

メンバーはハードウェアよりも ソフトウェアエコシステムの発展に期待

以上が機能ブロックCPUの特徴だ。こうなると、アプリケーションプロセッサーともかくとして、機能ブロックに組み込むCPUにArmコアを搭載するのはコストパフォーマンスが悪い選択肢になる。

先のFounder企業の中で、台湾のAndes Technology、フランスのCortus、チェコのCodasip、ロシアのSyntacoreなどはいずれもこうした、非Armの独自コアをASICの機能ブロックの組み込み向けなどに向けて提供していたベンダーである。これらのベンダーが提供するコアは命令のカスタマイズや拡張が自由に行なえ、ライセンスやロイヤリティーに関しても柔軟性があり、用途によってはArmコアより高効率であることを特徴としていた。

ただしその反面ソフトウェアのサポートなどはあまり十分ではなく、GNUのToolchainとLinux Kernelが提供される程度。中にはRTOSのサポートが用意されるものがあったが、ラフに言えば機能ブロックを提供するベンダーには必要十分というレベルで、一般に広く使うには足りないものがかなりある、といった感じの状況だった。

こうしたベンダーが一斉にRISC-V FoundationのFounding Memberに名前を連ねた、というのは要するにハードウェアよりもソフトウェアエコシステムの発展に期待をしたから、という話である(続く)。

この記事に関連するニュース

-

吉川明日論の半導体放談 第307回 米中関係で注目されるHygonのx86プロセッサー

マイナビニュース / 2024年7月5日 13時35分

-

Intel Tech Talkで見えたLunar Lakeにおける低消費電力と高性能の両立へのこだわり

マイナビニュース / 2024年6月27日 6時45分

-

Copilot+ PCをいち早く体験!洗練されたデザインのノートパソコン「ASUS Vivobook S 15 S5507QA」レビュー

ITライフハック / 2024年6月25日 23時59分

-

Copilot+ PCをいち早く体験! 洗練されたデザインのノートパソコン「ASUS Vivobook S 15 S5507QA」レビュー

ITライフハック / 2024年6月25日 23時59分

-

「Copilot+ PC」って何だ!? 「AI PC」は早くも第2世代へ

ITmedia PC USER / 2024年6月18日 6時0分

ランキング

-

13月末にコンビ解散したお笑い芸人、「また美人になった?」「見るたびにキレイになってく」と反響

ねとらぼ / 2024年7月5日 18時37分

-

2「静岡40度」がトレンド入り「まだ梅雨明け前だってのに…」「そんな暑くなるところだっけ?」「酷暑日って初めて聞いた」

iza(イザ!) / 2024年7月7日 16時6分

-

3Ryzen 5 8600Gを標準搭載する1.92LのBTO PC、超小型PCの決定版になりそう

ASCII.jp / 2024年7月7日 10時0分

-

4格安SIMでIPv6が使えると何かいいことがあるのか?

ASCII.jp / 2024年7月7日 12時0分

-

5「どう見てもセガのアレ」 コンビニうどんの容器トレーが「圧倒的既視感」「コントローラーの抜け殻」と話題

ねとらぼ / 2024年7月7日 17時0分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください