早いペースで新コアIPを発表してRISC-Vを広めたSiFive RISC-Vプロセッサー遍歴

ASCII.jp / 2023年12月4日 12時0分

今週のRISC-Vプロセッサー遍歴は、話を2020年頃に戻す。連載744回で触れた「RISC-Vに前のめりだった第1グループ」であるファブレスCPU IPベンダーはどんどん製品投入を開始している。わかりやすい例はSiFiveであろう。

CPU IPの提供だけでなくSoC全体の設計まで手がけるSiFive

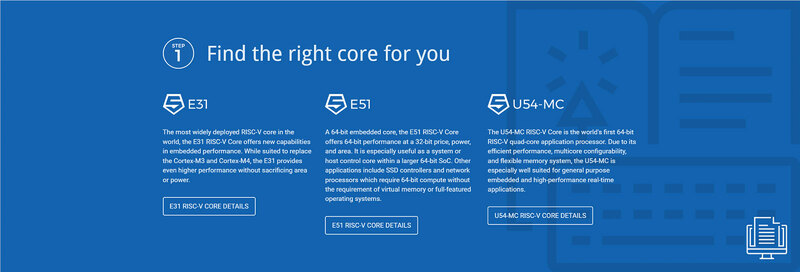

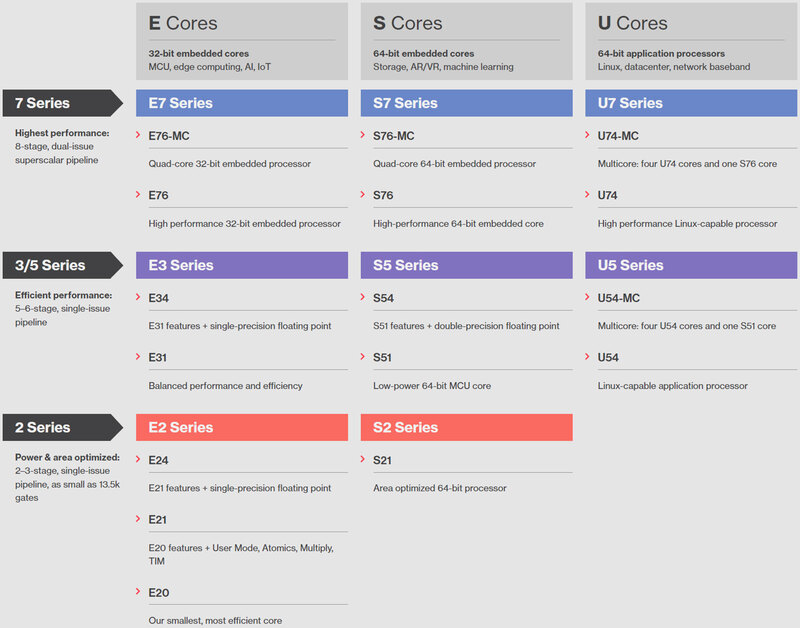

SiFiveの2017年10月における製品ラインナップが下の画像である。

E31は32bitのMCU向けで、競合製品はCortex-M3やM4とされ、シングルイシューのパイプライン構成ながら1.5 DMIPS/MHz(Cortex-M3/M4は1.25 DMIPS/MHz)の性能であり、28nmプロセスなら最大1.5GHzで動作するとされている。

もちろんこんなスピードで動かしたら普通はフラッシュメモリーが全然間に合わないので、実際にはもっと遅い周波数で動かすわけだが、逆に言えば28nmで1.5GHzということは90nmあたりでも数百MHzで十分回るわけで、これは高性能なMCUコアとして使うには十分である。

E51はE31を64bit対応にしただけという感じで、MMUもないので(PMP:Physical Memory Protectionユニットはあるが、これは俗にいうMPUである)、Linuxなども動かない。これはASIC内部のコントローラー向けといった扱いである。

この上位に来るのがU54-MCであるが、こちらはCortex-A53にもおよばない程度の性能でしかなく、アプリケーションプロセッサーとして使うには厳しい。ただソフトウェア開発用のプラットフォームとしては十分であり、とりあえずCPU IPベンダーとしての体裁が整ったという程度である。

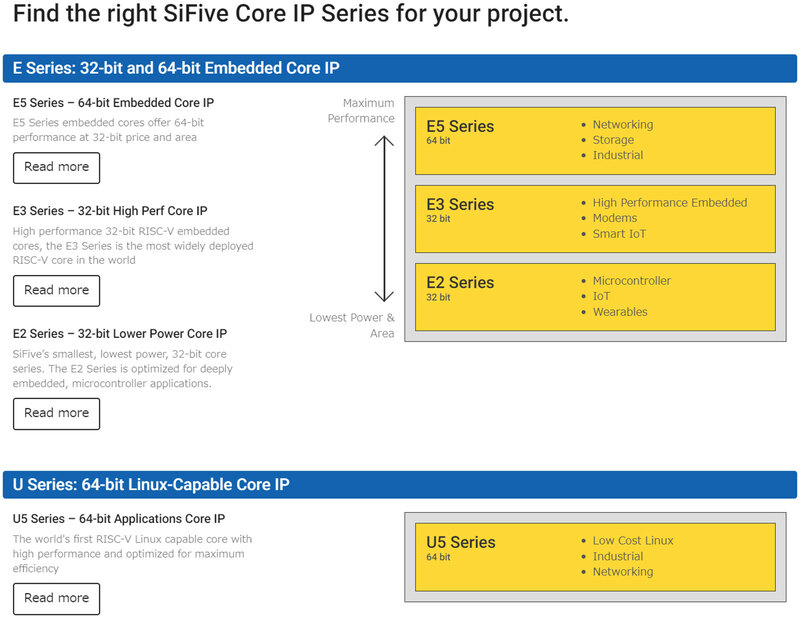

これが2018年になると、ローエンドにE2シリーズが追加される。

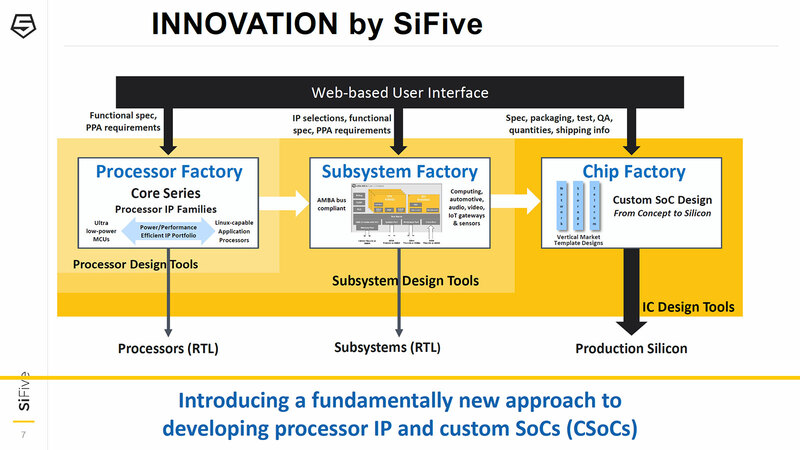

ちなみにこの時期、SiFiveは単にCPU IPのみならず、SoC全体を構築できるようなソリューションを提供している。というのは、SiFiveは2017年8月にOpen-Siliconという独立系のデザインハウス(ASICの設計を専門にした企業。顧客が論理設計を行なったチップの物理設計を担当したり、論理設計から物理設計まで担当して、テープアウトまで面倒を見たりする)を買収したことで、CPU IPの提供だけでなくSoC全体の設計まで手がけられるようになったからだ。

この時期SiFiveは“Processor Factory”、“Subsystem Factory”、“Chip Factory”という形で、単にCPU IPだけでなくCPUを含んだサブシステムの提供、あるいは最終的にASICそのものの製造まで意図していた。

結果から言えばこの試みは時期尚早であり、2020年にこのOpen-Siliconの舞台はOpenFiveとしてSiFiveの子会社の形で独立して動くことになり、2022年9月に英Alphawave IPに売却されることになった。

この手のサービスの場合、Armはデザインパートナーと呼ばれる認定を受けたデザインハウスが担っているが、SiFiveにはこうしたパートナーとなるデザインハウスが存在しない。したがって自前で抱え込もう、というのがそもそも上の画像の目論見だったように思う。

ただそのためには、顧客が使いたいと思うような魅力あるCPU IPが大前提であり、残念ながら当時のSiFiveのコアはそこまで魅力的と言えるほどではなかった。

結局のところOpen-Silicon部門は単独でもビジネスが成立する状態だったのに、SiFiveと組み合わせたことでビジネスが先細りになってしまったので、分離して運営(つまりArmなどをベースにしたASICの設計も担えるようにする)する形となり、こうなるとSiFiveが子会社として保持する意味がないので売却してしまった、というあたりだろう。

話を戻すと、E3コアは性能がそれなりにあり、性能/面積比や性能/消費電力比も良好と言っても、世の中にはそこまでの性能が要らないからもっと小さい回路規模で、というニーズが一定量存在する。Armで言えば、Cortex-M0やCortex-M0+、Cortex-M23あたりに該当するコアである。

2段のパイプライン構成ながら1.77 DMIPS/MHzと動作周波数あたりの性能はE30シリーズよりも若干上である。もっともその分動作周波数はあまり上げられないという制約は付くのだが。

S5シリーズと7シリーズが追加

2019年に入ると、ラインナップにS5シリーズが追加される。

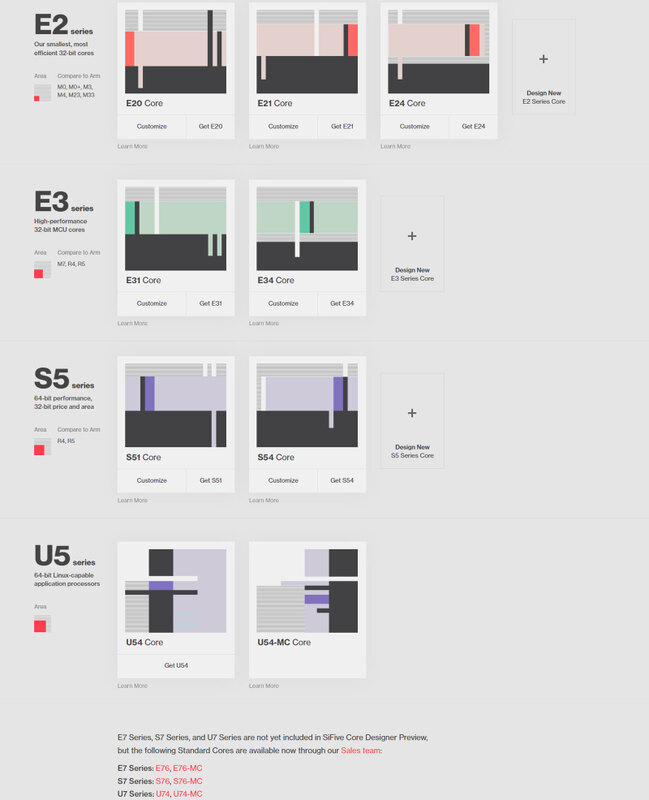

厳密に言えばこれは新製品の追加というよりもリブランドというべきで、これまで組み込み向けとされていたEシリーズとアプリケーションプロセッサー向けとされていたUシリーズを、新たにE/S/Uの3つに再編。E5はそのままS5にシフトした格好だ。その意味では何も変わっていないと言えなくもないが、S54やE24など細かく製品が追加され、だいぶCPU IPベンダーらしい品ぞろえになってきた。

2020年になり、ここで初めて7シリーズが追加になった。

こういうマトリックス構造にするとわかりやすいが、実はE/S/Uのコアは基本的に同じで、Eは32bit命令のみ、Sは32/64bitの両対応、UはSにOSが動くためのサポートメカニズム(仮想記憶のサポートや、このために必要なMMUの実装など)を追加しただけである。

一方で2/3・5/7は内部構造で、2は2~3ステージの短い命令パイプラインで、性能よりも省電力性や省面積(というか省回路規模)を優先したもの。3・5はシングルイシューのパイプラインながら、5~6ステージとすることで動作周波数を引き上げやすい構造にしたもの。7がデュアルイシューのスーパースカラー(ただしインオーダー)構成で、より動作周波数を引き上げやすくするとともに性能向上を狙ったシリーズとなる。

この結果、Cortex-M7クラスに匹敵するE7シリーズやCortex-R5/7に相当するS7シリーズ、またアプリケーションプロセッサーとしてもCortex-A53クラスの性能に相当するU7シリーズなどがラインナップされたことで、だいぶ製品が充実するようになった。

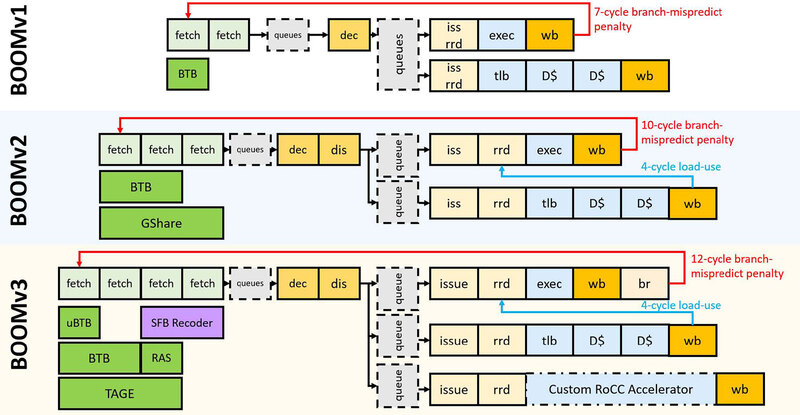

スーパースカラーを支えるBOOMコア (Berkeley Out-of Order Machine)

RISC-Vのスーパースカラーコアそのものは、連載743回でも少し言及したBoomと呼ばれるコアが存在する。これもv1~v3があり、Boom v1は性能重視ながら動作周波数が上がらず、これを解決した(パイプライン段数が3段増えている)のがBoom v2である。Boom v3はさらに高速化を目指し、ついでに性能改善も狙ったものだ。

簡単にまとめると、以下のようになる。

Boom v2はBoom v1よりもやや性能が落ちるが、その分動作周波数を引き上げやすい構成になっている。Boom v1は2017年4月、v2は2017年8月に発表されており、v3は2020年5月なので、前掲の2020年1月の製品ラインナップには間に合わない。

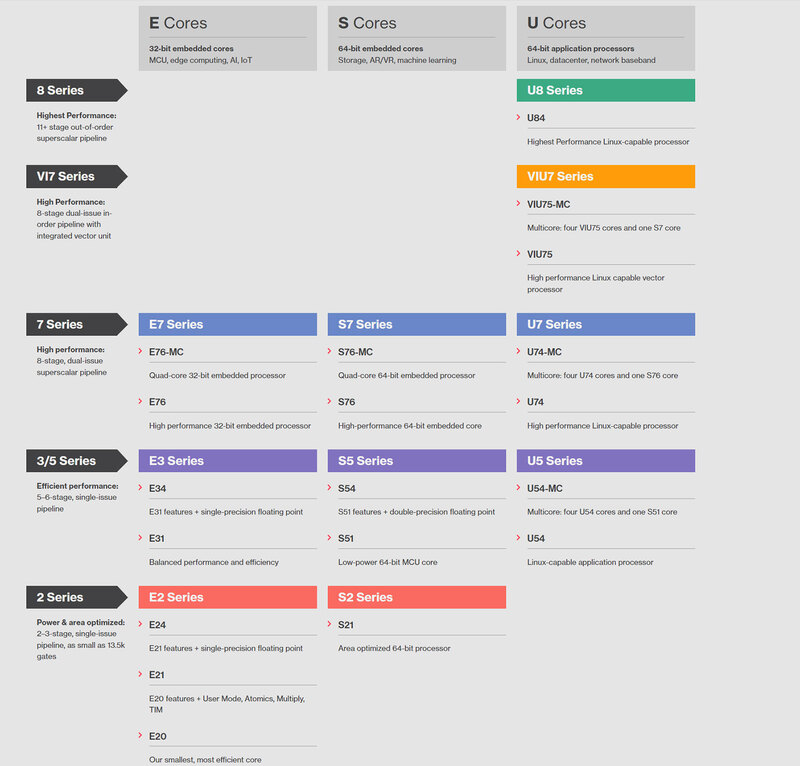

性能や回路規模を考えればおそらくはBoom v1をベースとしたものと考えられるが、それでもBoom v1の登場から3年弱を要したのは、単に忙しかった以上に商品化には相応の時間が必要だった、ということに思える。というのは、2020年8月には7シリーズの上のグレードで8シリーズが投入されているためだ。このU84はおそらくBoom v2ベースのものになっていると思われる。

ちなみにここまでのシリーズは、現在ではエッセンシャル・シリーズとしてまとめられており、今はこの上位にあたるパフォーマンス・ファミリーとベクターエンジンのみを提供するインテリジェンス・ファミリー、それと自動車向けのオートモーティブ・ファミリーが用意されている(U8はパフォーマンス・ファミリーにまとめられたようだ)。

やはりというべきか、当然というべきか、Armのハイエンドプロセッサーに相当するコアをいきなり投入するのは「普通」難易度が高い。

例外はTenstorrentで、Jim Keller氏がハイエンドプロセッサーコアの設計経験が豊富だったからこそ、Jim Keller氏の参画後にいきなりAscalonコア(それもいきなりトップエンドの8-wideデコーダーのコアを開発し、そこからカットダウンするかたちで6/4/3/2-wide デコーダーの派生型を作るという荒業を成し遂げた)を投入できたが、普通の設計者はまずシングルイシュー/インオーダーのコアを製品化し、これを売りながら改良型や派生型を開発、ラインナップを広げていく。

こうした流れで時間を稼ぎつつ、これと並行して高性能なコアを開発、より高い性能が求められるアプリケーションプロセッサーやサーバーの市場に殴り込みをかける。もちろんサーバーといってもクラウドサービスに使われるようなもの、つまりインテルのXeonやAMDのEPYC、あるいはArmのNeoverseを利用したAWSのGravitonシリーズのようなものにいきなり投入、というのは困難というよりも不可能であって、まずは小規模なエッジ・サーバー狙いということになる。

このあたりのストーリーはArmと同じで、2010年にCortex-A15を発表したときは、まず小規模なStatic Web ServiceとかCDN(Contents Deliver Network)などに採用事例を増やしていく見通しであった。

ArmがNeoverse N1を発表するのは2019年で、途中ソフトバンクによる買収などでエコシステムの充実が加速されたとはいえ9年を要していることを考えると、RISC-Vももちろんそう簡単にクラウドサーバーなどを含むハイエンドサーバー市場に参入はできないだろう。

ただ卵と鶏ではないが、とりあえずそうしたハイエンドサーバー市場にリーチできるような性能を持つプロセッサーIPコアがないと話にならないし、そうしたコアはサーバー以外にも例えば自動車向けなどでもニーズがあるから、高性能コアを用意するに越したことはない。ただ普通これには数年~10年くらいの時間がかかる。特に高性能コアの開発は、そのための開発費がシャレにならない。

高い資金力があるから 開発を急ピッチで進められる

SiFiveがこの短い期間で8シリーズやパフォーマンス・シリーズを投入できたのは、Boomシリーズという「元になるコア」があったことも大きいが、それよりもRISC-Vベンダーの中では群を抜いて資金力が高いことに起因する。

要するにファンドからの資金を潤沢に確保できているのが、開発を急ピッチで進められた最大の要因ではある。公開されている分だけで、2022年3月の時点で合計3億6600万ドルを調達しており、この資金調達は、やはりAsanović教授の存在がかなり大きかったはずだ。

ほかのベンダー、つまりAndes/Codasip/Cortus/TenstorrentなどもやはりRISC-Vプロセッサーを手がけていることが評価され、やはりファンドからの資金調達を行なってラインナップの拡充につとめている。それもあって、各社とも独自のコアを提供していた時に比べるとはるかに早いペースで新コアIPを発表するようになっている。

この記事に関連するニュース

-

Lunar LakeではPコアのハイパースレッディングを廃止 インテル CPUロードマップ

ASCII.jp / 2024年7月1日 18時0分

-

Intel Tech Talkで見えたLunar Lakeにおける低消費電力と高性能の両立へのこだわり

マイナビニュース / 2024年6月27日 6時45分

-

RISC-V搭載ノートPCが登場、モジュール式ノートPCの米Frameworkから

マイナビニュース / 2024年6月19日 15時54分

-

ASUSが放つ世界初の「Copilot+ PC」となる「Vivobook S 15」(S5507QA)を試す

ITmedia PC USER / 2024年6月18日 15時0分

-

GEEKOM Mini PC 21周年記念の新製品A8をご紹介

PR TIMES / 2024年6月18日 10時45分

ランキング

-

1「鳥肌たった」「これこそアート」 SNSで約13万いいねを集めた1枚のイラスト、衝撃の種明かしに反響 作者に制作経緯を聞いた

ねとらぼ / 2024年7月6日 12時30分

-

2「これはやばいw」 モスバーガーの“狂気のLINEスタンプ”が話題 公式も認める異様な絵面に「夢に出てきそう」

ねとらぼ / 2024年7月6日 17時0分

-

33月末にコンビ解散したお笑い芸人、「また美人になった?」「見るたびにキレイになってく」と反響

ねとらぼ / 2024年7月5日 18時37分

-

4「Pixel 6」シリーズに不具合、最新アプデ→初期化でトラブル発生 Googleが回避策を案内

ITmedia NEWS / 2024年7月5日 8時20分

-

5モトローラが日本市場で急成長している理由 1年で出荷台数2倍以上、「edge」「razr」の販路拡大がカギに

ITmedia Mobile / 2024年7月6日 11時45分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください