日本の半導体メーカーが開発協力に名乗りを上げた次世代Esperanto ET-SoC AIプロセッサーの昨今

ASCII.jp / 2024年6月3日 12時0分

Esperantoが日本の半導体メーカーRapidusと協力

5月15日、都内でRapidus(ラピダス)とEsperanto Technologyが共同で記者会見を開催、Esperanto Technologyの第3世代製品をRapidusの2nmプロセスを利用して製造することに関してのMOU(協力覚書)を交わしたことを明らかにした。

といってもまだMOUのレベルであって、具体的に契約が交わされたわけではない。そもそも現状ではまだRapidusの方が工場すらなく、サンプル品を作るどころかテストベッドすら走らせられない。

また製造装置すら確定していない状態ではPDK(Process Development Kit:チップの物理設計を行なう際に必要となるさまざまなパラメーターをまとめたもの)すら出せないから、Esperanto側としても物理設計を始めることすらできない。

この状態でさすがに契約というのは双方にとってハイリスクな行為であり、その前段階である協力覚書に留まるのは当然である。

それは良いとして、記者会見では2nmが主な話題であって深い話はなかったのだが、Esperanto Technologyは今年4月に東京大学で開催されたCool Chipsで第2および第3世代のET-SoCに関して同社創業者にしてCTOのDavid Ditzel氏が講演しており、ここで多少の説明をしている。今回の記者説明会にはもDitzel氏が同行しており、少し細かな話をうかがえたので、これをもとにET-SoC-2/ET-SoC-3の詳細を説明したい。

発端はRISC-VベースのAI向けプロセッサー「ET-SoC-1」 電圧を大幅に下げて性能/消費電力比を大きく向上させた野心作

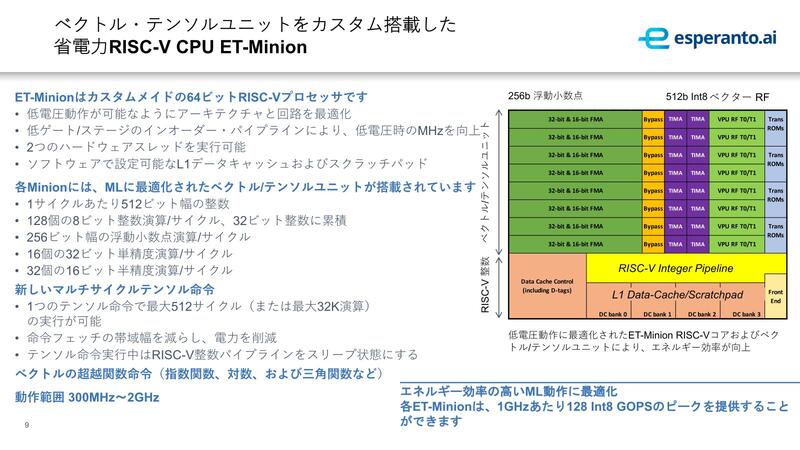

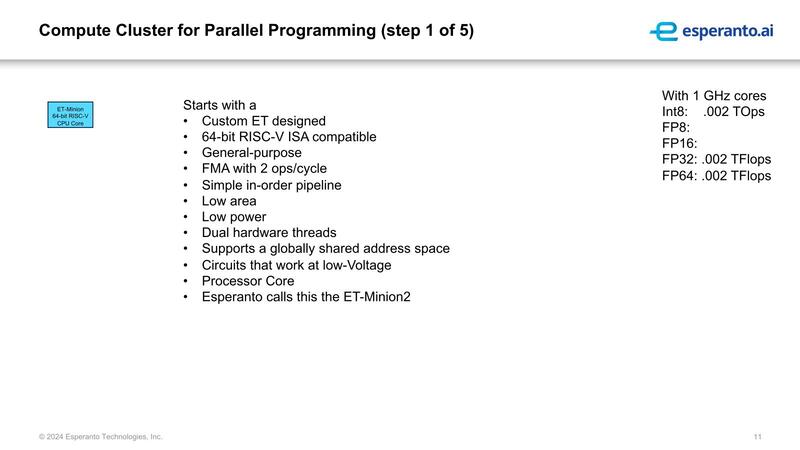

まずおさらいを。連載645回で説明したが、同社のET-SoC-1は、ET-Minionというコアが基本となる。ET-MinionはIn-OrderのRISC-Vコアに、512bit幅のVector/Tensor Unitをアクセラレーターの形で組み合わせたものだ。

このVector/Tensor Unitが肝であり、FP16なら32個、FP32なら16個の演算を1サイクルに実行可能である。またTensor Unitとして使う場合、最大512サイクル連続して稼働できる。

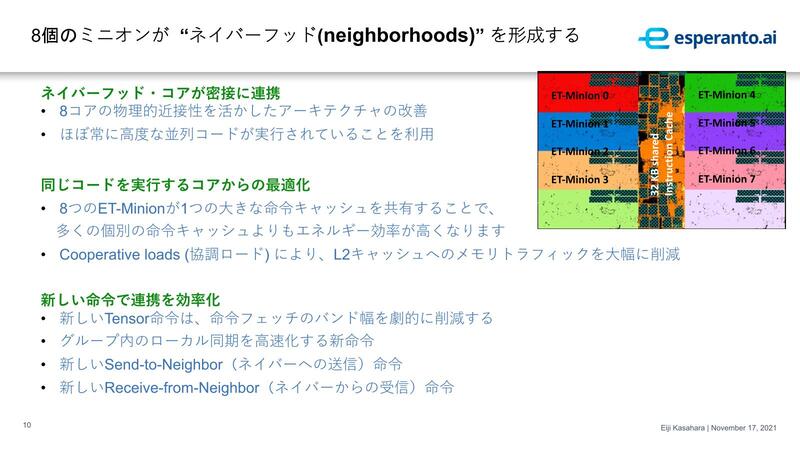

そして8つのET-MinionをまとめてNeighborhoodsを構成し、この8つのET-MinionでL1命令キャッシュを共有する。このNeighborがある意味、1つの処理単位と考えればいい。

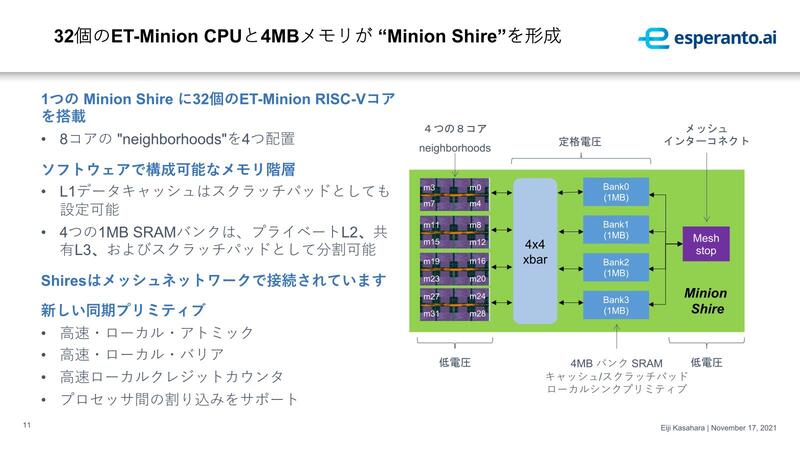

L1を共有というのは、8つのET-Minionコアが同じ命令を実行するから(データは異なる)である。Neighberhoodsを4つと、1MB×4のSRAMを組み合わせたものがMinion Shireとなり、CPU内のほかのMinion Shareとのメッシュ接続のI/Fもここに搭載される格好になる。このMinion Shareが事実上の最小構成というわけだ。

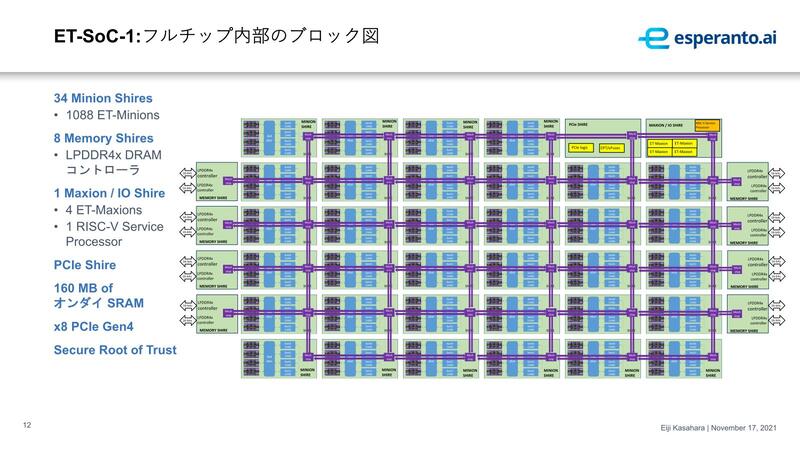

ET-SoC-1全体は、このMinion Shareを34個、それとアプリケーション/OS用のET-Maxion×4、さらにPCIeのブロックと8つのLPDDR4x I/F(各々32bit幅)から構成される格好になる。合計で1088個のET-Minionが搭載され、そのおのおのに512bit幅のVector/Tensor Unitが搭載される形になる。

厳密に言えば、他にもう一個RISC-V Service Processorがシステム全体の管理用に動作するが、これはアプリケーション側からは見えないようだ。

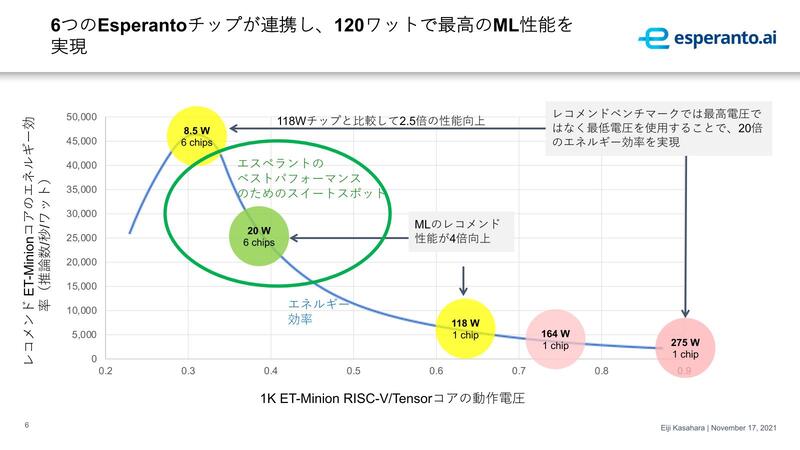

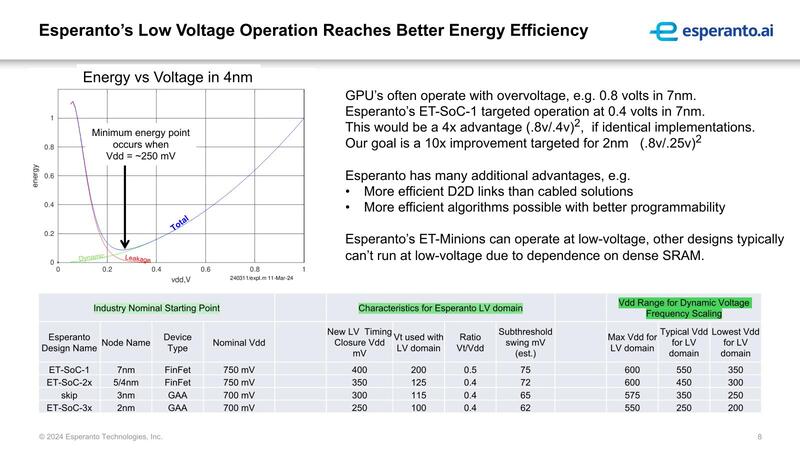

さて、ここまで言えば単にMassive Parallelの一種と見えなくもないET-SoC-1であるが、最大の特徴は電圧を大幅に下げて性能/消費電力比を大きく向上させていることだ。

今回はこの技術をELV(Extreme Low Voltage)と呼ぶようになったのだが、要するに通常よりも大幅に電圧を下げることで効率向上を図る、というものだ。ET-SoC-1の場合はおおむね以下の試算が成立する。

PCIeカード1枚の消費電力枠を120Wとすると、0.63V以上では1チップでカードの消費電力枠を使い切ってしまう。0.38Vでは6チップが搭載できて、トータルの性能が一番高い。ちなみに0.31V枠なら14個チップを搭載可能で、この場合は560万OPSが発揮できるはずだが、14個も1枚のカードに載せられないという物理的な障害があるため、そのあたりを勘案すると0.38V動作がちょうどいい、という判断らしい。

もちろん通常の7nm(TSMC N7)では、こんな低電圧での動作は不可能である。そのあたりがDitzel氏というかEsperantoのノウハウが一番生きる部分というわけだ。

ET-MinionがET-Minion 2に進化 性能が4倍向上する

ここまではET-SoC-1の話だったので、ここからはET-SoC-2以降の話を。まずET-Minionだが、こちらは若干変更したET-Minion 2に進化した。

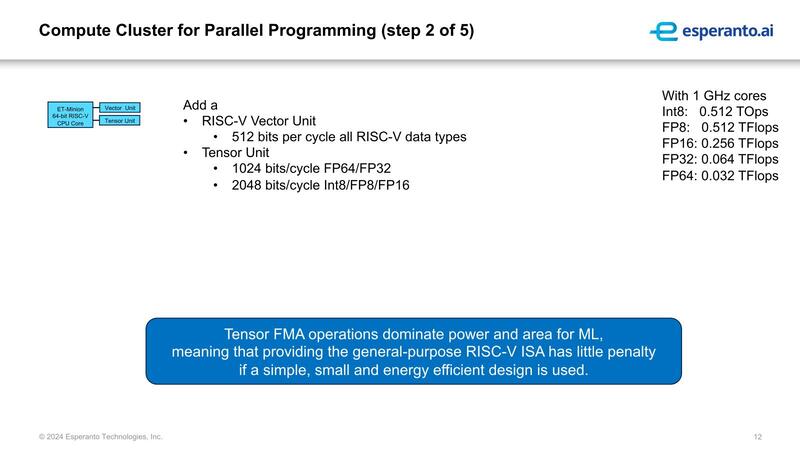

大きな変化は外付けのアクセラレータ-で、ET-Minionと異なりVector UnitとTensor Unitが独立。Vector UnitはRVV(RISC-V Vector Extension)準拠の512bit幅となった。一方Tensor Unitは2048bit幅に拡張された。

まず2つに分けた理由であるが、一応技術的には両方を同時に動かすことも可能らしい。ただ目的はそうではなく、Vector UnitはRISC-VのVector Registerに対してのアクセスとなり、一方Tensor Unitは独自の2048bit幅のRegisterのへのアクセスとなる関係で、構造的に分離した方が都合が良かったから、だそうである。

この結果として、例えばFP16やFP32であれば、ET-Minion比で4倍の性能向上が実現することになった。実際の動作周波数は後述する。ちなみにET-Minionでは最大512サイクル連続してTensor Unitが稼働するが、ET-Minion2はDitzel氏によると「512ではないが連続して稼働する。ただいくつだったか忘れた」だそうだ。

また、今回FP8までのサポートは追加されたが、FP4やInt 1/2/4に関するサポートはない。これについては「研究レベルではよく取り上げられるが、実際に使うユーザーからの声では、やはり精度が足りない」という判断だそうで、現実問題としてInt 8とFP8/FP16/32/64のサポートがあれば十分、ということだそうだ。

ET-Minion2が8つでNeighborhoodを構成するのは同じだそうである。このNeighborhoodがL1命令キャッシュを共有するのも同じという話であった。

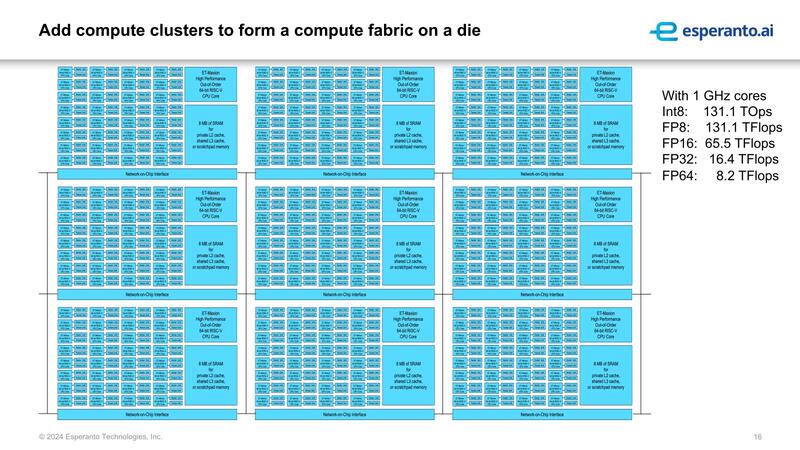

そのNeighborhoodが4つで、1つのクラスターを構成するのもET-SoC-1に似ているが、異なるのはこのクラスターに1つ、ET-Maxionが搭載されることと、またSRAMの容量が倍増していることだ。

ただSRAMに関しては、確かに容量は倍だが処理性能が4倍ほどに上がってることを考えると、実際には足りなくなるのでは? と思ったのだが、確認したところ「そもそもそのデータは処理中に何度も再利用するから不足はしない」という返事であった。実際には8MBといっても細かくパーティションを切って、L2やL3、さらにはスクラッチパッドとして使う形になるので、純粋に容量が増えて柔軟性が増すことになるそうだ。

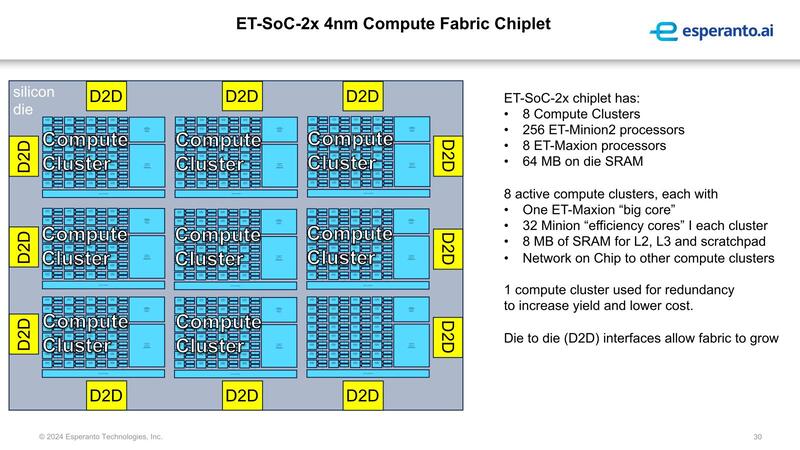

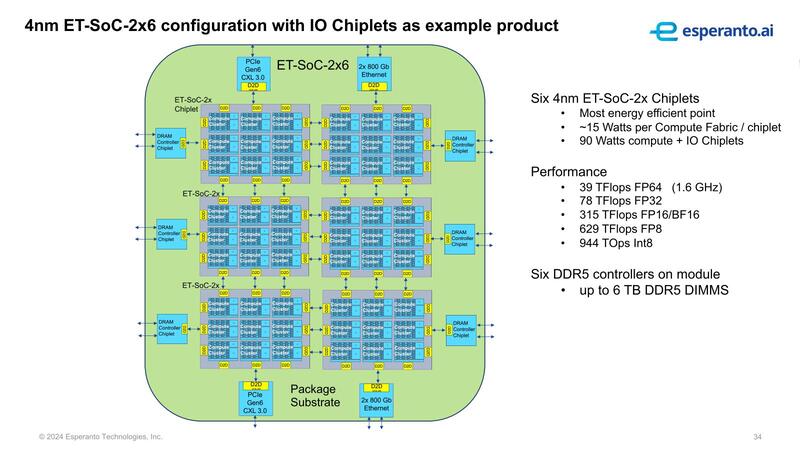

そしてET-SoC-2であるが、このクラスターを9個並べて1つのチップレットを構成する。9個にもかかわらず、性能は1GHzのInt 8で131.1TOPSと、1つのクラスター(16.384TOPS)の8倍でしかないのは、9つのクラスターのうち1つは冗長クラスター扱いとなるためだ。

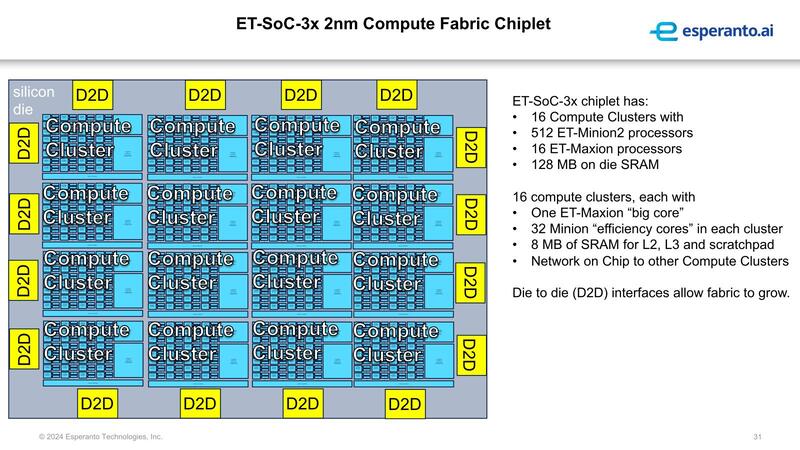

ちなみに後述するET-SoC-3では1つのチップレットにクラスターが16個であり、実際に16個となる。つまり性能はET-SoC-2の2倍だ。「なぜ?」と聞いたところ、「クラスターの数を2のべき乗にしたかったから」だそうだ。したがってET-SoC-2では9個のうち1つを冗長扱いにして8つとし、一方ET-SoC-3では16個は変えずに冗長性は他のスキームで確保するという返事であった。おそらく個々のクラスター内部に冗長Neighborhoodあるいは冗長ET-Minion2を設ける格好だろう。

ET-SoC-2は予定通りなら2025年後半にサンプル出荷開始 次世代のET-SoC-3は2026年後半出荷とのことだが間に合うのか?

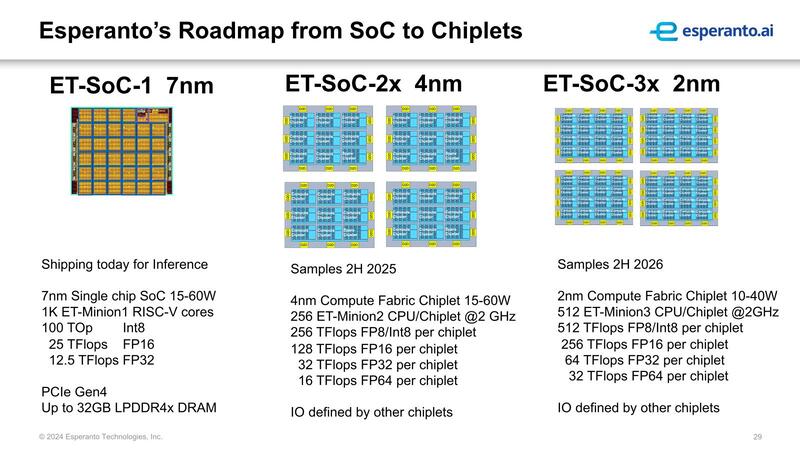

さてここからが将来製品のロードマップである。ET-SoC-1はチップ内にすべての機能を搭載しており、ここにはPCIeやメモリーコントローラーなども含まれていたが、ET-SoC-2以降はすべてチップレットになり、I/O類やメモリーコントローラーなどは外部のチップレット任せとなる。

ET-SoC-1では1088個だったET-Minionが、ET-SoC-2ではチップレット1個あたり256個になる計算で、ほぼ4分の1に減るわけだが、性能は4倍になるから「同じ動作周波数ならば」性能は同等と言う計算だ。

ちなみに上の画像で示すように、ET-SoC-2は9クラスター(うち有効なのが8)、ET-SoC-3は16クラスターとなる。クラスター内部に関してはET-SoC-2とET-SoC-3で基本的には同じ、という話であった。ただET-SoC-2は12個のDie-to-Die I/Fを持つ一方、ET-SoC-3は16個となる。

Die-to-Die I/FはUCIeを利用しており、転送速度は32Gbpsとのこと。0.2~0.3pJ/bitで、1Tbitのリンクでも消費電力は0.5W程度との試算が出ている。

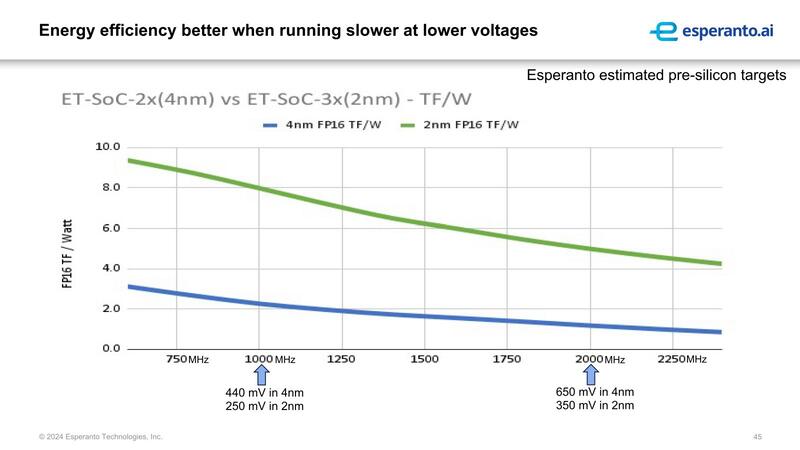

気になる動作周波数と消費電力であるが、推定で言えば1GHz動作が4nmで440mV、2nmなら250mV程度で可能になる、としている。また2GHz動作ではそれぞれ650mV/350mVということで、この2GHzの数字はわりと普通で、通常の4nmよりやや低い程度であり、ELVのメリットがまるで生かせない。おそらくは1GHz動作が標準的な数字ということになるだろう。

ただ実際の構成案を見ると、これでもまだ消費電力が多すぎる。実際には350mVあたりまで下げることを想定しているようだ。

話が前後するが、Esperantoでは第2世代のET-SoC-2を4nm、第3世代のET-SoC-3を2nmで製造することを予定している。このうち第3世代は冒頭で述べたようにRapidusで製造されるのだが、第2世代はどうもSamsungのSF4が利用されるようだ(SF4Eかもしれないが、そこまでは確認できなかった)。

まだET-SoC-2はテープアウトに至っていない(もうすぐらしい)が、2025年後半にはサンプル出荷を予定している。それはいいのだが、ET-SoC-3は2026年後半のサンプル出荷としている。Rapidusの正式なオペレーション開始は2027年度であることを考えると、さすがにこれは厳しくないだろうか? というのが正直な感想である。

この記事に関連するニュース

-

わずか2年で完成させた韓国FuriosaAIのAIアクセラレーターRNGD Hot Chips 2024で注目を浴びたオモシロCPU

ASCII.jp / 2024年11月11日 12時0分

-

Metaが自社開発したAI推論用アクセラレーターMTIA v2 Hot Chips 2024で注目を浴びたオモシロCPU

ASCII.jp / 2024年11月4日 12時0分

-

「Snapdragon 8 Elite」は何が進化したのか PC向けだったCPUコア「Oryon」採用のインパクト

ITmedia Mobile / 2024年10月28日 16時15分

-

チップレット - 相互接続で次世代システムを構築する技術革新 第3回 テストの標準化と最適化

マイナビニュース / 2024年10月23日 6時30分

-

チップレット - 相互接続で次世代システムを構築する技術革新 第2回 チップレットを相互接続してシステムを構築

マイナビニュース / 2024年10月22日 6時28分

ランキング

-

1「ポータブル外付けSSD」おすすめ3選 コンパクトボディーで大容量データも高速で対応できる【2024年11月版】

Fav-Log by ITmedia / 2024年11月18日 18時45分

-

2中古市場で「レトロiPhone」が人気? ゲオモバイル渋谷センター街店で販売急増の理由を聞いた

ITmedia Mobile / 2024年11月18日 12時30分

-

3農水省、食べてはいけない“毒きのこ”を紹介 「野生の毒きのこを誤って食べる人、後を絶たない」

ITmedia NEWS / 2024年11月18日 18時55分

-

4Salesforceの障害は「誤ったコマンド」含むDBメンテが原因か 同社が報告

ITmedia NEWS / 2024年11月18日 14時32分

-

5新作ガンプラ「HG デスティニーガンダムSpecII&ゼウスシルエット」が発売間近!新たな商品画像も一挙お披露目

インサイド / 2024年11月18日 17時20分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください