Intel 3は300~500MHz動作周波数が向上する インテル CPUロードマップ

ASCII.jp / 2024年8月12日 12時0分

Lunar Lakeの解説そのものは前回までで終わったのだが、そのLunar Lakeの初回で、少しだけ新プロセスIntel 3の詳細について触れさせてもらった。この時は1.2V Cellの信頼性の話だけで終わったのだが、今回はIntel 3そのものについて解説しよう。

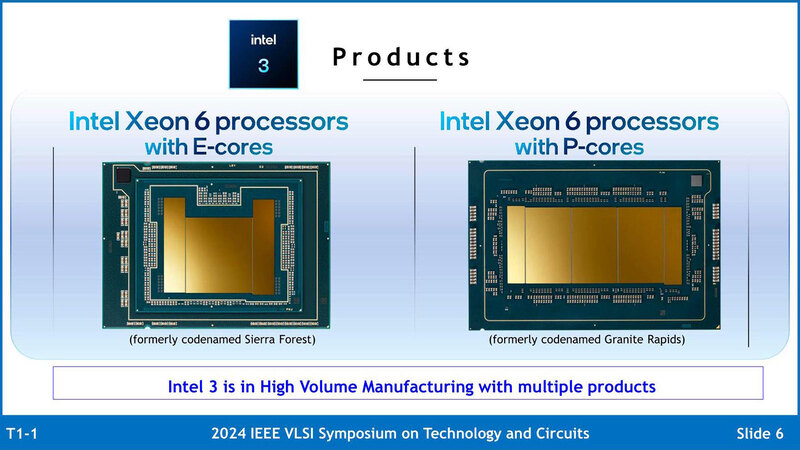

Sierra ForestとGranite Rapids以外で Intel 3を使用する製品はあるのか?

今のところSierra ForestとGranite Rapidsが確実にIntel 3を使うとわかってる製品で、Arrow Lakeは以前の話ではPコア×2のU SKUがIntel 3ベースのコンピュート・タイルを利用(S/H SKUはTSMC N3B)であったが、この話が出てきたのは2024年初頭なので、現状も生きている話なのか自信がない。

というのは、このタイミングならこの後設計をTSMC N3Bに置き換えることは十分可能だからだ。一般論として論理設計が終わった後で物理設計(P&R:Place and Routing)を行なうのには1年ほどかかるとされるが、そもそもArrow LakeではTSMC N3B向けの物理設計がS/H SKU向けに行なわれているので、これに手を入れてコア数を減らすだけでU SKU向けが実現するからだ。

ただ、省電力向けにいろいろ最適化をやり直したりする可能性はあるので、無条件にS/H SKU向けを流用できるとは限らない。Arrow Lake-UのみIntel 3の可能性はあるが、メインはXeon向けであって、その意味ではコンシューマー向けにはあまり関係ないと言えなくもない。

余談ながらそのインテル、これまでFoundry Serviceを率いてきたStuart Pann氏が5月末に引退。これを受けてKevin O'Buckley氏が跡を継ぐことが5月13日に発表されていた。ただそのPann氏、翌6月1日にはGroqのCOOに就任してることを考えると、引退と言われても素直に受け止めるのはやや難しい気がする。

それはともかくその後を継いだBuckley氏へのインタビューが8月6日に突如掲載され、また同日Intel 18Aの量産準備が順調に進んでいる旨のプレスリリースが出されたというのは、やはり8月2日の第2四半期決算を受けて、先端プロセス向けに大量の投資を続けているインテルの現状に対する批判をかわす(投資に見合った製品が出てきて、これによって競争力を再び備えるようになる)目的だろうと考えられる。

Intel 18Aはまだサービス提供は先であり、まずはIntel 3からサービスが始まることになる。Intel 3の顧客が全然いない、という話も聞こえてくるし、連載761回で紹介した図を見る限り、Intel 3の本格的な量産が始まるのは2026年後半といったあたりで当面はXeon 6向けの生産が主になるのだろうが、それでも今後はIntel 3に顧客を集めたいというニーズがある以上、ここで手を抜くわけにはいかないだろう。

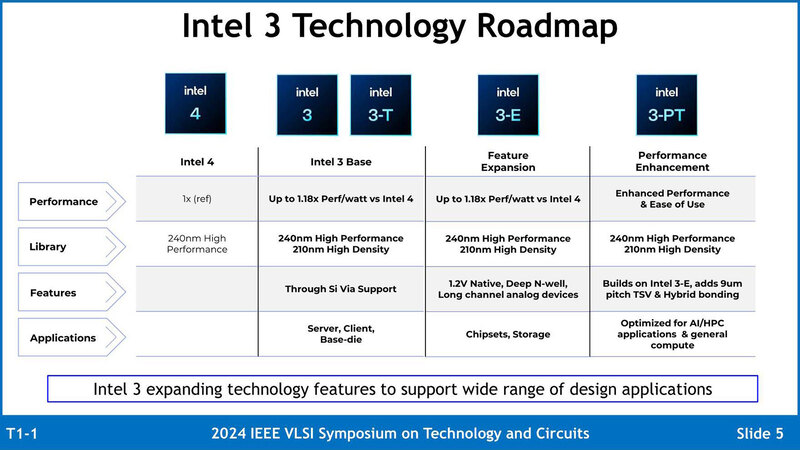

話をIntel 3に戻そう。Intel 3には派生型として3-T/3-E/3-PTがある、という話は連載760回で簡単に触れたが、今回もう少し詳細が明らかになった。具体的には下表のようになっている。

すでにSierra ForestとGranite Rapidsの量産に入っているとされている。もっともEコアの方のSierra Forest、すでにIntel Arkでは7製品がラインナップされているにも関わらず、Dell/HPE/Lenovoといったメーカーから出荷のアナウンスがないというのは、どの程度出荷が本当にスタートしているのか実はよくわからなかったりする。

ちなみにLenovoは製品アナウンスはあったものの、出荷時期は明言されていない。DellとHPEは製品アナウンスそのものが見つけられなかったのだが、実はどこかでされているのだろうか?

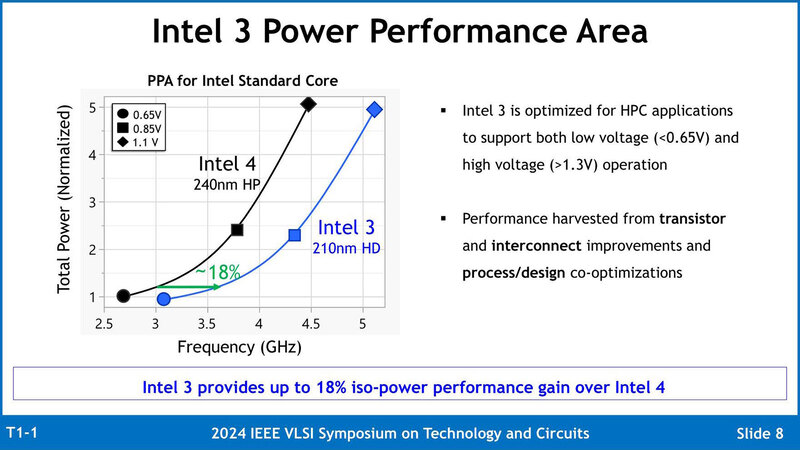

Intel 3はIntel 4より300~500MHzほど動作周波数が向上

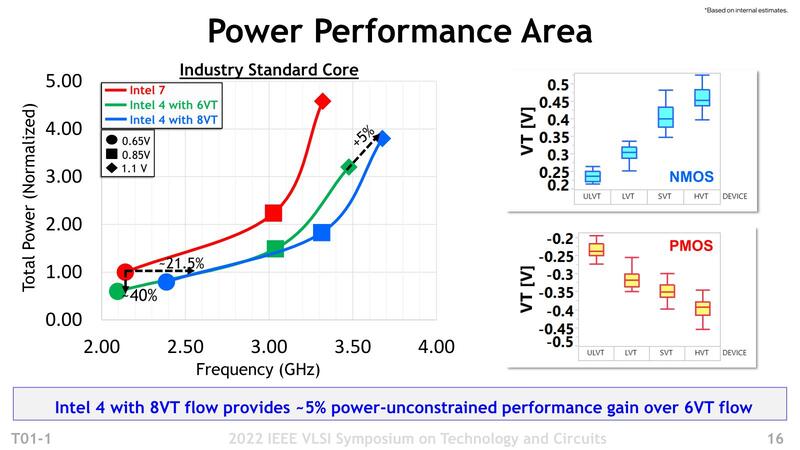

さてそのIntel 3の中身であるが、まずはStandard CellにおけるPPA Optimizationの結果が下の画像だ。同じ電力では300~500MHzほど動作周波数が向上するとしている。

ただこれ、Intel 3の方は210nmのHD Libraryを使っていることに注意されたい。おそらく、HP Libraryでは動作周波数はさらに上がるが、Powerももっと増えるものと思われる。

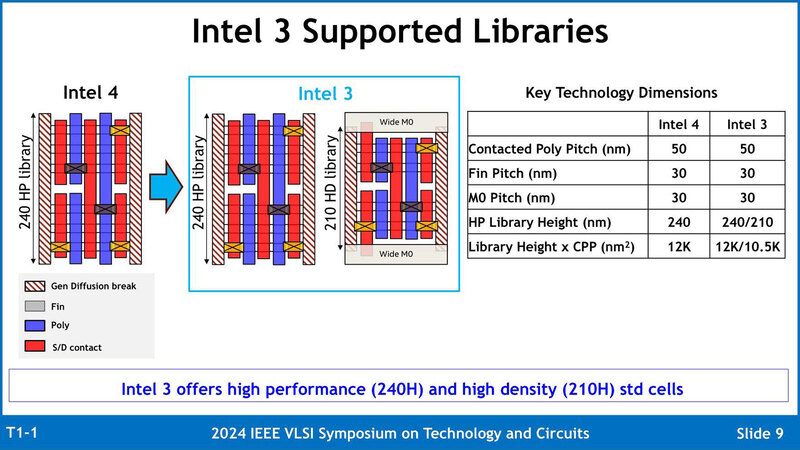

さきほども出てきた210nmのHigh Density Libraryと、Intel 4と同じHigh Performance Libraryの違いが下の画像だ。Gate Pitch(横幅:この図で言えば、2つのDiffusion Breakの間の距離)は変化ないが、240nmの方はPMOS/CMOSともに3 Fin構成なのに対し、210nmの方は2 Fin構成となっている。結果的にLibrary Hightが210nmに減ったわけだ。

これだけ見ていたら性能が向上する理由は理解できないのだが、2つ上の画像の右下にあるように、トランジスタとインターコネクトの改善で性能向上を果たしたとしている。その結果、Intel 4の3 Fin構成よりIntel 3の2 Fin構成の方が性能も上がってしかも省電力という特性につながったわけである。

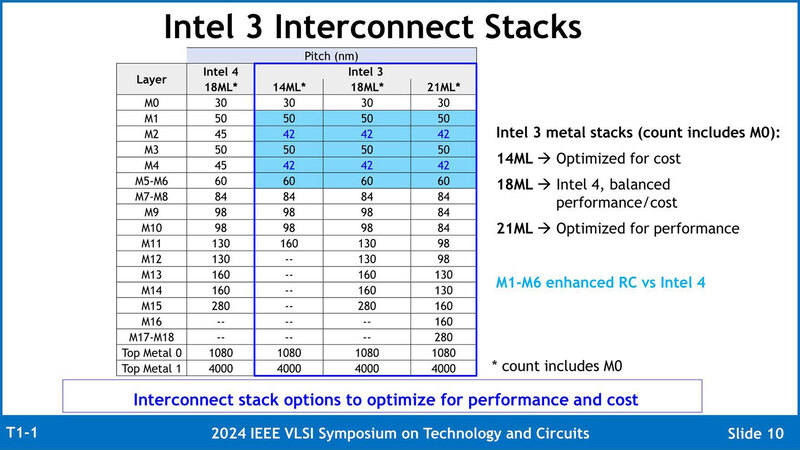

というわけで、そのインターコネクトについて。Intel 4では配線層が18層だったが、Intel 3では14/18/21層の3種類が用意される。この18MLがある意味標準的な位置付けとなるわけだが、レイヤーで言えばM2とM4が若干微細化されているのがわかる。

またIntel 4の配線では、M1~M4がeCU(銅配線の外側にコバルトの薄膜を付けた構造)になっていたが、Intel 3ではこれがM6までに拡張されたほか、enhanced RCということでおそらくは抵抗を減らすなんらかの工夫がなされた模様だ。

もしもArrow Lake-Uが本当にIntel 3で製造されているとすれば、18MLあたりが使われるだろう。逆にXeon 6(特にGranite Rapids)は、21MLを使っているかもしれない。

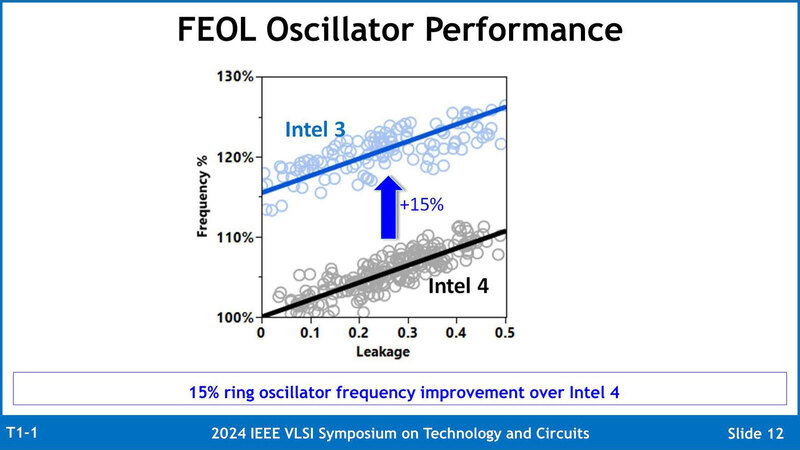

同じリーク電流なら動作周波数が15%ほど向上する

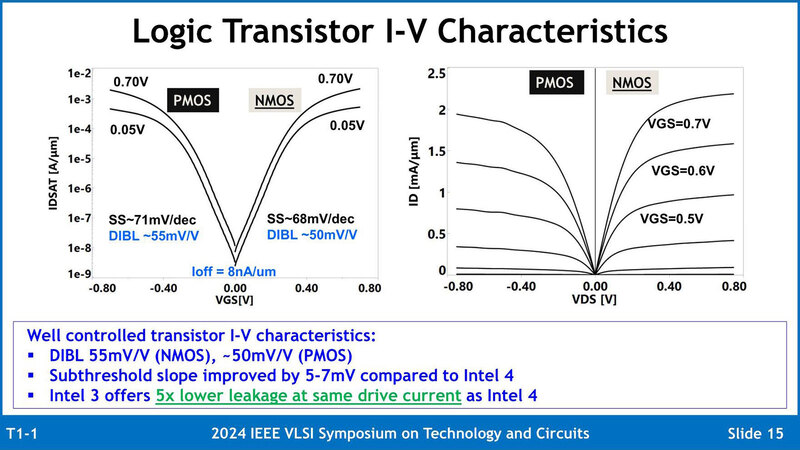

次にFEOL、つまりトランジスタ層の話である。OverallとしてRing Oscillatorを構成した場合の動作周波数は、同じリーク電流なら15%ほど動作周波数が向上するとしている。

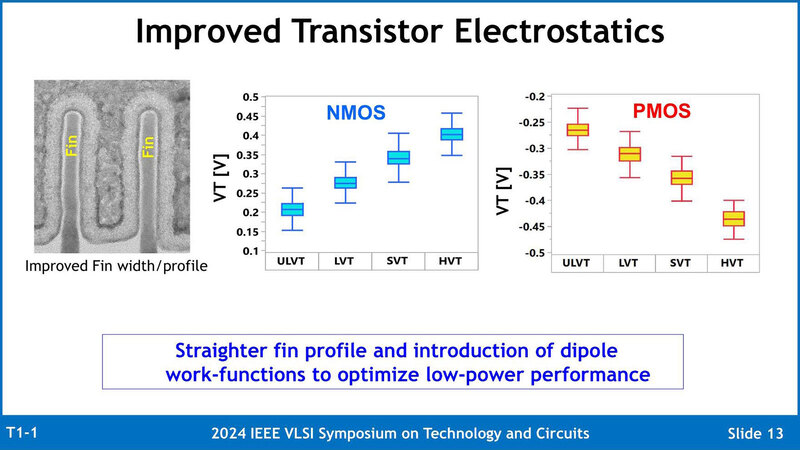

もう少し細かなトランジスタ特性が下の画像だ。

Intel 4の時の特性が下の画像であり、ULV~HVTまですべてのケースでより動作電圧が下がっていることが見て取れる。

これが実現できた理由は、Finの形状を工夫してより特性を向上させた(以前はFinの形状が末広がりだったのが、もう本当に横から見ると棒という感じになっている)ほか、コンタクトの接合方法を工夫したことだとしている。

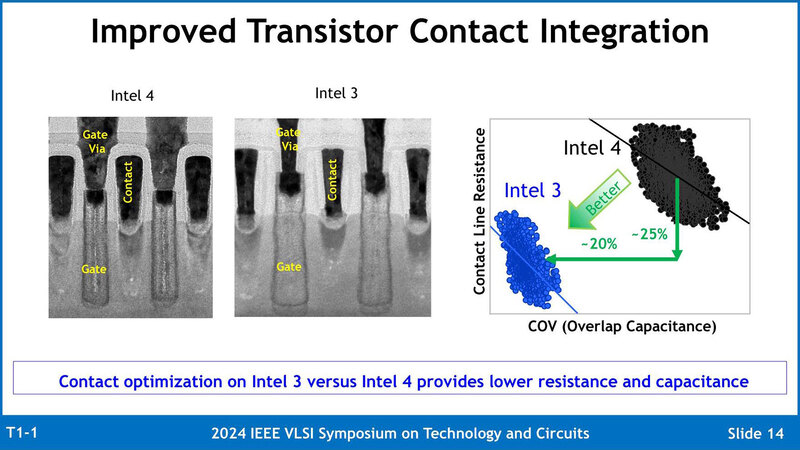

そのコンタクトの接合方法に関するスライドが下の画像である。Gate ViaやGate、Contactの周囲の絶縁層がより広く取られている。その一方でGate ViaとGateの接続部は、Intel 4よりもよりしっかりと接続されているのがわかるかと思う。

結果として、Intel 4→Intel 3で接続部の抵抗(Contact Line Resistance)が25%、全体の寄生容量(Overlap Capacitance)が20%削減されたとしている。これだけ配線部の抵抗や容量が減ったら、それは特性の向上に大きな寄与が見込めるだろう。

このContact Gate周りの工夫やFin構成の改善のほかにもいくつか改良点はあるのだろう。結果としてトランジスタの特性もだいぶ改善された。

Intel 4の場合、Short Channel EffectsはPMOSがSS:~75mV/dec、DIBL ~77mV/V、NMOSが75mV/dec、DIBLは~62mV/Vだった。SS(Subthreshold slope)も、DIBL(Drain-induced barrier lowering)も、それが大きいほど大電圧をかけた際の性能低下が大きくなる。このあたりも性能改善(特に高速動作時の消費電力を抑えること)に貢献しているものと思われる。

トランジスタまで含めた信頼性が大きく改善

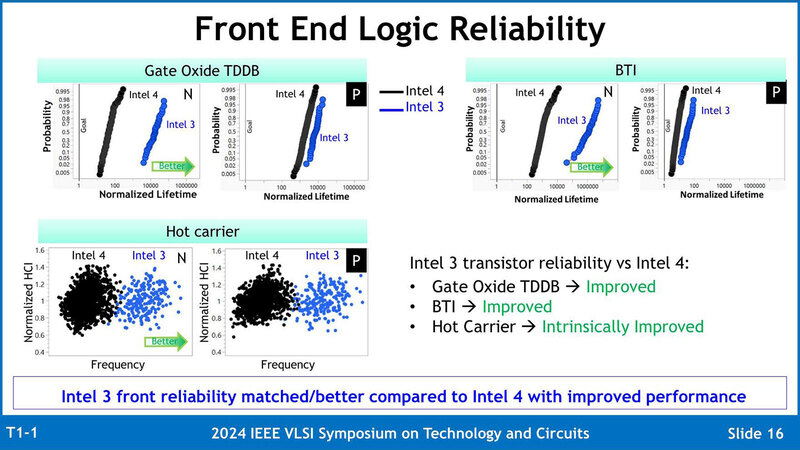

次が信頼性周りの話。1.2V Cellの信頼性の話は連載777回で説明したので割愛するとして、通常のトランジスタまで含めての信頼性の話が下の画像だ。

まず最初の2つについてはこうした現象が発生するまでの時間がだいぶ改善している。またHCIに関しては、同じHCIの発生率に対してより動作周波数を上げられるようになったことが観測されている。FETもある意味、機械部品であり、ずっと使っていれば次第に劣化していくことは避けられないのだが、その劣化の度合いがだいぶ改善した、という話である。

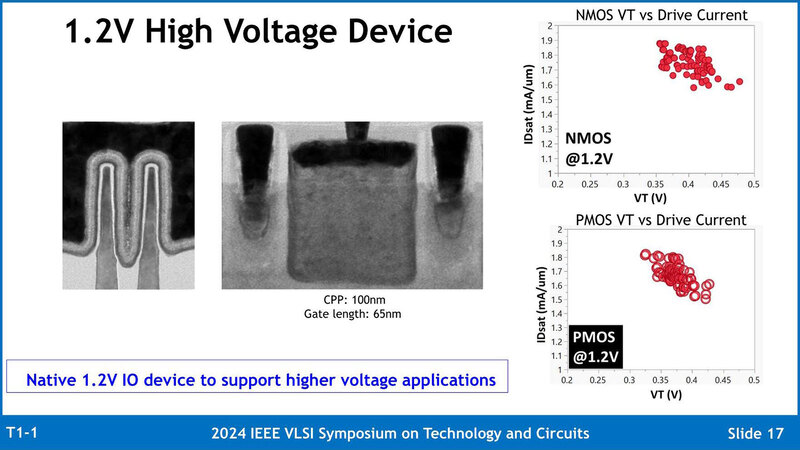

説明では次に1.2V Cellの話に移るのだが、これも連載777回で紹介したので割愛する。ただその1.2V Cellの断面写真が示されていたので紹介しておきたい。

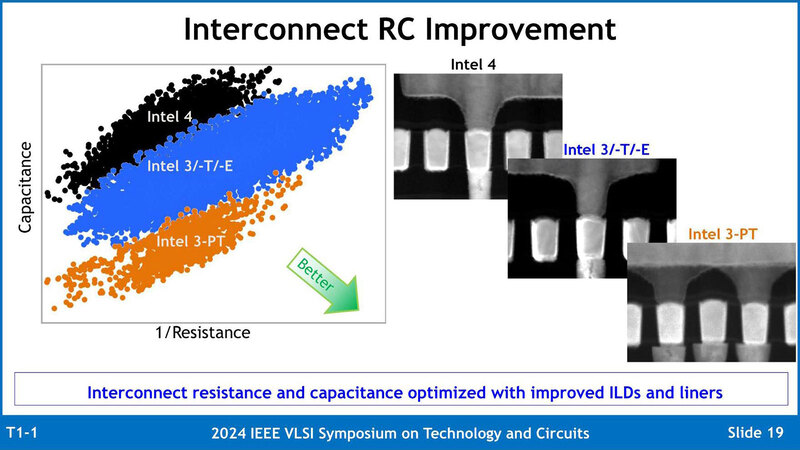

最後にIntel 3-PTの話である。先にIntel 3-Eの高性能版と説明したが、具体的な話としてインターコネクトの改良が紹介された。ただIntel 3-Eと3-PTの違いが単にインターコネクトだけなのか、ほかにトランジスタの改善なども含まれるのかは不明だ。

ということで、VLSI Symposiumにおけるインテルの発表を簡単にまとめてみた。問題は歩留まりや現在のウェハー生産能力なのだが、このあたりの情報は当然ながら公開されていない。Intel 3の出来具合がXeon 6の性能や供給体制に大きく関わってくるだけに、順調に生産できていることを祈るのみである。

この記事に関連するニュース

-

トランジスタ最先端! RibbonFETに最適なゲート長とフィン厚が判明 IEDM 2024レポート

ASCII.jp / 2025年1月13日 12時0分

-

PCテクノロジートレンド 2025 - Memory編「DDR」「MRDIMM」「GDDR」「HBM」

マイナビニュース / 2025年1月5日 10時0分

-

PCテクノロジートレンド 2025 - CPU編「Intel」と「AMD」

マイナビニュース / 2025年1月3日 10時0分

-

PCテクノロジートレンド 2025 - プロセス編「TSMC」

マイナビニュース / 2025年1月1日 10時0分

-

トランジスタの当面の目標は電圧を0.3V未満に抑えつつ動作効率を5倍以上に引き上げること IEDM 2024レポート

ASCII.jp / 2024年12月23日 12時0分

ランキング

-

12023年に急逝した五彩緋夏さんの親友、“2年前の写ルンです”を現像……緋夏さんとのお宝ショットに「この写真が見れてよかった」と大きな反響

ねとらぼ / 2025年1月13日 12時45分

-

2セザンヌの“700円福袋”を開封したら…… 予想以上の開封結果に驚きの声「太っ腹すぎる!」「プチプラでも優秀」

ねとらぼ / 2025年1月14日 19時30分

-

3IIJmio、mineo、NUROモバイル、イオンモバイルのキャンペーンまとめ【1月15日最新版】 110円スマホや高額ポイント還元あり

ITmedia Mobile / 2025年1月15日 10時34分

-

4「神ゲー」日本からの声高く翻訳後の日本売上7倍に、“日本人に何故か熱い注目あびたため”日本語実装のインディーSRPG―「実際は、賭けだった」語られる裏側

Game*Spark / 2025年1月11日 18時45分

-

5「配慮が足りない」 映画の入場特典で「おみくじ」配布→“大凶”も…… 指摘受け配給元謝罪「深くお詫び」

ねとらぼ / 2025年1月15日 7時0分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください