Xeon 6のIOチップレットには意地でもDDR5のI/Fを搭載しないインテルの強いこだわり インテル CPUロードマップ

ASCII.jp / 2024年8月19日 12時0分

連載783回で、COMPUTEXで公開された話を説明し終わった気になっていたが、Xeon 6とGaudi 3の詳細が公開されたことをすっかり忘れていた。ということで、今回はXeon 6の話をしよう。

2種類のパッケージが存在するXeon 6

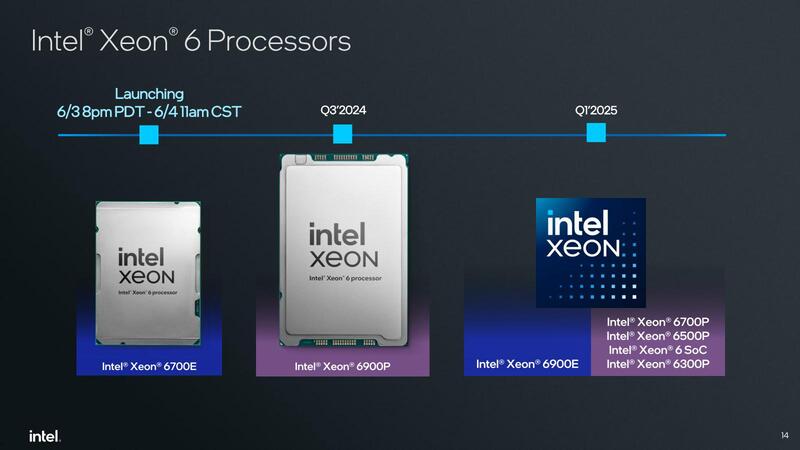

Sierra ForestおよびGranite Rapids、つまりXeon 6の話はこれまで何度かしてきた。直近では連載736回と連載737回だし、その前にもあちこちで言及しているわけだが、COMPUTEXのタイミングでもう少し詳細が公開されるとともに、Xeon 6の最初の製品であるXeon 6700シリーズの7製品もラインナップされた。

筆者が誤解していたのだが、Xeon 6には2種類のパッケージが存在する。4/5th Gen Xeon Scalableと「近い」FCLGA 4710と、一回り大きいものである。

「近い」というのは、外形寸法はどちらも77.5×56.5mmとされているのだが、4/5th Gen Xeon ScalableはFCLGA 4677だからで、現状プラットフォームそのものは互換性があるという情報はない。

例えばSuperMicroはXeon 6に対応したX14ソリューションを4月に発表しているのだが、このX14でサポートされるのはXeon 6のみで4/5th Gen Xeon Scalableはサポートされないし、逆に既存の4/5th Gen Xeon Scalableに対応したソリューションにXeon 6のサポートは入っていない。したがって、マザーボードそのものが異なるもの、と考えるべきなのであろう。

では、Sierra ForestがFCLGA 4710、Granite RapidsがFCLGA 7529かというと、そういうわけでもないようだ。上の画像で青がEコアベース、紫がPコアベースであるが、来年第1四半期にはXeon 6900EでこれはおそらくFCLGA 7529ベース。一方Xeon 6300P~Xeon 6700PはおそらくFCLGA 4710ベースとみられる。要するに今後Xeon 6は2種類のプラットフォームで提供されるということである。

これ、サポートの手間やアップグレードパスなど考えたときに、本当に賢明なアイディアだったのかは非常に疑問である。顧客(つまりXeon 6ベースのサーバーを出荷するOEMベンダー)にとっても、無駄にラインナップが増えるだけでしかないのだが、どうしてこういうことになったのか? というヒントは後で説明したい。

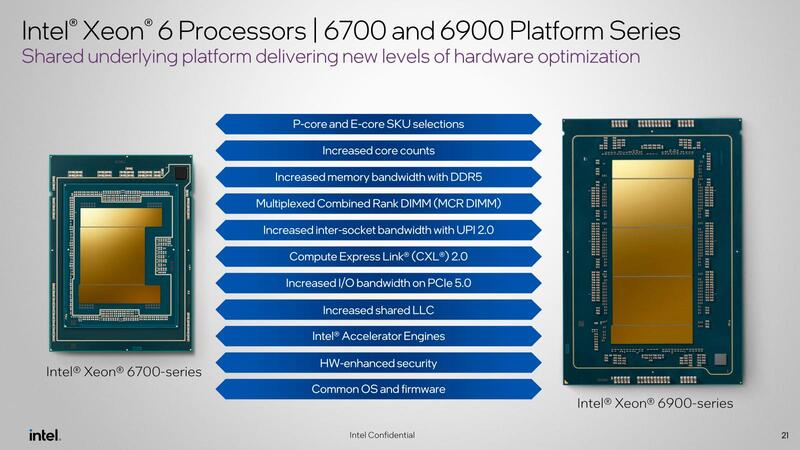

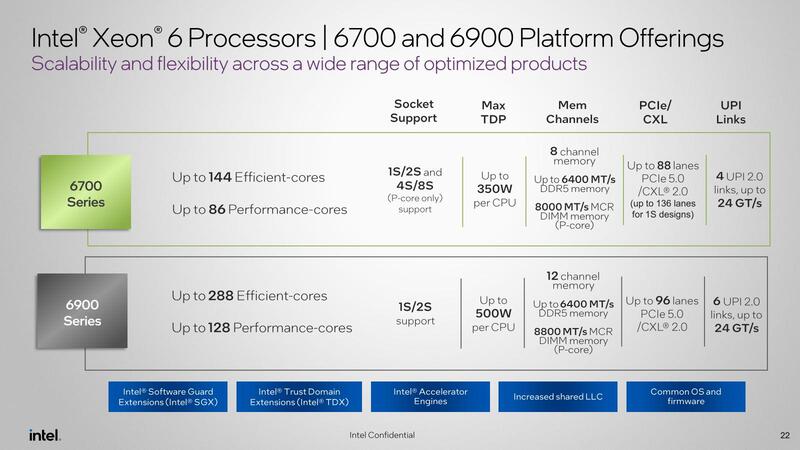

さてこの2つのプラットフォームであるが、基本的な特徴は共通とされる。

では2つのプラットフォームでの違いは? というのが下の画像だ。

基本的にはメモリーチャンネル数やPCIe/UPI Link数の違いであるのだが、それより大きいのは消費電力である。もともとLGA 4677の時代もTDPは350W程度だった。もちろん中にはXeon Platinum 8593Qのように385Wと、ほぼ400W近くまで行なっているプロセッサーもあるのだが、4th Gen Xeon Scalableの時代は最大350Wに抑えられており、これを5th Genでは特定のSKUのみちょっぴりオーバーする形だった。

ただGranite RapidsとSierra Forestの288コア版などは到底これで収まらなかったのだろう。またダイサイズ的にもパッケージいっぱいになりかねない。より供給電力を増やすためには電源/GND用のピンを増やすか、供給電圧を上げる(例えば12V供給とし、パッケージの上にVicorあたりのVRMを載せてそこから1V程度を生成する)のどちらかしかない。

最近はあまりの電流量の多さに、電圧を引き上げる方策を検討する事例が増えてきたが、インテルは自前ではまだそこまでの解決策を提供できていない。となるとピン数を増やすしかなく、必然的にパッケージが大型化せざるを得なかったということだろう。ただ、そこまで増やすべき理由が本当にあるのか? というのはやや疑問ではあるのだが。

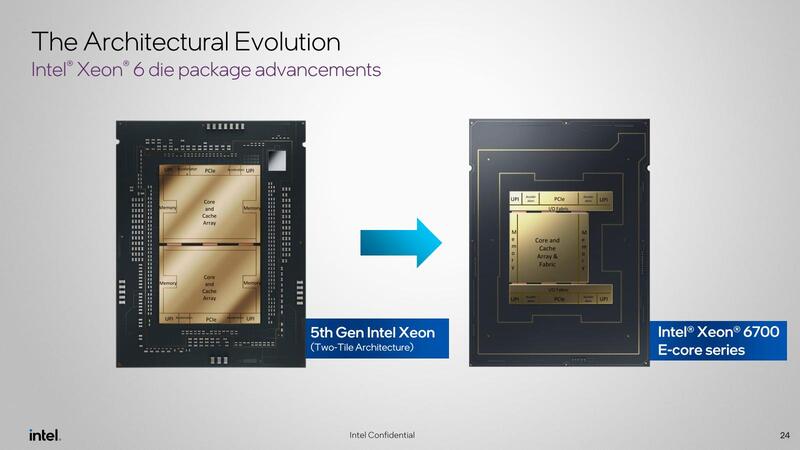

連載736回の答え合わせ 左と中央がPコアタイル、右がEコアタイルで正解だった

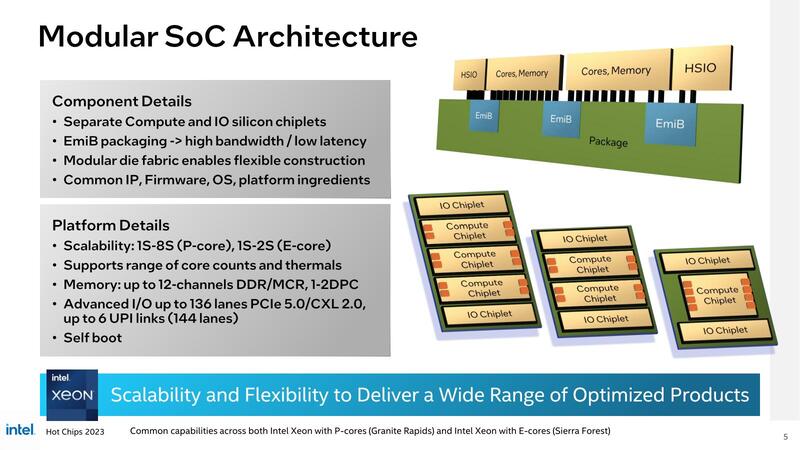

ところで連載736回で、Hot Chips 2023におけるスライドを取り上げたが、これの答え合わせをする時間がやってきた。

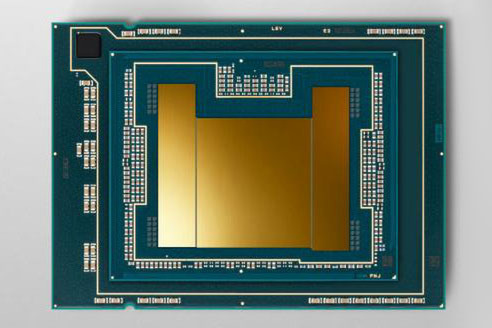

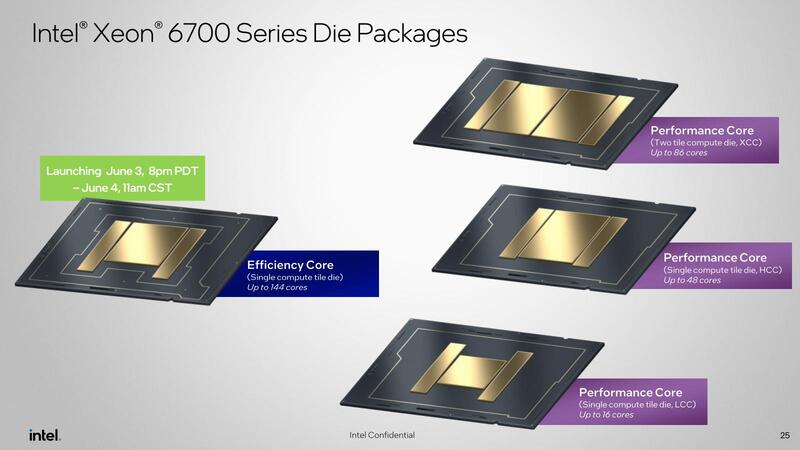

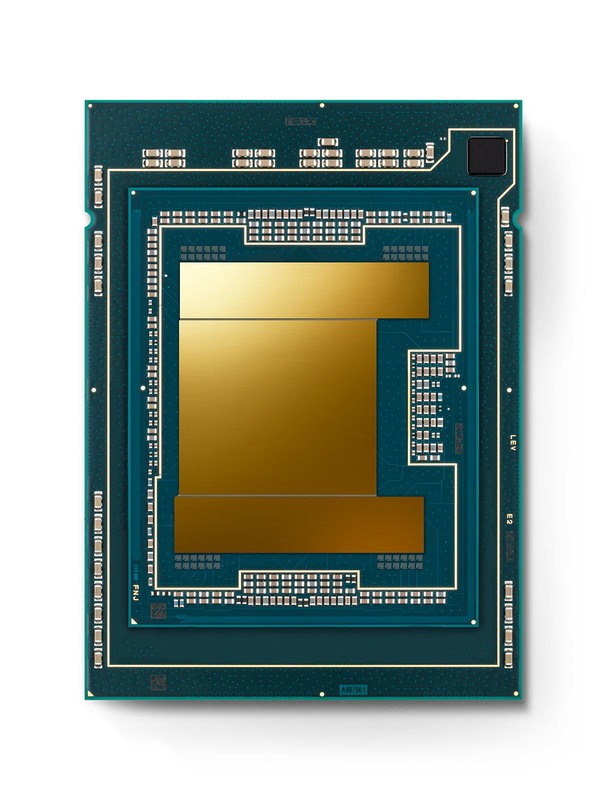

まずXeon 6700シリーズ、つまりFCLGA 4710のパッケージが下の画像である。

Eコア(左側)は比較的スクエアなコンピュート・チップレットの両側にIOチップレットが配される格好。以前の情報で言えば、コンピュート・チップレットにメモリーコントローラーが搭載される模様。つまり144 Eコア+8ch DDR5 I/Fである。

Pコア(右側)は、またもやXCC/HCC/LCCの3種類のコンピュート・チップレットが用意される。ということは以下の構成になる。

プロセッサー内部の構造が下の画像で、ここから察するに下表のような内部構造になっているように思える。

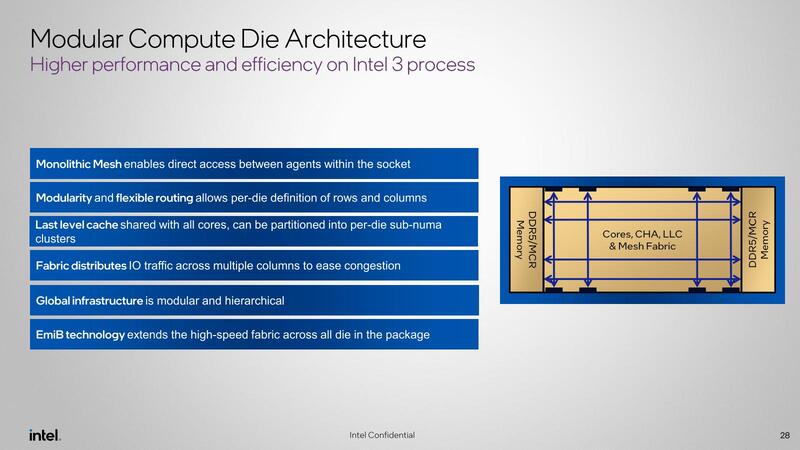

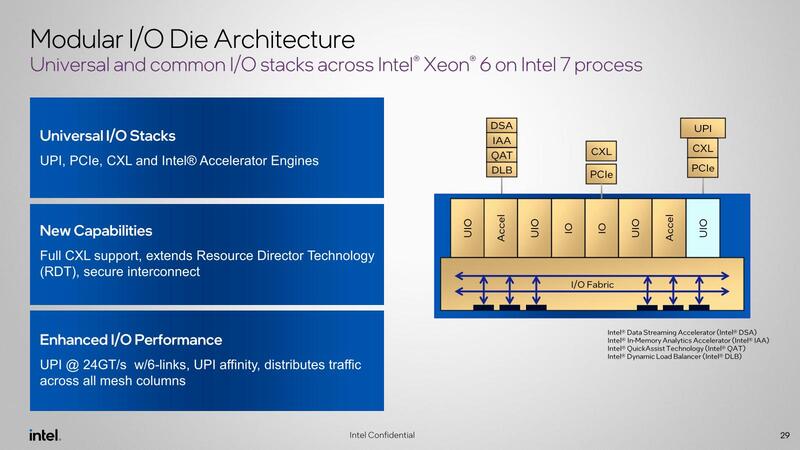

XCCで冗長コアが多いのは消費電力の制限の可能性もありそうだ。一方IOチップレットそのものは、少なくとも今見てる限りはEコア/Pコアで共通に思える。内部構造は下の画像のとおりで、アクセラレーターと外部I/Fをまとめた格好である。

このIOチップレット、最初のページにある2つ目の写真で比較する限りにおいては同じ幅と高さになっており、実際の製品写真での比較ではないので断言はできないがXeon 6900シリーズと共通の可能性が高い。

Xeon 6900シリーズは有機パッケージが2段重ねの不思議な構造

Xeon 6900シリーズの構成が下の画像だ。こちらもXeon 6700シリーズと同様に推定すると下表の構成になっているように見受けられる。

ここから察するに、Eコアのコンピュート・タイルはFCLGA 4710のものと共通で、ただしチップレットあたり8chのメモリーコントローラーを6chに制限したもの。またPコアの方はFCLGA 4710のXCCをそのまま流用しているようだ。

ところでそのXeon 6700、実際のパッケージ写真が下の画像だが、少し妙なことに気がつく。なぜ有機パッケージの2段重ねになっているのだろう?

実際横から見ると、明らかにパッケージが2段重ねになっているのがわかる。理由は不明であるが、こういう構造だと上側のパッケージにコンピュート・タイルを2つ載せるのは絶対に不可能である。それにしても不思議な構造である。

以上のように、Xeon 6の世代でインテルは5種類(Eコアのコンピュート・チップレット、PコアのXCC/HCC/LCCチップレット、IO チップレット)ものチップレットを製造する必要があることになる。最大の理由は、意地でもIOチップレットにDDR5のI/Fを搭載しなかったためである。

AMDの考え方なら、メモリーコントローラーをIOチップレット側に移動したうえで、Pコア×16のみの細長いコンピュート・チップレットを用意するだろう。XCC向けはこれを5つか6つ。HCCは2つ、LCCは1つである。それにIOチップレットを組み合わせれば完成なのだが、そうしなかったあたりがインテルなりのこだわりだろう。

言うまでもなく絶対性能そのものはインテル方式の方が高くしやすい(本当に高くなるかどうか、はまた別の問題)。ただしそのために多数のチップレットを設計・製造するのでコストは当然高くなるし、チップレットそのものの面積も大きくなるので歩留まりも下がる。

さらに言えば検証するべき組み合わせが増えるということでもある。この検証周りはSapphire Rapidsの時も問題になっていたし、現在進行中でRaptor Lakeの問題(こちらもまだ解決していないというか、本当の原因が判明していない)もある。そこに来て今度はXeon 6の多数の組み合わせの検証が待っているわけで、検証チームの負荷は増えるばかりというのは、お気の毒としか言いようがない。

Xeon 6756Eの性能はEPYC 9534とほぼ同等

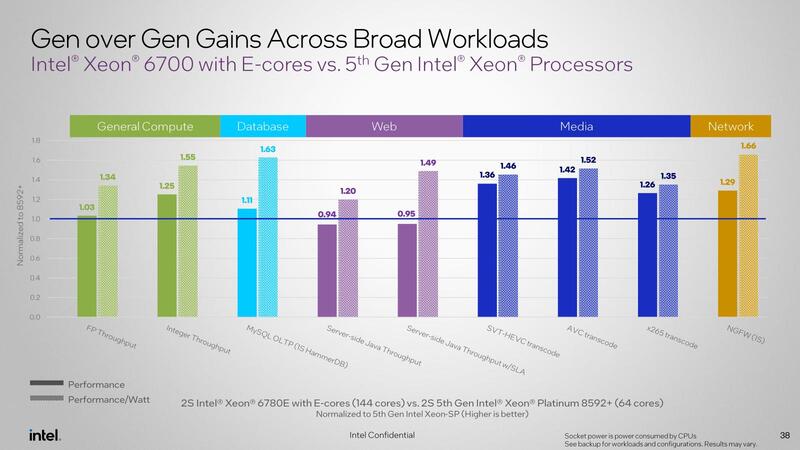

現状出荷されているのはXeon 6700製品のみということで、EコアベースのSierra Forestでのスコアであるが、5th Gen Xeon ScalableであるXeon Platinum 8592+との性能および性能/消費電力比の比較が下の画像である。

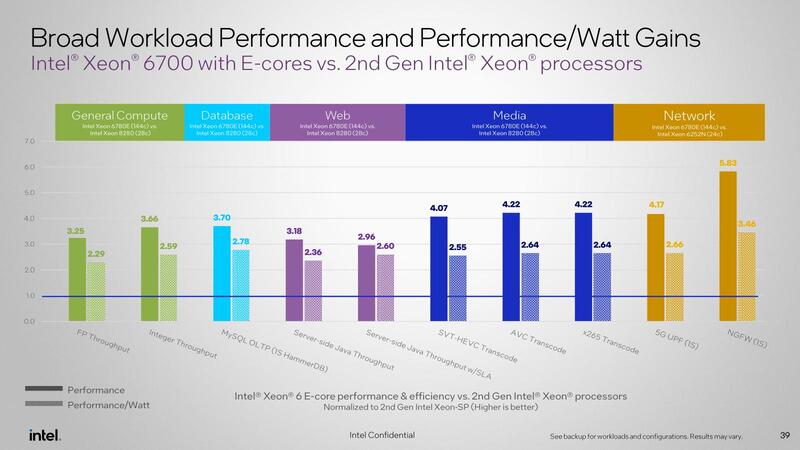

そして2nd Gen Xeon Scalableとでは3~4倍の性能と、倍以上の性能/消費電力比を実現しているとする。

ただグラフを見ると性能の方が性能/消費電力比より大きいということは、消費電力の絶対値そのものはむしろ増えていることに注意されたい。一番少ないServer-side Java Throughput w/SLAで13.8%、一番多いNGFW(1S)で68.5%の増加となる。

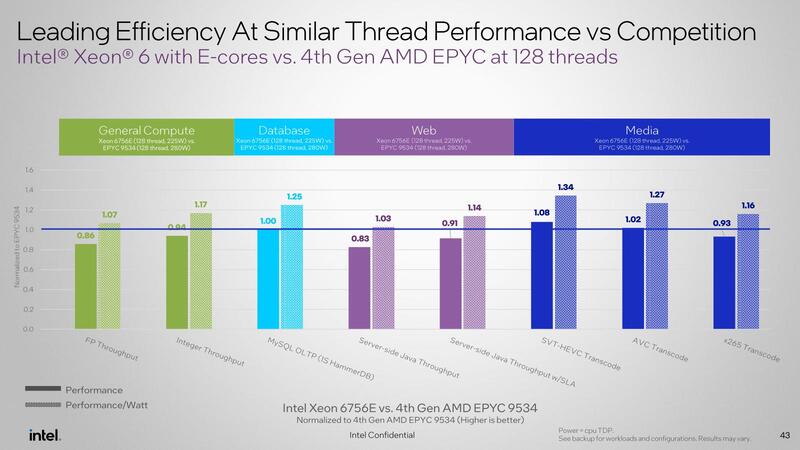

そして最後がAMDのEPYC 9534との比較である。ここでは同一スレッド数(128スレッド)という比較で、性能的にはやや劣るが性能/消費電力比では若干上回っているとする。

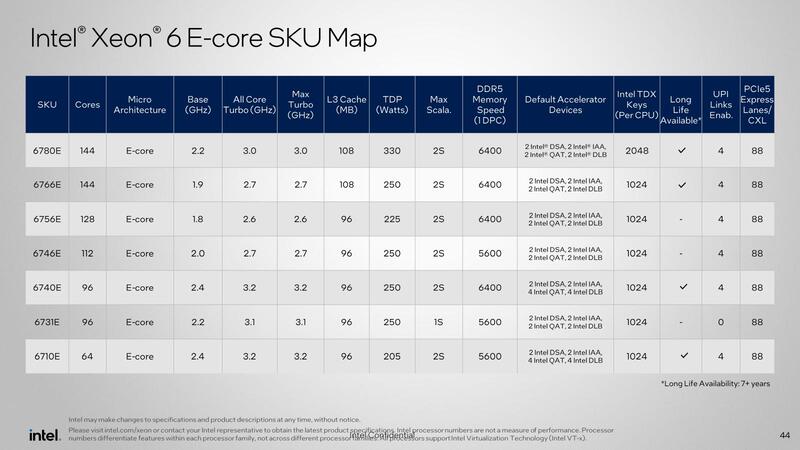

最後にSKU一覧を示しておく。Eコアベースということで動作周波数そのものはかなり低めである。現状インテルからは明示的にSierra Forestのコアがなにかは示されていないが、おそらくMeteor Lakeと同じくCrestmontと思われる。

Lunar LakeのSkymontほどではなにせよ、Gracemont世代からは多少強化されていることで、この性能を実現しているものと考えられる。もっとも微妙なのは、EPYCの方はSMTを有効にしての128スレッド、つまり64コアでこの性能を叩き出しているわけで、これの損得を判断するのはやや難しそうだ。

この記事に関連するニュース

-

iiyama PCより、インテル® Core™ Ultra プロセッサー(シリーズ2)搭載BTOパソコン・単体パーツ販売開始

@Press / 2024年10月25日 14時40分

-

第5世代EPYCはMRDIMMをサポートしている? AMD CPUロードマップ

ASCII.jp / 2024年10月21日 12時0分

-

Core Ultra(シリーズ2)にデスクトップ/ハイエンドモバイル向けモデルが登場! これまでのIntel製CPUとの決定的な違い

ITmedia PC USER / 2024年10月11日 6時0分

-

10月25日登場のArrow Lake、強みはどこ?アーキテクチャーのポイントをおさらい

ASCII.jp / 2024年10月11日 0時0分

-

ASUS、革新的なインテル Xeon 6 プロセッサー搭載サーバーを発表

PR TIMES / 2024年10月10日 12時15分

ランキング

-

1IIJ勝社長、大手3キャリアの“30GBプラン改定”に「スタックテストをやっていただきたい」と要望

ITmedia Mobile / 2024年11月8日 18時56分

-

2「ガチでレア品」 祖父が所持するSuica、ペンギンの向きをよく見ると……? 懐かしくて貴重な1枚に「すげえええ」「鉄道好きなら超欲しい」と興奮の声

ねとらぼ / 2024年11月8日 20時10分

-

3出そろった「AQUOS sense9」の価格 ドコモ、KDDI、ソフトバンク、楽天モバイル、IIJmio、mineoでお得なのはどこ?

ITmedia Mobile / 2024年11月8日 15時49分

-

480年代デザインのBluetooth搭載ラジカセ発売 カセットテープのデジタル化も可能

ITmedia Mobile / 2024年11月8日 19時2分

-

5M4チップ搭載の新型「MacBook Pro」は堅実な選択肢へと進化した1台だった 試して分かった違い

ITmedia PC USER / 2024年11月7日 23時10分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください