AI推論用アクセラレーターを搭載するIBMのTelum II Hot Chips 2024で注目を浴びたオモシロCPU

ASCII.jp / 2024年9月23日 12時0分

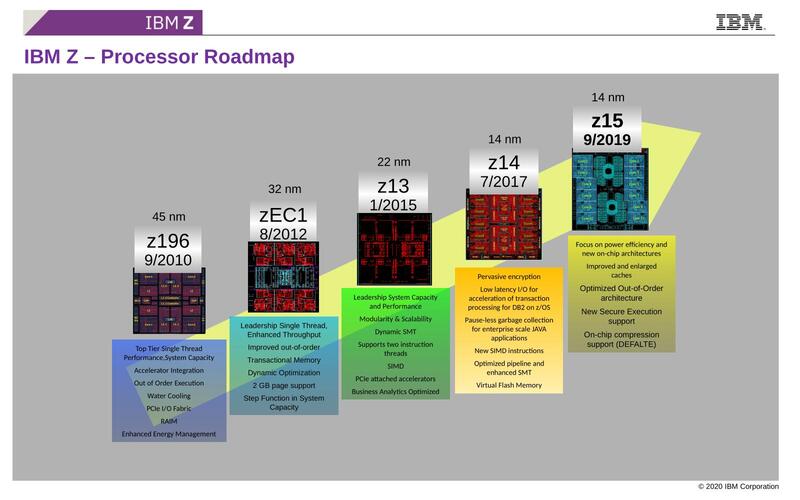

Hot Chips第3弾は、IBMのTelum IIである。これはIBMのzシリーズの系列のプロセッサーとなる。IBMのzシリーズは以前連載502回で取り上げたが、高可用性/高信頼性を最大の特徴とするメインフレーム向けプロセッサーのシリーズである。連載502回ではz14までのラインナップを紹介したが、2019年にz15プロセッサーが発表された。

10進演算がある珍しいzシリーズ 2019年にz15プロセッサーを発表

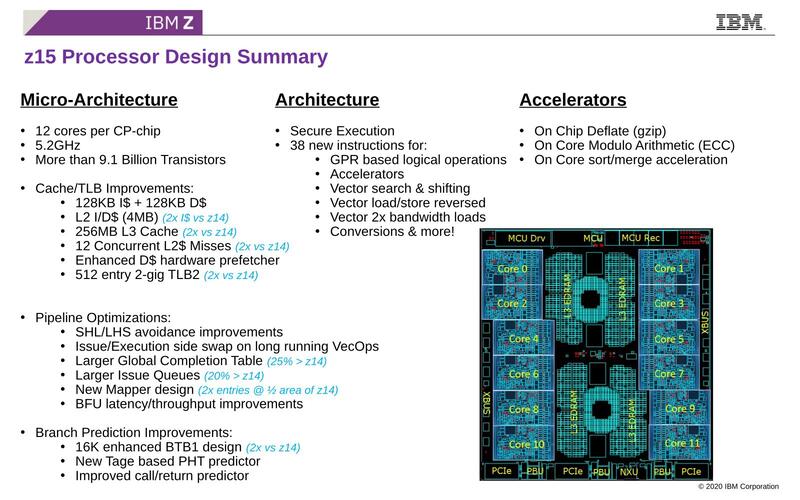

z14→z15はどちらも同じ5.2GHz動作であるが、コア数以外に細かな性能向上の工夫が凝らされている。

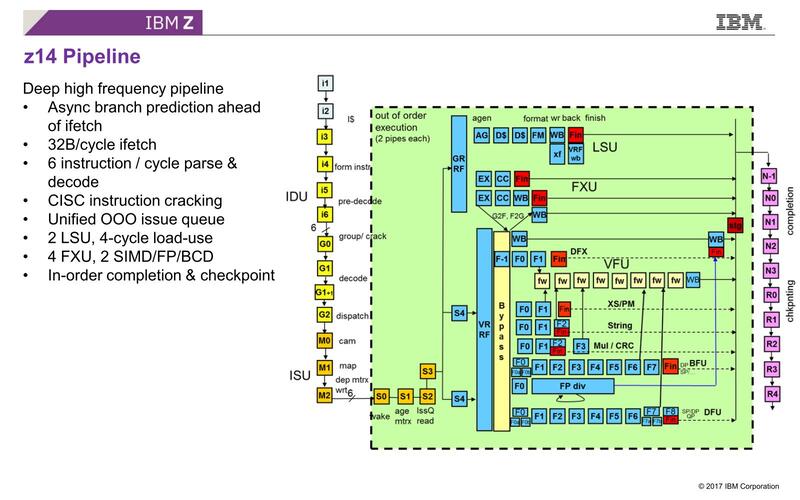

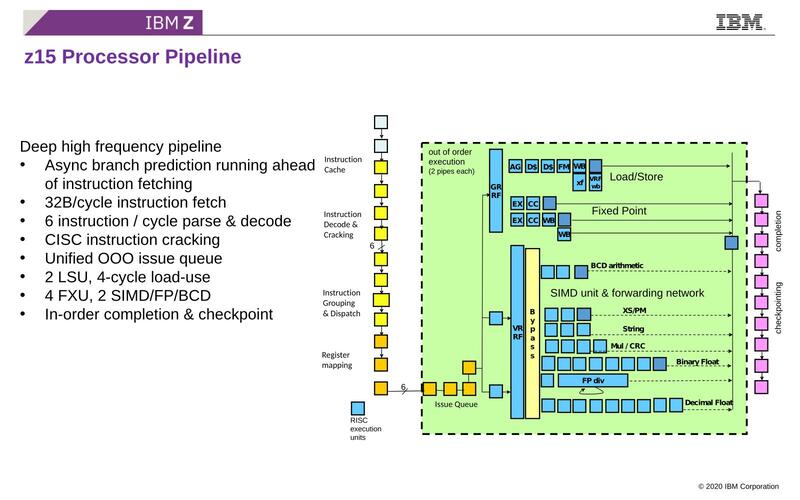

処理パイプラインの構造そのものは、細かな改良は当然いろいろあるにせよz14とz15はほぼ同じで、6命令/サイクルのデコードを持つフロントエンドに、ALU×4+Load/Store×2、FPU/Vector×6のバックエンドという構成になっている。z15がおおむねz14の延長にあることはおわかりいただけるだろう。

ちなみにシステム全体という意味では、z14では6つのCP(Central Processor)チップが1つのSC(System Controller)チップにつながっており、この7チップで1つのドロワー(要するにシャーシに収まるユニット)を構成する。

SCは言ってみればドロワー間を接続するためのI/Oチップみたいな扱いだが、その672MBのL4も内蔵されている。これに対しz15では4つのPU(Processor Unit:z14で言うCP)と1つのSCでドロワーが構成されているが、SCには960MBものL4が搭載されているという違いがある。

最大構成で言えば、z14の場合は24CP(つまり240コア)までサポートし、一方z15は20PUだがコア数で言えばやっぱり240コアになる。Xeonの8ソケット構成など問題にならないくらいの大規模なシステムが構築できる。

分岐予測を再設計したTelum 周波数はz15から据え置きでキャッシュを増量

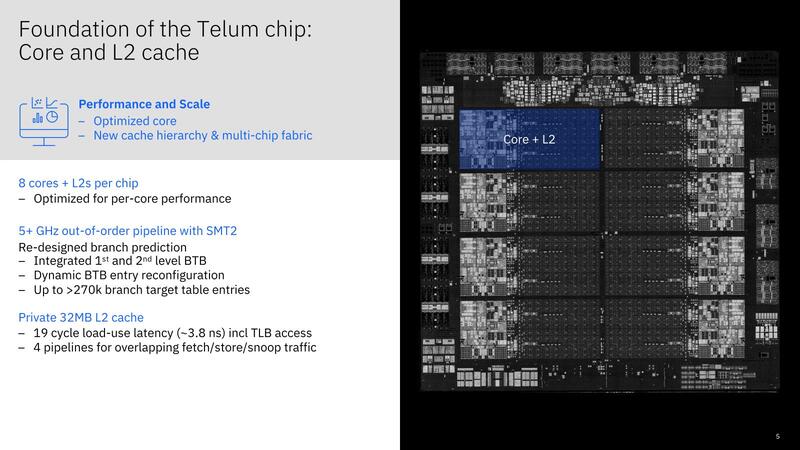

そのz15の後継として2021年に発表されたのがTelumプロセッサーである。Telumではややプロセッサーの方向性が変わった。まずチップそのものであるが、8つのコアから構成される。

おのおののコアの詳細は明らかにされなかったが、基本はz15までのパイプライン構造を踏襲しているものと考えられる。2スレッドのSMTというのもz13時代からずっと実装されている話で、このあたりは変わらない。

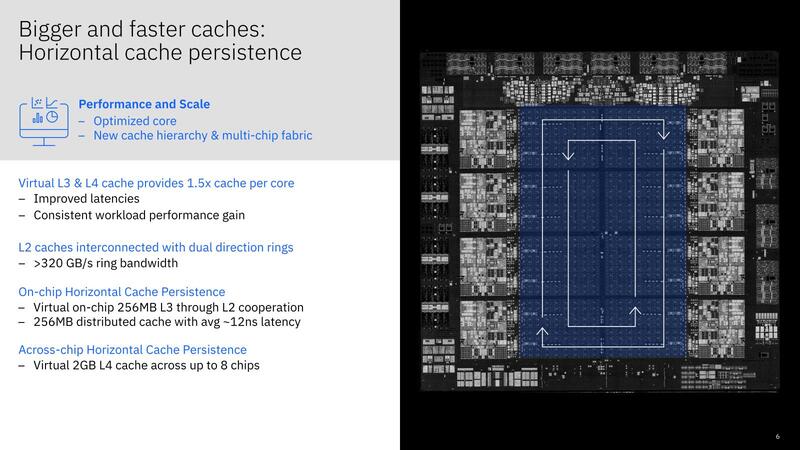

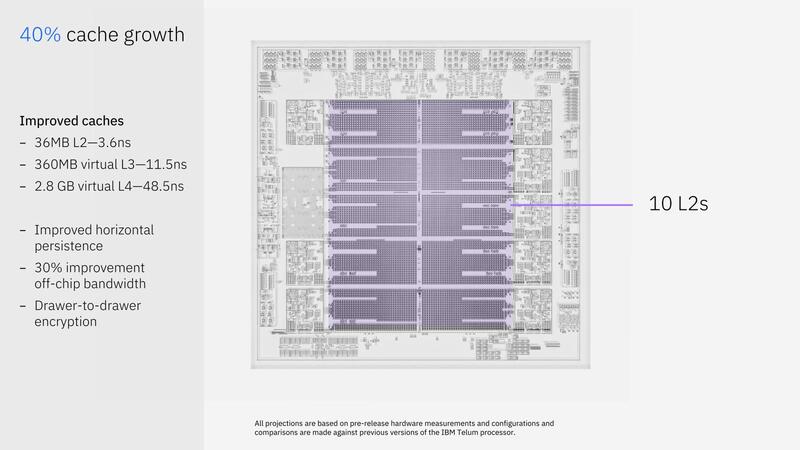

また動作周波数も5.2GHzで据え置きである。L3とL4は8コアで共通だが、コアあたりの容量は1.5倍になったほか、Virtual L3/L4が搭載された。このVirtual L3/L4は、以下の仕組みになっている。したがって、全コアが稼働中だとVirtual L3/L4は無効になる。

- 同一チップ内の非アクティブなコアのL2をL3として扱う

- 異なるチップ内の非アクティブなコアのL2をL4として扱う

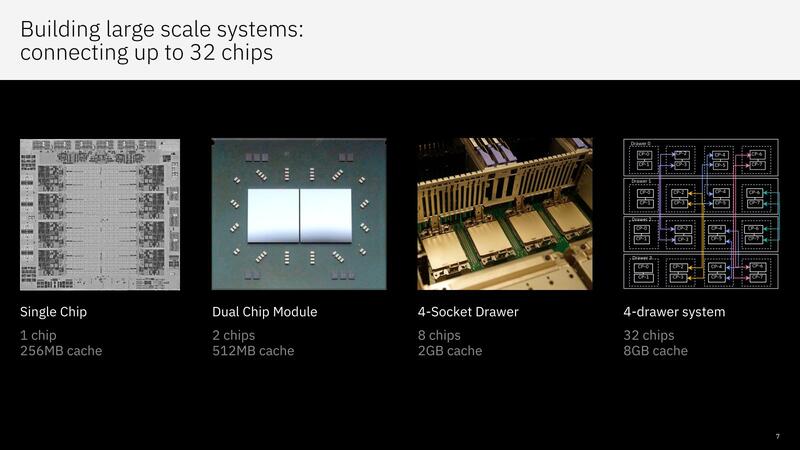

Telumのダイそのものは7nmプロセスを利用しているとあって530mm2とそれほど大きくないが、実際には2つのダイを1つのチップに搭載している。

1つのドロワーには4チップが搭載されるので、1ドロワーあたり64コアという構成だ。システム全体では4ドロワー構成(32チップ:256コア)までのSMP構成が可能とされる。ちなみにシステム的には256コアでも、ユーザーが利用できるのは最大200コアに制限されているそうだ。

※お詫びと訂正:記事初出時、Telumの発表年に誤りがありました。記事を訂正してお詫びします。

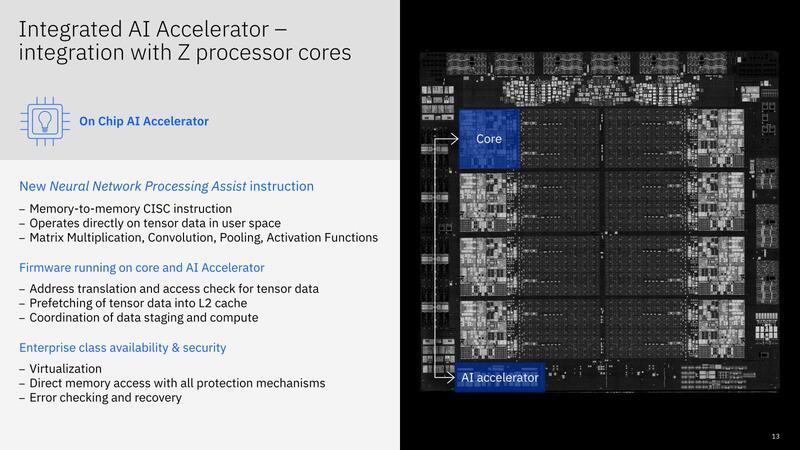

TelumはAI推論用のアクセラレーターを搭載

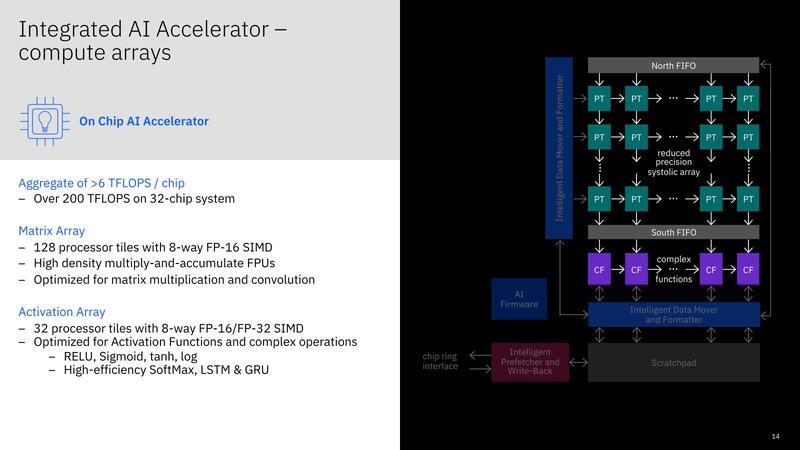

Telumでもう1つ大きな特徴は、AI推論用のアクセラレーターを搭載していることだ。このアクセラレーターはコアとは別の個所に配されており、マトリックス演算や畳み込みなどの演算を直接メモリーから読み込み、その結果もまたメモリーに書き戻す形で実施している。

この推論アクセラレーター、内部は8wayのFP16 SIMDエンジンを持つプロセッサー×128をマトリックス構成にしたものに、アクティベーション専用にFP16/FP32 8way SIMDを持ったプロセッサー×32を用意するという、なかなか強力な代物であり、チップ1個あたりで6TOPSの性能を持つとする。

他にもNXU(Nest Accelerator Unit)と呼ばれる、GZIPの圧縮/伸長用のアクセラレーターやMerge/Sort用のアクセラレーターなど、細かいアクセラレーターがいろいろ搭載されているのも特徴である。IBMの説明によれば、「ソケットあたりの性能を(z15世代比で)40%向上させた」としている。

CPUコアを減らしてDPUを配置したTelum II

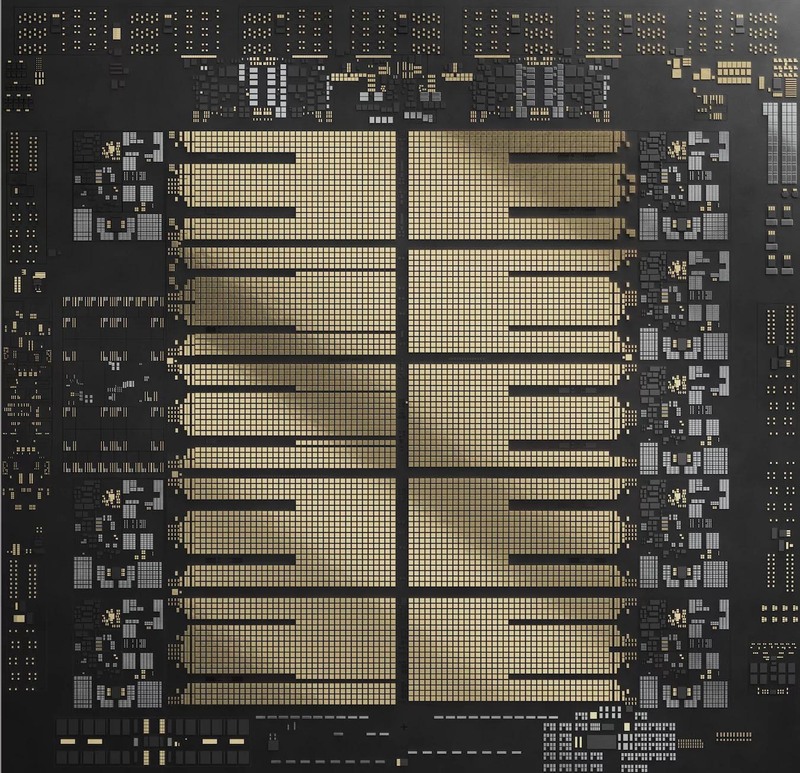

ということでやっとTelum IIである。Telum IIの写真として示されたのはこちらなのだが、これダイではなくパッケージ基板+αのようで、現時点でもダイの写真は示されていない。

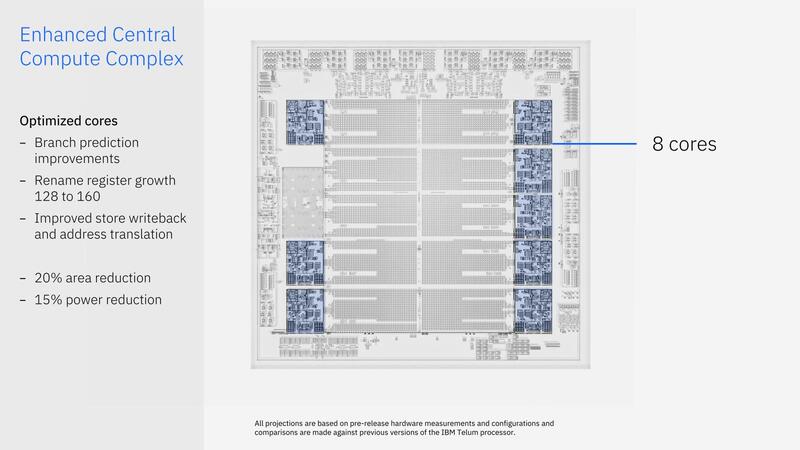

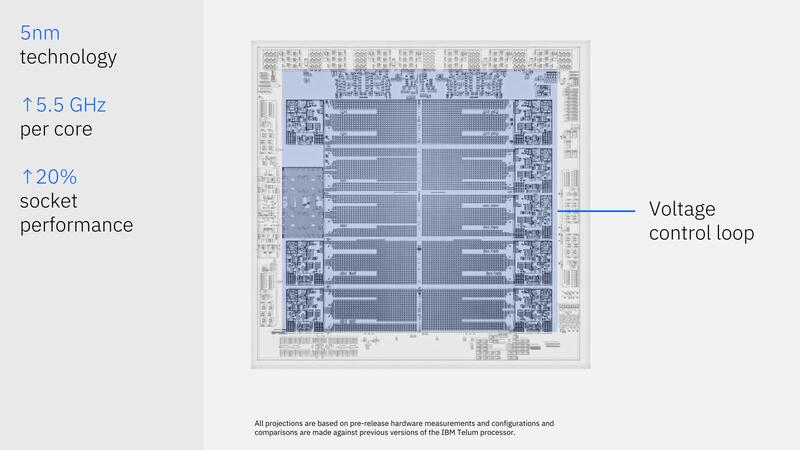

さて、Telum IIはSamsungの5nm(SF5:旧5LPPあたりと目される)を利用して製造されているが、CPUコアは8つに減ってしまった。

Area ReductionとPower Reductionはおそらく7nm→5nmにプロセスを微細化した効果だろう。ただしL2は36MBが10ブロック分が用意され、合計360MBとなっている。ややL2というサイズではなくなっている気がするが。

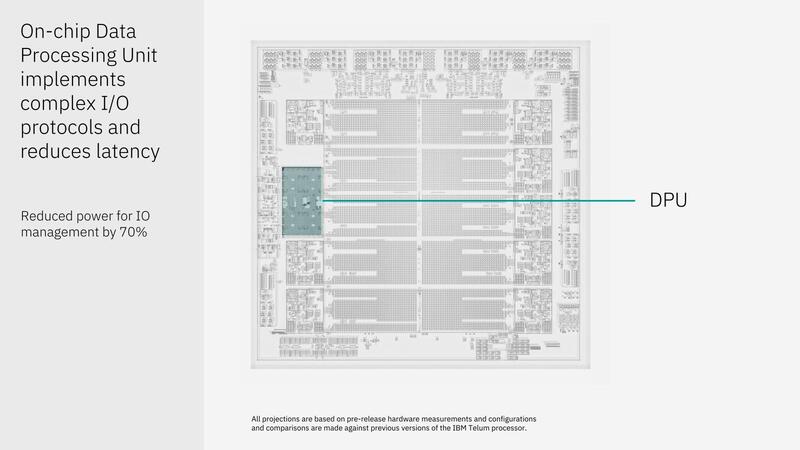

CPUコアを2つ減らしたところに収まるのがDPU(Data Processing Unit)である。これはインテルのMount Evansのように、I/Oの処理をオフロードするもので、これによりI/Oの制御に要する消費電力が70%削減できたとする。

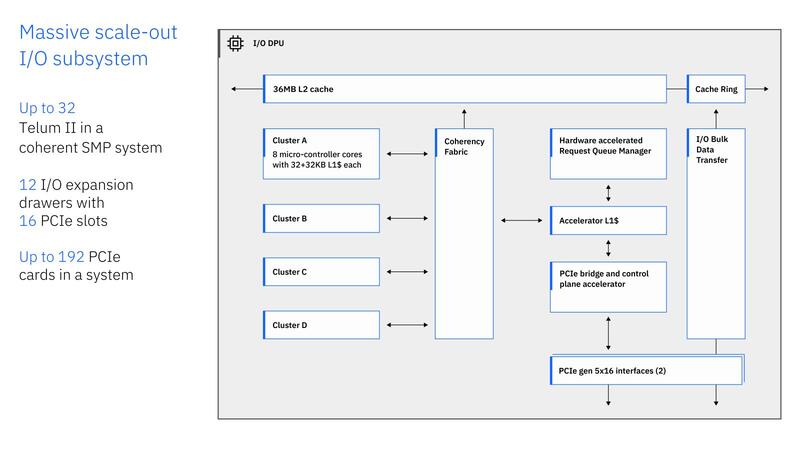

そのDPUの中身が下の画像だ。Cluster A~Dの4つのMCUコアクラスターがあり、おのおの8つのMCUが動作して、これがI/Oの処理を担っているようだ。ちなみにMCUとは言うが、中身は不明である。

さすがに今さらPowerPC 430などを使っているとは思えないので、Cortex-M7クラスのものだろうか? I/O周りの処理結果は、そのまま隣接するL2キャッシュに収められ、その内容はCPUコアからVirtual L3の先に格納されているものとして扱われる格好だろう。チップ1個あたり12個のPCIe Gen5 x16レーンが出るのも、このクラスのCPUとしてはかなりのものだ。

ちなみにCPUコアとL2、それとDPUに関しては、Voltage Control Loopの制御下に置かれており、このControl Loopの制御を有効にすることで最大18%の消費電力削減が実現したという。

PCIe x16カードの形で提供されるAI推論アクセラレーター Spyre Accelerator

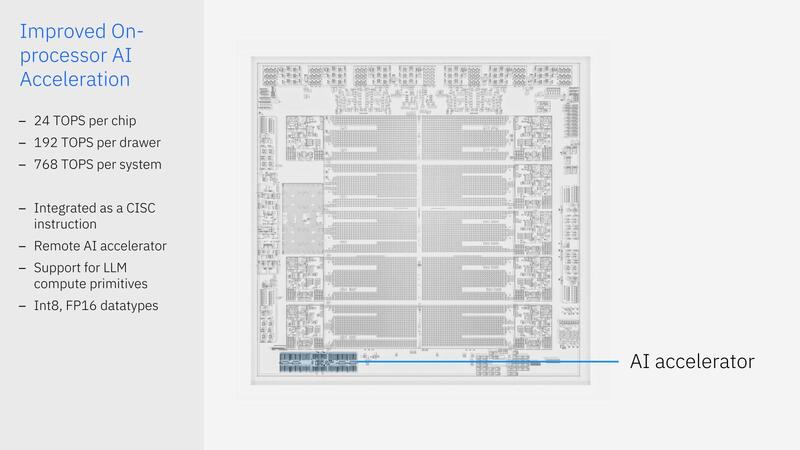

ところでAI推論アクセラレーターは当然Telum IIにも搭載されており、性能は24TOPSと4倍に向上しているが、もともとTelumの時代からプロセッサー性能と推論アクセラレーターの性能が釣り合っていなかった。

AI処理が多い処理を多数のプロセッサーでこなす、というケースにおいては、明らかにCPUによって推論アクセラレーターの取り合いになる。だからといってCPUの数だけ推論アクセラレーターを搭載するか? というと、それはそれで問題でダイサイズも増えるし、Telumプロセッサーを使うすべてのシステムが大量のAI推論処理を行なうとは限らない。

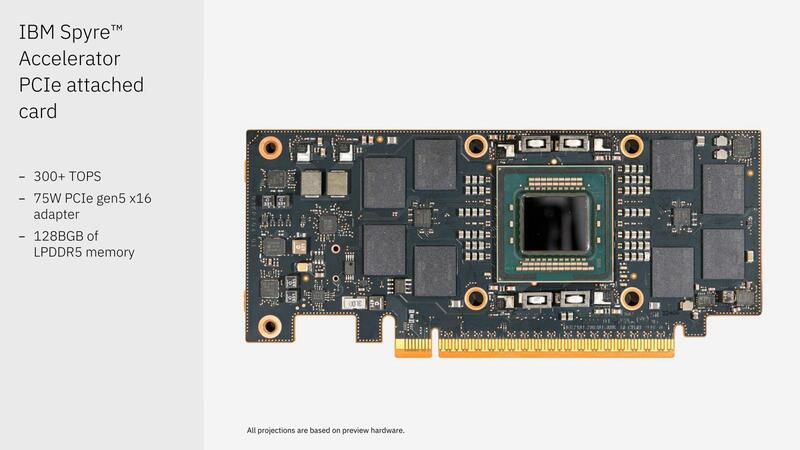

このあたりの条件に対する解が、Telum IIで登場したSpyre Acceleratorである。SpyreはPCIe x16カードの形で提供され、カード単体で300TOPS以上の性能とされる。このSpyreは最大8枚まで、I/Oドロワーに搭載可能、という説明になっている。

まだTelum IIを使ったシステム(おそらく順番から言えばIBM z17 systemになるのだろう)の詳細構成が不明なので推察するしかないのだが、どうもTelum IIでは1ドロワーあたり8チップ(80コア)が最大構成になりそうだ。

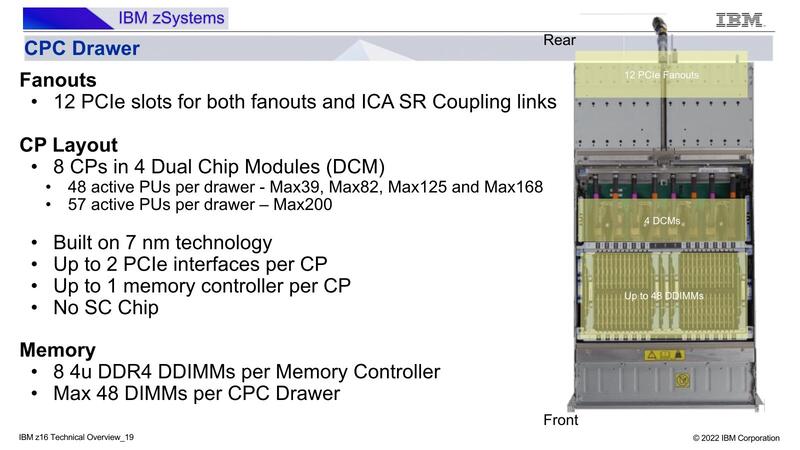

下の画像がz16 systemでのCPドロワーの構成であるが、Telum IIを搭載したz17でのCPCドロワーも似た構成であり、Storage、DIMM、CPU×8、PCIeカードという順序になり、その最後のPCIeスロットの部分にこのSpyreカード×8が収められ、1CPUあたり1枚のSpyreカードという感じになりそうである。

もっともこれは構成次第のところがあって、Spyreカードは別に用意される拡張カード専用ドロワーに収められ、CPCドロワーの方はイーサネットなどのネットワークカードだけになるかもしれない。

製品出荷はIBMのリリースでは2025年になりそうなので、もうしばらくは詳細な構成は明らかにされないと思うが、Xeon/EPYCなどのPC用プロセッサーから進化したサーバー向けプロセッサーとは明らかに異なる原理原則で設計されていることが垣間見られ、非常に興味深い構成になっている。

この記事に関連するニュース

-

ハイエンドスマホ向け新型SoC「Snapdragon 8 Elite」にみるAI半導体の進化

ITmedia PC USER / 2024年11月28日 19時40分

-

Microsoft 365 CopilotがNPUによるローカル処理に対応/「Google ドライブ」のArm版Windows 11ネイティブアプリ登場

ITmedia PC USER / 2024年11月24日 6時5分

-

日本が開発したAIプロセッサーMN-Core 2 Hot Chips 2024で注目を浴びたオモシロCPU

ASCII.jp / 2024年11月18日 12時0分

-

わずか2年で完成させた韓国FuriosaAIのAIアクセラレーターRNGD Hot Chips 2024で注目を浴びたオモシロCPU

ASCII.jp / 2024年11月11日 12時0分

-

Metaが自社開発したAI推論用アクセラレーターMTIA v2 Hot Chips 2024で注目を浴びたオモシロCPU

ASCII.jp / 2024年11月4日 12時0分

ランキング

-

1NHKのネット受信契約(案)が“ダークパターン”過ぎて見過ごせない件(前編) NHKの見解は?

ITmedia NEWS / 2024年11月28日 19時9分

-

2どうする? 大学生用パソコンの選び方 「4年通しよりも2年で買い替え」がオススメな理由

ITmedia NEWS / 2024年11月28日 13時26分

-

3「ミリ波対応スマホ」の値引き規制緩和で感じた疑問 スマホ購入の決め手にはならず?

ITmedia Mobile / 2024年11月28日 18時13分

-

4松屋が“店内持ち込み”で公式見解→解釈めぐり賛否 「何と言うサービス精神」「バレなきゃいいのか……?」

ねとらぼ / 2024年11月28日 20時2分

-

5えっ、プレステ2のゲーム高すぎ!? ここにきて中古ソフトが高騰している納得のワケ

マグミクス / 2024年11月28日 21時45分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください