第5世代EPYCはMRDIMMをサポートしている? AMD CPUロードマップ

ASCII.jp / 2024年10月21日 12時0分

Hot Chipsで公開された新プロセッサーの説明の途中であるが、10月10日にAMDがAdvancing AI 2024というイベントを開催したので、今回はAMD CPUのアップデートをお伝えしよう。

イベントのレポートはRyzen AI Pro 300とEPYC 9005としてすでに既載されている。このうちRyzen AI Pro 300シリーズに関しては、今年のCOMPUTEXで発表されたRyzen AI 300シリーズのビジネス向けのPro版というだけで、仕様的にもすでに出荷中のRyzen AI 300シリーズと同じ(Pro機能の有無が異なるだけ)なのであまり説明の必要がないのだが、EPYCについてはけっこう細かい情報が公開されたので、こちらを中心に説明したい。

第5世代EPYCは16CCDが物理的限界

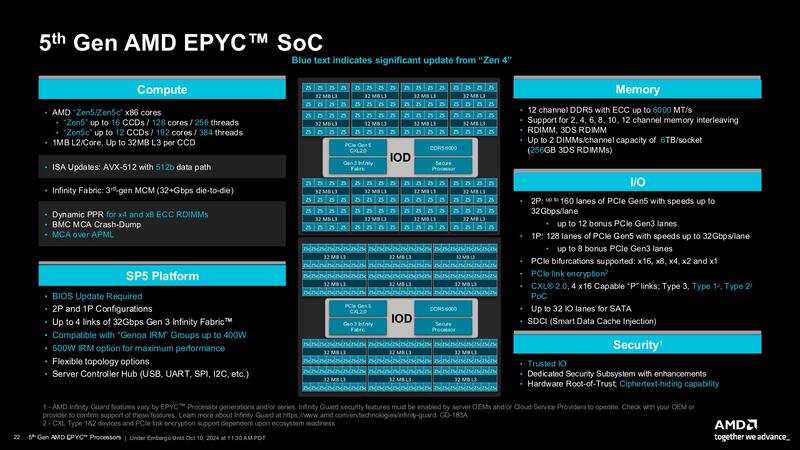

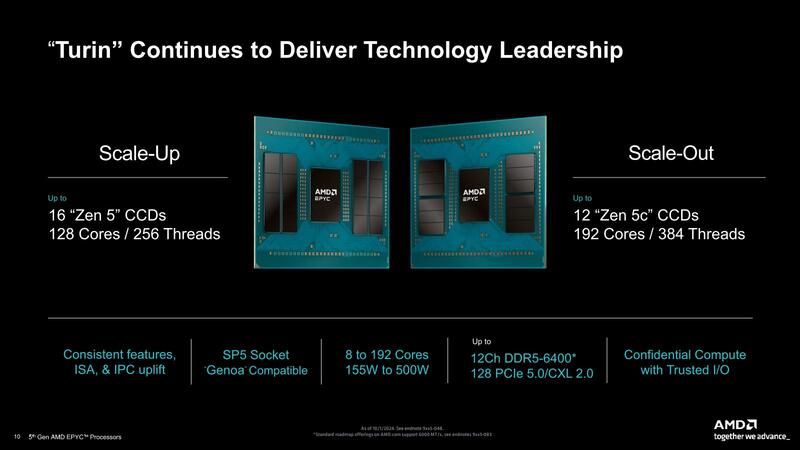

まずラインナップについてだ。連載776回で書いたように、TSMC N3を利用するのはZen 5cコアの場合のみで、Zen 5コアの方はTSMC N4となる。ここまでは想定通りであったが、IoDが予想通り大きく変更され、しかしながら筆者が想定していたMRDIMMのサポートは明示されなかった。その代わりだが、最大16個までCCDを接続できるようになった。

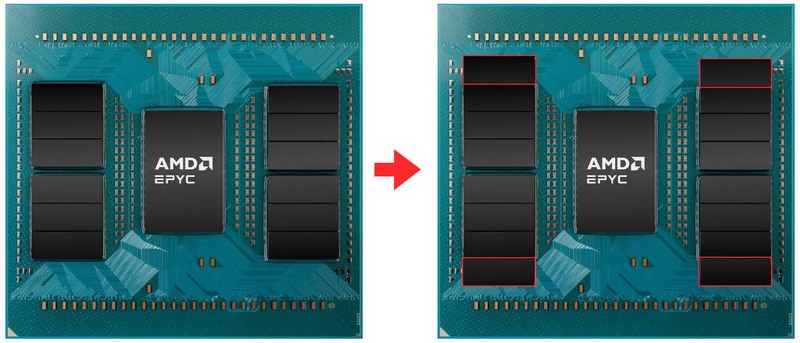

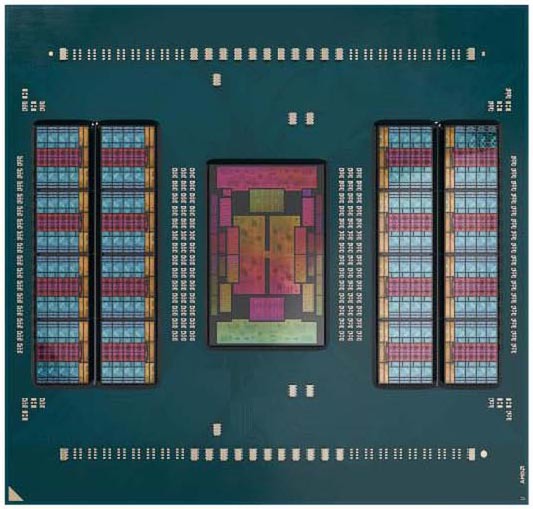

下の画像は少しわかりにくいが、中央の上半分がZen 5ベースのEPYC、下半分がZen 5cベースのEPYCである。

Zen 5ベースの場合、最大16個のCCDを接続可能で、この場合は128コア/256スレッドでの動作が可能になる。Zen 5cの場合は最大12CCDで、こちらでは192コア/384スレッドという計算になる。別にZen 5cではIoDに12CCD以上接続できないという話ではなく、物理的にSP5のパッケージに16個のZen 5cのCCDが載らないという制約から来るものと思われる。

これはZen 5のCCDの方も同じで、16CCDが上限であり、これ以上はパッケージを大きくする必要がありそうだ。

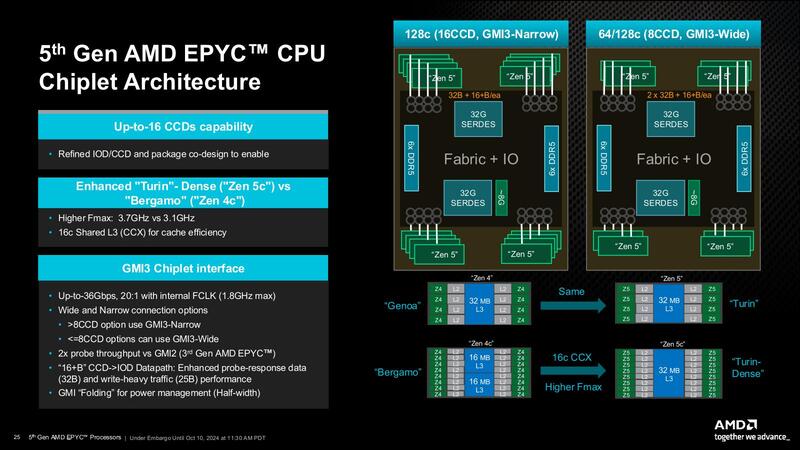

そうした話はともかくとして、IoDのインフィニティ・ファブリックのI/F(GMI3)はZen 4世代の12chからZen 5世代では16chに増やされた。もうこの時点でIoDは新しくなったことが明白である。

16 CCD/12 CCDのEPYCに関してはCCDとIoDが1本のGMI3で接続される形になるが、8CCDのEPYCに関しては2本のGMI3でCCDとIoDが接続される。この方式はGenoa世代でも採用されていたが、今回GMI3が合計で16ch分に増やされたことで、8 CCD以下の構成のEPYCはすべてこのDual GMI3(GMI3-Wide)構成での接続が可能になった。

SKUテーブルで言うと、64コアのEPYC 9575F以下の18製品がこれに該当する(ちなみにZen 5ベースのEPYCは全部で22製品なので、大半がGMI3-Wideの接続が可能になったことになる)。

Zen 5cベースのCCDはCCXあたりのコア数が16コアに増量 メモリーはDDR5-6000に対応

次にCCDそのものついて。Zen 5ベースのCCDに関してはこれはRyzen 9000シリーズと共通なので説明の必要がないが、Zen 5cベースのCCDについてはけっこう大きな変更があった。上の画像の右下にもあるが、CCXあたりのコア数が16コアに増量されているのである。

Bergamo、つまりZen 4cの場合は8コアCCXを2つ、1つのダイに収める形になっており、2つのCCXの間の通信は一度IODを経由する(しかも1chのGMI3を使って行なう)ためにおそろしく効率が悪かった。これはZen 4cの設計コストを最小限に抑えるための工夫であったが、Zen 5cでは当初からこのあたりの改善を図ったようで、16コアCCXに切り替わった。これにより1つのダイの中での通信のレイテンシーとスループットの両方が大幅に改善されたものと考えられる。

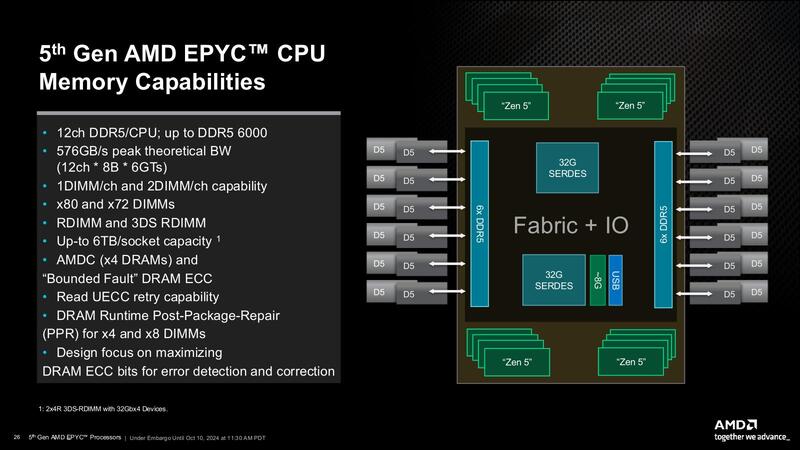

次にメモリー回りについて。まず対応するメモリーが最大DDR5-6000になった。

この表現が非常に微妙で、別のスライド(下の画像)には"12ch DDR5-6400"と書いてあったりする。

ただし脚注を読むと"5th Gen EPYC processors support DDR5-6400 MT/s for targeted customers and configurations. 5th Gen production SKUs support up to DDR5-6000 MT/s to enable a broad set of DIMMs across all OEM platforms and maintain SP5 platform compatibility"とあったりする。

要するに、メモリーコントローラーそのものはDDR5-6400まで対応できているが、現時点ではまだDDR5-6400のRDIMMや3DS DIMMが存在しておらず、検証が不可能である。検証できているのはDDR5-6000までなので、製品としてはDDR5-6000までをサポートしている、ということらしい。

第5世代EPYCはMRDIMMをサポートしている? 技術的にはサポートしておりJEDECでの標準化を待っている状態か

これにからんでもう1つ、MRDIMMに関して今回Gen 5 EPYCでは一切言及がなかった。ただ間接的な言及ではあるが、下の画像の下の方に"25% improvement in DRAM speed (4800 -> up to 6000) using JEDEC-standard (nonproprietary) DIMMs"という表現があるのがわかる。

これはなにを言っているかと言えば、連載786回で説明したようにXeon 6はMRDIMM-8800をサポートしており、こちらはDIMM 1chあたり70.4GB/秒の帯域を持つことになる。

MRDIMM-8800と比較すればDDR5-6000は48GB/秒なので帯域的にはおよばないが、問題はMRDIMMはまだJEDECでの標準化が終わっていないことだ。AMDとしては非標準のメモリーはサポートしないという方針を貫いており(EPYCだけでなくRyzenもそうだし、RadeonでGDDR6X DRAMをサポートしないのも同じである)、これは「JEDEC標準に準拠したメモリーを使いながら、DDR5-4800→DDR5-6000で25%帯域を増やした」と言っていることになる。

「ではJEDECでMRDIMMの標準化が完了したら、第5世代EPYCでもMRDIMMをサポートするのか?」という問い合わせをやはりAMDに投げている(が、返事はまだである)。AMDのMRDIMMへの取り組みが前向きであることを考えると、すでに技術的にはMRDIMMのサポートは完了しており、ただし標準品での検証が終わるまではサポート対象としない、といったアプローチではないかと思われる(これはDDR5-6400も同じであるが)。

リモートアクセスサーバー機能は ほぼXeonと肩を並べる性能

なお、第5世代EPYCは速度向上だけでなく容量も倍増した。これは256GB DIMMを公式にサポートしたことによるもので、最大でソケットあたり6TBとなる。ただしこれは2 DIMM/chの場合の数字で、1 DIMM/chなら3TBとなる。これに関しては、「速度を取るか、容量を取るか」になる。とはいえ3TB/ソケットであってもGenoa世代の最大容量と変わらないわけで、このあたりは大幅な強化としていいだろう。

上の画像は1Pおよび2Pにおける構成で、これは既存のSP5プラットフォームと互換性がある以上大きくは変更がない。2Pの方は、基本は4対のインフィニティ・ファブリックでプロセッサー間を接続する形になるが、I/Oを重視したい構成の場合は3対に減らし、その分PCI Expressレーンをx32利用可能とすることも可能だ(これはGenoa世代から変わらず)。

このあたりはSP5を利用するので抜本的に変えることは不可能だし、まだPCIe Gen6の登場には時間がかかることを考えれば変える必要もないと判断したものと思われる。

ただ注意点としては、一部SKUがTDP 500Wの設定になっていることだ。Gen 4 EPYCの世代は最大でも400W(EPYC 9684X)で、当初発表されたSKUは360W止まりだったから、一部のマザーボードは供給能力が足りなくなる可能性がある(たしかPlatform Guideでは当初は400W推奨であったと記憶している)。

幸いにも実際にSKUを確認すると、TDP 500Wが設定されているのはZen 5c 192コアのEPYC 9965とZen 5 128コアのEPYC 9755というハイエンド製品のみで、それ以外はすべて400W以下に収まっているためアップグレードに支障はほとんどないだろう。

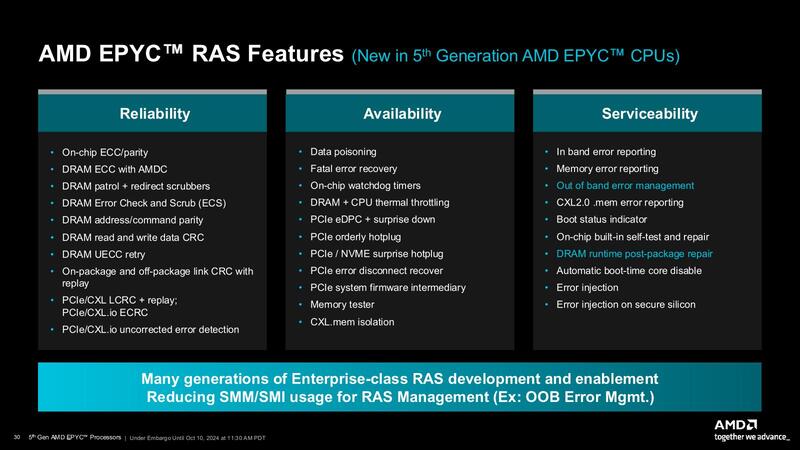

さて、RAS(Remote Access Server)機能のまとめが下の画像である。Reliability(信頼性)とAvailability(可用性)に関してはGenoa世代から変更はないが、Serviceability(保守性)に関してはOut of band error management(対象となる機器が稼働していなくてもエラー管理が可能:CPUとは別にシステム管理用の機構が独立して稼働しており、これを経由してシステムのエラー管理が可能になる)と、DRAM runtime post-package repair(PPR)のサポートが新たに追加された。

PPRはDRAMセルに故障が発生した場合、そのセルを含むRowを、冗長Rowと置き換えることで対処する方法である、ちなみにPPRには電源投入時に冗長セルに入れ替える(Hard-PPR)方式と、ソフトリセット時に冗長セルにマッピングし直す(Soft-PPR)方式があり、どちらをサポートしているのかは不明である。

性能についてはいくつかのスライドは示されているが、比較対象が5th Gen Intel Xeon、つまりEmerald RapidsでありXeon 6との比較は示されなかったので今回は割愛する。本来の競合製品はXeon 6であるが、現状はEコアベースのSierra Forestのみが出荷されており、Turinとの比較にはならない。

発表こそあったものの、未だに出荷されていないGranite RapidsベースのXeon 6が実際に市場に登場して、実アプリケーションベンチの結果などが出てくるまでお預けといったところだ。

この記事に関連するニュース

-

スーパーマイクロ、スーパーコンピューティング2024にてHPCに最適化されたマルチノードシステムの最大規模のポートフォリオを発表

共同通信PRワイヤー / 2024年11月22日 9時44分

-

GALLERIA、「AMD Ryzen 7 9800X3D」搭載パソコンを6製品発売

マイナビニュース / 2024年11月15日 12時59分

-

AMD、CXL 3.1/PCIe Gen6/LPDDR5に対応するアダプティブSoC「Versal Premium Series Gen 2」を発表

マイナビニュース / 2024年11月13日 6時45分

-

ゲーミングに最適化したキャッシュ爆盛りデスクトップCPU「Ryzen 7 9800X3D」正式発表 米国では479ドル

ITmedia PC USER / 2024年10月31日 23時40分

-

AI性能を引き上げるInstinct MI325XとPensando Salina 400/Pollara 400がサーバーにインパクトをもたらす AMD CPUロードマップ

ASCII.jp / 2024年10月28日 13時0分

ランキング

-

1【最新】Wi-Fiルーターだけはいいものを買え、今ならこれでキマリだ

ASCII.jp / 2024年11月23日 17時0分

-

2Switchで遊べるヴァンサバ系ゲーム5選!強化しまくって大量の敵を一掃する「俺TUEEE!」が超気持ちいい

インサイド / 2024年11月23日 15時0分

-

3普段は塩対応の柴犬に大好きな人が会いに来たら……? 別犬のような喜び方が270万再生を突破「お散歩ってワードにも、それで頼む」

ねとらぼ / 2024年11月23日 7時0分

-

4プロが教える「PCをオフにする時はシャットダウンとスリープ、どっちがいいの?」 理想の選択肢は意外にも…… 「有益な情報ありがとう」「感動しました

ねとらぼ / 2024年11月20日 22時0分

-

5「しぬwww」「怖すぎ」 かわいいカメを“絵文字ミックス”したら…… 爆誕した“バケモノ”が2200万表示 衝撃ビジュアルに「笑いすぎて涙」

ねとらぼ / 2024年11月23日 20時20分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください