酸化ハフニウム(HfO2)でフィンをカバーすると性能が改善、TMD半導体の実現に近づく IEDM 2024レポート

ASCII.jp / 2025年1月27日 12時0分

一週空いたが、IEDM 2024の第5弾は、24-3の"Gate oxide module development for scaled GAA 2D FETs enabling SS<75mV/d and record Idmax>900μA/μm at Lg<50nm"である。インテルのプレビューでは下のスライドに相当する話だ。

ゲート長30nmのGAA NMOS/PMOSを シリコンを利用せずに構築

論文の要旨は、ナノシート型FETにおけるシリコンの代替として、TMD(2次元遷移金属二カルコゲナイド)半導体の実現可能性を向上させることを目的とした、としている。

具体的にはゲート長30nmのGAA NMOS/PMOSを、シリコンを利用せずに構築するのが目的で、インテル独自のゲート酸化膜プロセス、それと改良型のゲートクリーニングの技法により、ゲート長50nm未満で厚さ1nm未満の単層MoS2チャネルを構築し、SS<75mV/decおよびIdmax>900μA/μmという記録的な値を達成した、としている。もっともいろいろ懸念事項もあるので、単純に喜んでいるわけでもないのだが、そのあたりは後ほど説明する。

発表の内容であるが、まずこの20年弱で急速にトランジスタが進化したというのはご存じのとおり。プレナー型と呼ばれる従来のトランジスタから、3次元構造のFinFETに移行し、間もなくナノシートを利用したGAAと呼ばれるトランジスタが出現しようとしている。

このプレナー→FinFET→GAAでどんどんゲート長を短縮できるようになったが、それでも限界というものはある。FinFETでは30nmあたりから急速に特性が悪化する。GAAではもう少し粘れるが、それでも20nmを切ったあたりからやはり悪化するというのがシミュレーションでの結果である。

これを打ち破るための方法はいろいろ模索されているわけだが、そのうちの1つがTMDと呼ばれるものである。連載806回でも紹介したが、フィンの厚みをどんどん減らそうとすると、他の特性が悪化する。これを打ち破るための材料の1つとして期待されているのがTMDであり、さまざまな研究がなされている。

TMDそのものは原子3つ分、厚みにしても1nm未満で構成できるから、薄膜化を目指すには最適な材料である。

特にこの研究の場合、ターゲットとなるのは将来のCFET向けである。

次がCFET、という話は連載803回や連載806回でも出てきた話なので繰り返さないが、これは業界的には妥当な流れと判断されているようだ。

ただし当然ながら課題も多い。そもそもウェハーサイズ、つまり直径300mmのリボンを欠陥なく構成できるようにしないといけないというのが最初の問題だし、積層する場合のコンタクト、つまり配線層をどう作り込むかというのも問題である。またCFETに関しては、まだ実験室レベルでの積層に成功したレベルの話であって、量産で流せるような製造手法そのものが確立できていない。

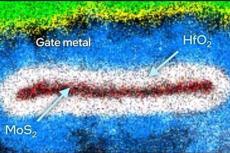

現在におけるTMDを利用したGAA FETの構築方法が下の画像である。

ALD(Atomic Layer Deposition:原子層堆積法)という技法を利用して、ゲートの周囲にHfO2の膜を積層している(水色の部分がHfO2の膜である)。このHfO2の膜を構築することで、SSsat(Subthreshold Slope saturation:しきい値以下スロープ飽和)とDIBL(Drain Induced Barrier Lowering:ドレイン誘障壁低下)という、トランジスタ特性を示す2つの値がどちらも改善されているとする。

インテルがHfO2成膜を実現

ここからが今回の発表の内容である。従来のMoS2にHfO2を積層するプロセスでは、Dangling Bond(原子における未結合手)が存在せず、このためHigh-Kでの膜形成が難しかったため、Low-Kでの膜形成層が必要になっていた。

ところがインテルは今回、HfO2 ALDプロセスを改良し、原子レベルでシャープな界面を持つ、均一でピンホールのないHfO2成膜を実現したとする。これによりLow-Kの膜を入れる必要がなくなり、それだけ特性が改善されるとする。

この技法を利用してGAAのフィンを構成したのが下の画像だ。厳密に言えばまだこれはGAAを構成する途中である。左はMoS2のシートの周囲にHfO2の膜を形成した状態だが、まだ周囲に炭素が大量に残っている。これを洗浄などによりキレイに取り除いたのが右の状態だ。

ちなみにこの洗浄の行程についても比較しており、摂氏50度という低温での洗浄でもGAAの歩留まりはわりと高い数値(66%)を維持できる一方、温度を上げるとチャネルの機械的な欠陥、あるいは剥離に起因するOpen Channel(つまりチャネルが構成できなくなる)の頻度が2倍以上に上がったそうだ。

この工程を経て最終的に構築されたGAAが下の画像である。左のClean 1とClean 2は従来発表されてきた研究の際のもので、Clean 3が今回の研究の成果である。

Clean 1/2と比較した場合、Clean 3のSSsatは121mV/dから101mV/dに減少し、それでいて3Vの固定オーバードライブにおける駆動電流は197μA/μmから297μA/μmとおよそ1.5倍に向上している。DIBLは111mV/Vから76mV/Vに減少している。

インテルはこの効果はHfO2/MoS2/HfO2界面の清浄度/品質の改善によるものと考えているとのことだ。

ちなみにコンタクト部の抵抗Rcの数値は、大規模なGAAデバイスがまだ存在しないので直接測定できず、Vd/Id(電圧/電流カーブ)からの推定とのことだが、インテルによればこれは蒸着コンタクトスタックの最適化値に近いとしている。

ゲート長を60nmから30nmまで短縮すると性能が出ない

次にこの状態でゲート長を60nmから30nmまで短縮した場合の特性を調べたのが下の画像である。

左側のグラフで、SSsatなどはそれほど大きな違いはないが、DIBLがLg=60nmの時は17mV/Vと低い値なのが、30nmまで短縮すると177mV/Vまで増加しているのがわかる。これはさらなるEOT(Equivalent Oxide Thickness:等価酸化膜厚)スケーリングが必要、というのがここでの結論である。

右側は2Vでのオーバードライブ駆動時の駆動電流を比較したもので、Lgを30nmにすると顕著に電流が劣化する。これはチャネルの形状が劣化することで、不十分な構成のGAAが形成されてしまい、GAAの利点が失われてしまうためで、これに関してさらなる最適化が必要、としている。

GAA NMOSトランジスタの新たな限界要因はHfO2膜の厚み

次はHfO2膜の厚みが性能におよぼす影響の比較である。HfO2はALDを使って積層するので、その回数を調整することで厚みを変化させられる。

論文では3.7nm/4.2nm/4.6nmの3種類の厚みを構成して、それぞれの特性を比較した。ここでClean 1/Clean 3は4つ上の画像と同じで、Clean 1が従来の手法、Clean 3が今回の手法だ。Clean 1の場合、膜厚を変化させてもほとんど特性が改善されない。

これは酸化膜の界面に残留した炭素汚染がEOTスケーリングを妨げたためと判断されており、逆に今回のClean 3では特に4.6nmにするとSSsatが明確に改善したが、3.7nm厚ではその改善効果が減少するとしている。Clean 1と比較して最適化が進んだClean 3でもこの限界がみられるというのは、GAA NMOSトランジスタの新たな限界要因になり得ることを示している

下の画像はチャネルと高誘電率酸化膜の界面に関する研究である。これはALDで構築したHfO2バックゲート基板上に、40×40nmという非常に小さなチャネルを構築し、このCV測定をした結果、4nmで1.4nm相当、8nmでは2.1nm相当のEOTになることがわかった。

ここから、vdWギャップ(van der Waals:ファンデルワールス決勝のバンドギャップ)、残留分、潜在的な剥離などが0.8nm相当のEOTになることが判明した、としている。

NMOSとPMOSの違い PMOSはNMOSとは逆の傾向

ここまでの話はNMOSベースだったが、ではPMOSではどうか? ということで性能を確認したのが下の画像である。

一般論としてWSe2を利用したPMOSは、同じ構成のNMOSに劣っている。これは材料の接触抵抗と潜在的な欠陥の増加が主な課題とされている。これに対する研究の1つとして、蒸着Ru(ルビジウム)を利用したコンタクトは、Au(金)のコンタクトよりIdmaxを向上させられるという話が2023年のIEDMで発表されている。

これを一歩進め、Ruでソース/ドレインのコンタクトを形成した際の、膜厚のスケーリングを確認したのが画像真ん中のグラフである。膜厚を減らした場合、Imaxが132μA/μmにに増加し、一方でSSsatは156mV/dという記録的な値を得られたとしている。

ただこれはNMOSとは逆の傾向であり、その要因としてはNMOSとPMOSで異なる制限要因があるか、もしくはPMOSとNMOSで界面の相互作用の違いに起因する可能性があるが、これに関しては今後の研究課題としている。

最終的な結論が下の画像で、これまで発表されたTMDベースのGAAトランジスタとしては一番良い成果を得られているが、ただしまだ目標を完全に達成できているわけではなく、今後もさらに研究を続けていくとしている。

ということで、こちらはまだ量産以前の基礎研究に近い内容であり、この成果が実際の量産製品に反映されるのはおそらく2030年以降のことになると思われる。

この記事に関連するニュース

-

ソフトバンク"脳細胞"を活用する異例の取り組み 次世代のAIとして2050年の実用化を目指す

東洋経済オンライン / 2025年1月24日 9時0分

-

ミニLEDディスプレイ向けにLED素子の映り込みを抑える光拡散フィルムを開発

PR TIMES / 2025年1月16日 12時15分

-

トランジスタ最先端! RibbonFETに最適なゲート長とフィン厚が判明 IEDM 2024レポート

ASCII.jp / 2025年1月13日 12時0分

-

水素発生と半導体応用を兼ね備えた二次元半導体ナノリボンを実現

共同通信PRワイヤー / 2025年1月9日 10時0分

-

AI向けシステムの課題は電力とメモリーの膨大な消費量 IEDM 2024レポート

ASCII.jp / 2024年12月30日 12時0分

ランキング

-

1人気アニメ続々登場の「異世界∞異世界」サービス開始! 「無職転生」ルーデウスらに会える♪

アニメ!アニメ! / 2025年1月27日 16時30分

-

2M4搭載「Mac mini」を試して分かった注意点

ITmedia PC USER / 2025年1月27日 12時0分

-

3ガイドライン改正でスマホ価格はどう変わった? iPhoneとPixelで明暗、お得な端末はコレだ

ITmedia Mobile / 2025年1月27日 11時39分

-

4フジテレビの記者会見が「SMAPの謝罪会見にそっくり」の声 「10年前のスマスマ……」「まさかの」

ねとらぼ / 2025年1月27日 20時31分

-

5PSストア2024年の年間ダウンロードランキング発表! PS5の1位は『FF7リバース』

マイナビニュース / 2025年1月27日 17時17分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください