銅配線をルテニウム配線に変えると抵抗を25%削減できる IEDM 2024レポート

ASCII.jp / 2025年2月3日 12時0分

昨年12月7日~11日にかけ、サンフランシスコでIEDM(International Electron Device Meeting) 2024が開催された。今回のIEDM2024第6弾で紹介するのは39-2の"Subtractive Ruthenium Interconnects with Airgap"である。インテルのプレビューでは下の画像に相当する話だ。

Cu配線をRu配線に変えると抵抗を25%削減できる

要旨はダマシンを利用してCu(銅)配線を利用する代わりに、サブトラクティブを利用してRu(ルテニウム)配線を形成したところ、25nm未満の配線ピッチで最大25%の抵抗を削減できたというものだ。もっとも単にRu配線だけでなく絶縁層にAir Gapを併用するなど、いろいろ工夫が凝らされている。またRuの抵抗を最大15%低減する技法についても併せて発表された。

ここしばらくの間、ロジック回路の性能や密度に関して支配的なのはトランジスタそのものよりも、それをつなぐ配線層の方である。下の画像はこの背景を説明したものだが、左はトランジスタ数の増加傾向を示したもの、右はこれにともない配線のピッチがどんどん微細化されていることを示したものだ。

当たり前の話で、面積あたりのトランジスタの数が増えるということは、トランジスタ同士をつなぐ配線の数がそれだけ増えるわけで、これを一定面積の中に押し込もうとしたら配線自身の幅と配線の間隔のどちらも狭める必要がある。結果、配線のピッチ(と配線の幅そのもの)も、トランジスタの増加の逆数に比例するように狭まるのは致し方ない。

この配線を狭めると、特に銅配線ではいろいろと問題が出てくる。ある程度の幅がある時には抵抗も少なく、コストも低い銅であるが、幅が狭まってくると配線抵抗が急激に増える傾向がある。

またエレクトロマイグレーションと呼ばれる問題も出てくる。最初にこれに触れたのは連載464回で、とりあえず最初の10nm世代ではこのエレクトロマイグレーション対策としてCo(コバルト)を使ったら、今度は配線抵抗が銅よりも増えてしまい、足を引っ張ることになったので10nm世代で一度配線の実装のやり直しが発生したという話を連載483回で説明した。

この対策がIntel 7で採用された、Cu配線の外側にTaN(窒化タンタル)のバリアを被せたTaN with Cu Alloyと、同様にCo配線の外側にTa(タンタル)のバリアを被せたTa barrier with Co linesであり、これはIntel 4ではCuヒア線の外側にコバルトの膜を作り、さらにその外側をTaのバリアで覆うTa/Co with pure Cuに進化した。

エレクトロマイグレーションの対策をしながら、なんとか配線抵抗を減らすべく苦労した結果である。もっともこれはIntel 4/3や、おそらくIntel 20A/18Aあたりまではこれでいけるだろうが、その先のIntel 16Aやさらにその先になると、より一層配線密度を上げる必要が出てくるから、このまま使えるかどうかは不明である。

トランジスタの裏側から太い配線で電力を供給

Ru配線に加えてもう1つ有望視されていたのが、BSPDNである。インテルはこれをPowerVIAと呼んでいるが、要するに電力供給はトランジスタの裏側から行なうことで、配線層の混雑を緩和するとともに、電力供給の配線を太くすることで配線損失を減らそうという試みである。

最初にアナウンスがあったのは2021年であり、2022年にはもう少し詳細が発表され、2023年にはIntel 4での実装の様子も説明された。ただ本来最初に実装される予定だったIntel 20Aがキャンセルになった関係で、今年後半に量産開始予定のIntel 18Aで初めてPowerVIAが採用される予定である。

そんなPowerVIAというかBSPDNであるが、これは一時的に配線密度の緩和にはなっても、この先は再び配線密度が上がるのが見えている、というのがインテルの説明である。そんなわけで抜本的な新しい配線材料というか配線の構造が求められつつあるわけだ。

ここでRu(ルテニウム)を採用する理由、というより現在のCuベースではこの先の微細化が難しいという理由が下の画像だ。

これはダマシンを利用したCu配線の製法で、まず誘電体(図中水色)から配線が入る部分を削り、ついでそこにバリアの層を構成してから、最後にCu(図中金色)を埋め込むという手法である。これには以下の課題がある。

- 配線を微細化しても、バリアの厚みそのものは減らないから、相対的にバリア層の比率が配線の断面積の中で増えることになり、これは抵抗の増加につながる。

- 配線の抵抗を下げるためには断面積を増やすのが効果的で、ただしこの図で言えば横方向はもう広げられない(というか狭められている)ので、高さを引き上げる(アスペクト比を上げる)ことが望ましいのだが、そのためには深い溝を均一に彫り、そこに欠陥なく銅を埋めるという処理が望まれ、ところがこれが難易度が高い。

- ダマシンの加工により誘電体にダメージが生じ、これにより誘電率が高くなる(=静電容量が増える)といった問題が出てきており、もうCoのライナーでカバーできるレベルの問題ではなくなってきているのが現状である。

一方Ruベースでは配線を構成するのにサブトラクティブと呼ばれる手法を使う。要するにダマシンの逆で、まず配線材料(つまりRu)を全面に構成し、そこから要らない部分を削って誘電体を埋め込むという手順になる。

メリットとして以下の項目が挙げられている。

- 誘電体を掘り下げるより、Ruを掘り下げる方が高いアスペクト比を構築しやすい

- 誘電体を後から埋め込めるので、より低い誘電率の材料を使いやすい

- Air Gapを作りやすい

このうちAir Gapとは誘電体として空気を使うというものだ。空気は非常に誘電率が低い(真空の誘電率が1.0と定義されており、空気は1.0006程度になる)ため、寄生容量を大幅に減らせるというメリットがある。ただ従来のダマシンではAir Gapを構成するのが非常に難しかったが、サブトラクティブではこれが容易に構成できる。

下の画像は、ピッチ20nmと25nmでCuおよびRuで配線を構築し、その際の配線抵抗と寄生容量を比較したものだ。さらにRuに関してはAir Gapの有無も同時に比較している。

最終的に重要なのはRとCの積になるが、25nmの方ではRuのメリットは(Air Gapなしでは)あまりないのだが、Air Gapにすることで寄生容量を3割近く減らせる。一方20nmにすると、Ruは抵抗も下がる上に寄生容量も減らせ、しかもAir Gapを構成することでさらに寄生容量が減るとする。配線微細化が進む中では、CuをRuに置き換えるのが非常に有望、ということがおわかりいただけるかと思う。

Ru配線にAGを併用すると配線遅延を大幅に改善できる

下の画像はそのRu配線で、配線ピッチとアスペクト比を変えながらいろいろ試作した結果である。アスペクト比を4まで引き上げると、どんどん配線領域の面積が増大し、これにともない配線抵抗が下がっているのがわかる。

そのRuの最適化の効果を検討したのが下の画像である、Thin Filmとあるように、これはまだパターニング(配線構成)の前段階、まだエッチングを行なわず全面Ruの膜が覆っている段階での比較である。ここでは接着層やRuの蒸着条件、および蒸着後の主要な処理などについて4種類の最適化技法を行ない、その結果を比較したものである。

Bundle 1とBundle 4で比較すると、Bundle 4の方が配線抵抗が7%ほど減少したとしている。では大きめの結晶になるといいのか? というとそういうわけでもないようで、実際にはOptimization Package 3が一番性能が良く、16%の抵抗削減が実現できたそうだ。

次がAGの効果を示すパラメーターである。要するに誘電体の中にAGを構築するにあたり、どの程度のAGだと効果的か、を示すものだ。横軸は溝の高さそのものである。結果から言えば、部分的にAGを入れるだけでも25%程度寄生容量を減らせ、100%のAGを構成できればさらに効果が高まる可能性がある、としている。

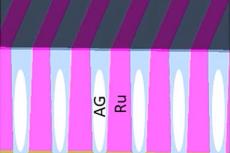

下の画像は実際にAGあり/なしでRuベースの配線層を構築したもので、配線ピッチ25nmでも間の溝にAGが構成できることを示している。

下の画像、は実際にサブトラクティブで形成したRu配線層とその上層の配線層との接続されている様子と、さらに信号の劣化を比較したものである。少なくともこのレベルで言えば、VIAとの接続による信号の劣化などは確認できず、通常のCu配線の場合と明示的な差はない、という結論になったとする。

また配線層の構成にあたっては、VIAのPunch-throughという現象を防ぐ必要がある。これは垂直方向の貫通VIAがAGを「突き抜けてしまう」ことだ。

従来はこれを防ぐため、隣接する次のVIAにAGが構成されないように、余分なパターニング作業が必要になっていた。ところが今回意図的にVIAを本来の位置とずらして構成したところ、確かにVIAは変な位置に構築されたが、それがAGを壊したり突き抜けたりしていなかった。要するにAGを利用するための余分なパターニング作業を省けることが確認できた、としている。

結論としては、Ruを利用することでより微細化した配線層を現状のプロセスの延長で製造可能であり、配線抵抗を大幅に減らせるほか、AGを併用することで寄生容量も減らせ、結果として配線遅延の問題を大幅に改善でき、今後のトランジスタ微細化にともなう配線密度向上にも耐えられる「可能性がある」ことが示された、とする。

問題はまだ実際に高密度配線が可能かどうかは不明なことで、次はピッチ10nm台の配線層構築などを実際に行なってその特性を調べる必要がある。また(これはCoも同じだが)Ruは熱伝導率が低いことや、貴金属ということでコストが高いこと、あと変わったところでは他元素と混ざりやすく、リサイクルが大変といった問題もある。こうした問題を解決しつつ、実際に製品に採用されるようになるのは、これも早くて2030年代以降だろうと思われる。

この記事に関連するニュース

-

酸化ハフニウム(HfO2)でフィンをカバーすると性能が改善、TMD半導体の実現に近づく IEDM 2024レポート

ASCII.jp / 2025年1月27日 12時0分

-

量子コンピューターの大規模化を支える材料評価技術

共同通信PRワイヤー / 2025年1月16日 0時0分

-

「第39回 ネプコンジャパン」に住友金属鉱山と伸光製作所が共同出展

PR TIMES / 2025年1月15日 13時15分

-

トランジスタ最先端! RibbonFETに最適なゲート長とフィン厚が判明 IEDM 2024レポート

ASCII.jp / 2025年1月13日 12時0分

-

PCテクノロジートレンド 2025 - Memory編「DDR」「MRDIMM」「GDDR」「HBM」

マイナビニュース / 2025年1月5日 10時0分

ランキング

-

1「正直破格です」 成城石井の元店長が辞めてからも買い続ける“名品”がリピ必至 「ヨダレが出そう」

ねとらぼ / 2025年2月2日 7時0分

-

2超初心者向けの“RAW現像入門”的な話

ITmedia NEWS / 2025年2月2日 8時20分

-

3PC版『Marvel’s Spider-Man 2』Steamで頻繫なクラッシュや不具合などの最適化不足を指摘され“賛否両論”に

Game*Spark / 2025年2月3日 13時15分

-

4mineo、50GBコースを追加! 春商戦キャンペーンでは20GBが6ヵ月間、月990円で利用可に

ASCII.jp / 2025年2月3日 13時30分

-

5DeNA、決済サービス「DeNA Pay」の提供を開始 DeNAベイスターズアプリ「BAYSTARS STAR GUIDE」と連携

ポイ探ニュース / 2025年2月3日 13時21分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください