【東芝デバイス&ストレージ】トランスを不要にした独自のStar-Deltaスイッチング回路方式で業界最高の電流密度の48V入力1V出力DC-DC電源ICを開発

Digital PR Platform / 2024年6月28日 11時50分

2024-6-28

東芝デバイス&ストレージ株式会社

トランスを不要にした独自のStar-Deltaスイッチング回路方式で

業界最高注1の電流密度の48V入力1V出力DC-DC電源ICを開発

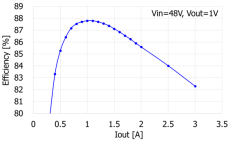

当社は、トランス(変圧器)を不要にした、独自のStar-Deltaスイッチング回路方式を開発し、業界最高注1の最大790mA/mm2の高い電流密度で最大88%と高い電力変換効率を実現した48V入力1V出力のDC-DC電源ICの動作を確認しました。本ICの実現により、大電流向け高電圧DC-DC電源の小型化および高効率化に貢献します。

近年、サーバーやデータセンター向けのDC-DC電源では、負荷側の大電流化に伴い、負荷側とともに入力側の導通損失注2も膨らんでいます。この損失の削減のために、入力電圧を12Vから48Vへ引き上げる規格化が進行していますが、従来のBuck回路方式で入力電圧の4倍引き上げに対応するには、パワースイッチを駆動するパルス幅を1/4に小さくする必要があり、スイッチング損失の増大により電力の変換効率が低下してしまいます。このため、トランスを用いてパルス幅を拡大する絶縁回路方式が主流となっていますが、この場合トランスを用いる分だけ実装体積が大きくなるため、インダクターとキャパシターを融合したハイブリッド型非絶縁回路方式注3が登場し、従来の絶縁型回路方式に比べて実装体積を1/10~1/100に削減できるようになりました。しかし、パルス幅の拡大倍率あたりに0.8~1.0個のキャパシター数注4を外付けする必要があるため、外付け部品の増加やIC周りのピン配線が複雑化し、実装コストが増加するという新たな課題が生じています。

そこで、当社は、電流が少ない入力側のスイッチングレイヤー注5を統合し、パルス幅の拡大倍率あたりのキャパシター数を0.5~0.6個に削減する独自のStar-Deltaスイッチング回路方式(図1)を開発しました。電源をオンするとStep1~4のスイッチングを繰り返し、Step1ではキャパシターをStar配置注6、Step3ではキャパシターをDelta配置注7したことが特徴です。スイッチングレイヤー毎にキャパシターが1個以上必要なため、スイッチングレイヤー数を最適化すれば、キャパシター数も減らすことができます(図2)。従来方式では48V入力電圧から複数の均等なスイッチングレイヤーを生成しますが、本方式では電流が少ない入力側のスイッチングレイヤーを統合し、キャパシター数を削減しました。この統合においては高耐圧スイッチの使用が必要ですが、電流が微小であり高耐圧スイッチの大きさを最小限に抑えることができるため、従来方式の複数の低耐圧スイッチとほぼ同じ面積であることを確認しました。

この記事に関連するニュース

-

テクトロニクス、電化を進めるエンジニアの革新を強力にサポートする画期的なパワー計測ソリューションを発表

PR TIMES / 2024年11月12日 16時45分

-

Grandiosoシリーズ初のフォノアンプ「Grandioso E1」を新発売

PR TIMES / 2024年11月7日 17時45分

-

スマホ、ウェアラブル機器向け1セルバッテリー保護IC「S-821A/S-821Bシリーズ」発売

@Press / 2024年10月31日 10時0分

-

Vicor、48V EVシステムに適用可能な車載グレード電源モジュール3製品を発表

マイナビニュース / 2024年10月30日 6時26分

-

アルプスアルパインIC外販 第二弾 電流リップル検出IC

Digital PR Platform / 2024年10月28日 15時0分

ランキング

-

1サンリオ株、三菱UFJや三井住友銀などが売却 約1335億円

ロイター / 2024年11月26日 16時58分

-

2「牛丼500円時代」の幕開け なぜ吉野家は減速し、すき家が独走したのか

ITmedia ビジネスオンライン / 2024年11月26日 8時10分

-

3【新NISA】50~60代から投資を始めるのは遅い?…メガバンク出身YouTuberが月1,000円ずつ投資した3つの銘柄「たった2年」で驚きの結果

THE GOLD ONLINE(ゴールドオンライン) / 2024年11月26日 9時15分

-

4激混み国道23号と1号を“直結” 桑名の川沿いを行く新道開通 たった720mでも「かなり便利じゃないかコレ…!?」

乗りものニュース / 2024年11月25日 7時42分

-

5「会社がつらい」同期トップ入社の彼に起こった事 「発達障害グレーゾーン」の人たちの特徴とは?

東洋経済オンライン / 2024年11月26日 14時0分

複数ページをまたぐ記事です

記事の最終ページでミッション達成してください