トランジスタの当面の目標は電圧を0.3V未満に抑えつつ動作効率を5倍以上に引き上げること IEDM 2024レポート

ASCII.jp / 2024年12月23日 12時0分

12月7日~11日にかけ、サンフランシスコでIEDM(International Electron Device Meeting) 2024が開催された。今年はIEDMの開催70周年となっており、昨年にもまして多くの発表が行なわれた。

今年のテーマは"Shaping Tomorrow's Semiconductor Technology"となっており、実際次世代向けのプロセスに関する話題が多く発表されている。

TSMCもN2プロセスの詳細やその次の世代向けのCFET(Complementary FET:後述)の試作などを発表しているし、ほかにもimecをはじめ各社がいろいろな成果を公開している。これを全部説明していると1年くらいかかるので、いくつかを紹介するにとどめたいわけだが、幸いにもインテルがIEDMの直前にプレビューを公開しており、こちらの記事で概略が紹介されている。

2005年まではプロセス微細化による高性能化が続く

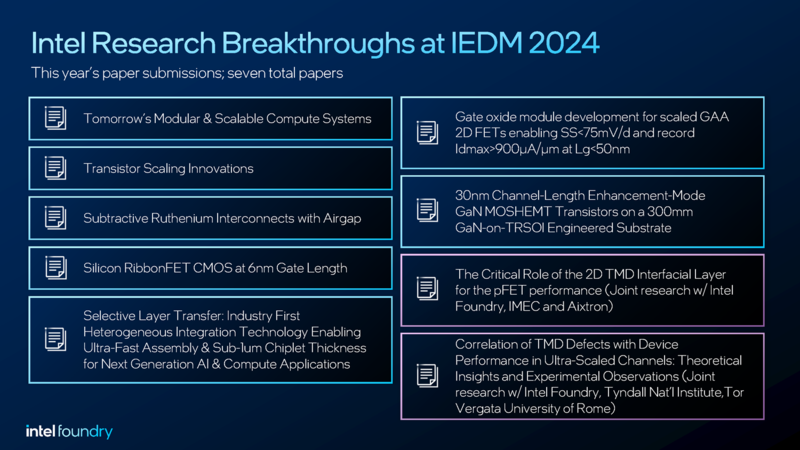

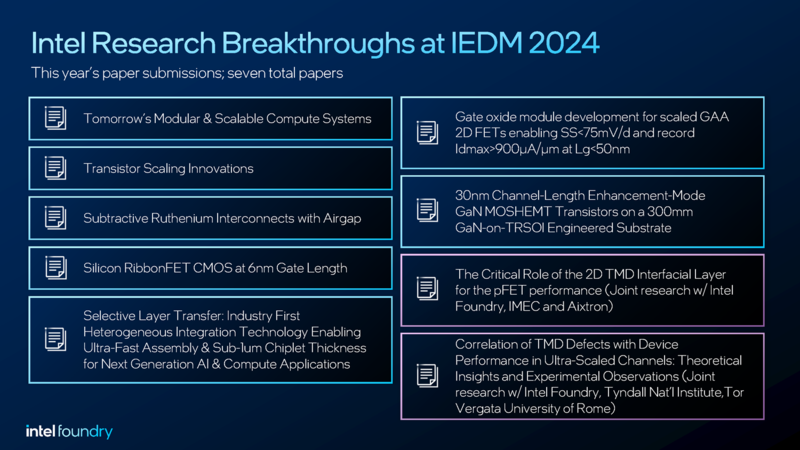

プレビューはプレビューでしかないので、いくつか選んでもう少し詳細に説明しよう。今回のテーマは、下の画像の左側上から2番目、"Transistor Scaling Innovations"という招待講演だ。ちなみに正式タイトルは28-1 "The Incredible Shrinking Transistor - Shattering Perceived Barriers and Forging Ahead"である。

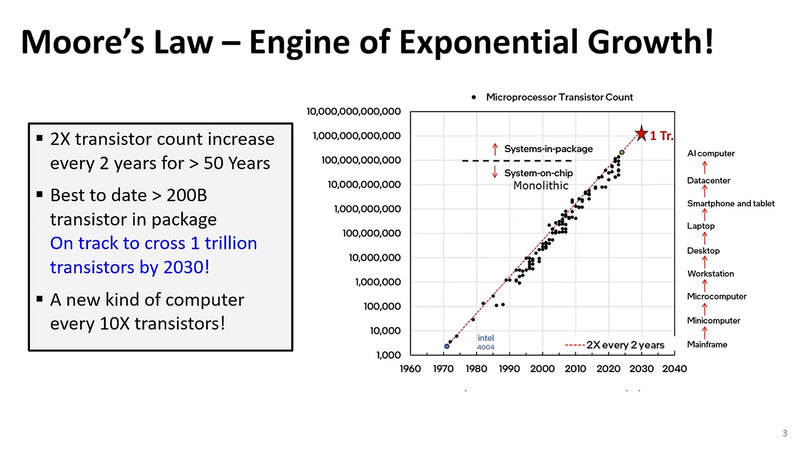

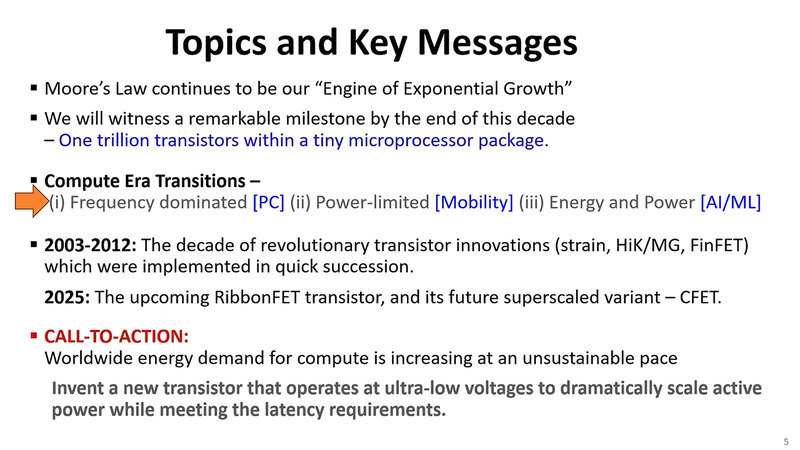

まずはムーアの法則がなんだかんだと言いながらまだ成立し続けていることに触れ、引き続きムーアの法則が業界の牽引力になっているとしたうえで、話を2005年まで、2005年~現在、今後の3つに分割した。

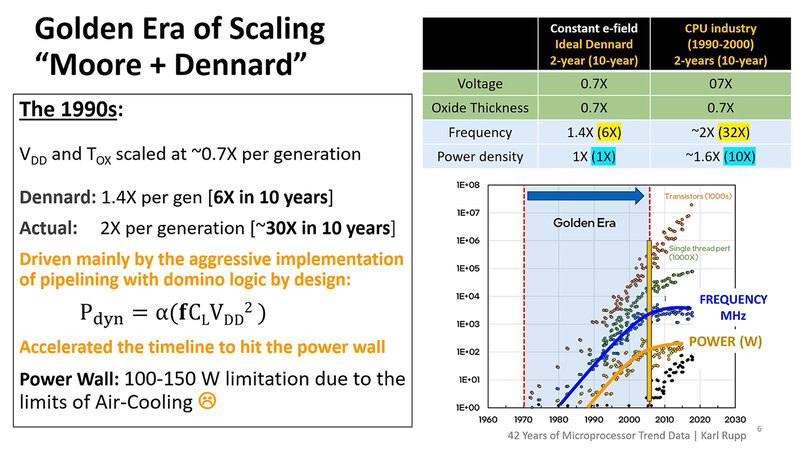

2005年までというのは黄金時代、あるいはフリーランチの時代などとも呼ばれているが、要するにこの時代はプロセスを微細化すると、動作周波数が上がり、トランジスタ密度も上がるのに、電圧が下がるお陰で消費電力が変わらないというものであった。

これはデナード則と呼ばれるもので、1974年にIBMのRobert H. Dennard博士が提唱した経験則である。正確に言えば、プロセスを1世代進めると、トランジスタの寸法が30%(面積で言えばほぼ半分に)縮まることで、利用できるトランジスタの数が2倍になる。

一方駆動電圧も0.7倍になり、消費電力は半分になる(駆動電圧の2乗に比例するので)。しかも寸法が0.7倍ということは遅延も0.7倍になるので、動作周波数で言えば1.4倍高速に動かせるという、夢のような話である。

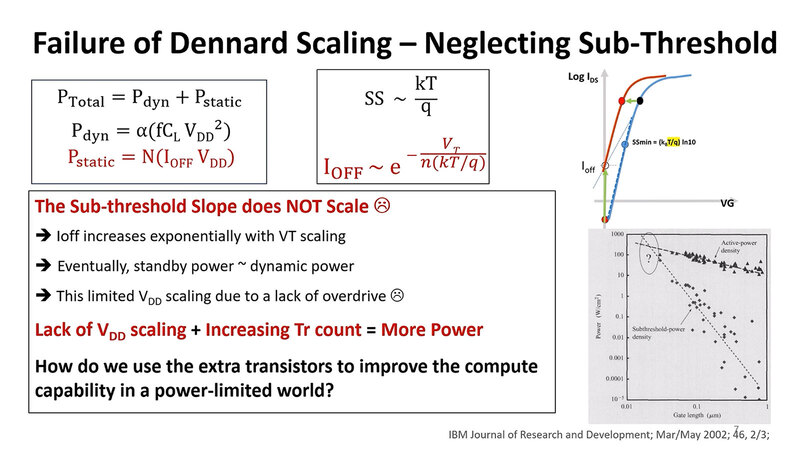

実際のところ、上の画像の右図にあるように、1970年代から2004年頃まではこの夢のようなプロセス微細化による高性能化が続いた。これに歯止めがかかったのは、直接的には微細化にともなうリーク電流の急増である。ただこのあと以下のように、デナード則が崩壊することになった。

- 寸法の微細化が思うように進まない

- 微細化しても遅延がそんなに減らない

- 駆動電圧をそれほど下げられなくなった

- 消費電力はなにもしないとむしろ増える

上の画像で2005年あたりを境に、動作周波数がさっぱり上がらなくなり、またPowerも100W超で頭打ちになったのは、左の下にあるように空冷で許容できる消費電力は100~150W程度であり、この消費電力の枠の中でもう動作周波数が上がらなくなったという実情である。

特に駆動電圧が下げられないことが、消費電力を下げるうえで一番大きな障害になっているとする。

※お詫びと訂正:記事初出時、NVIDIAのBlackwellのトランジスタ数に誤りがありました。記事を訂正してお詫びします。

画期的なプロセス技術をインテルが次々と開発

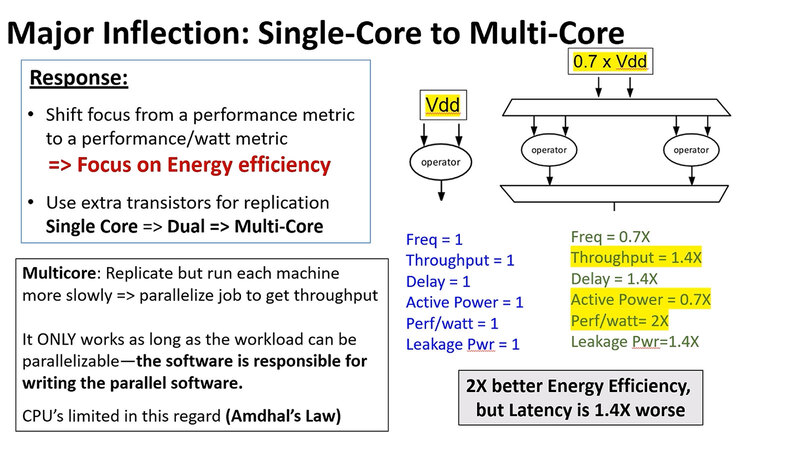

性能を上げるための最初の手段がマルチコア化であるが、トータルの性能は上がってもレイテンシー、別の言い方をすればシングルスレッド性能はむしろ落ちることになる。

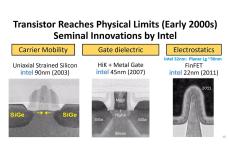

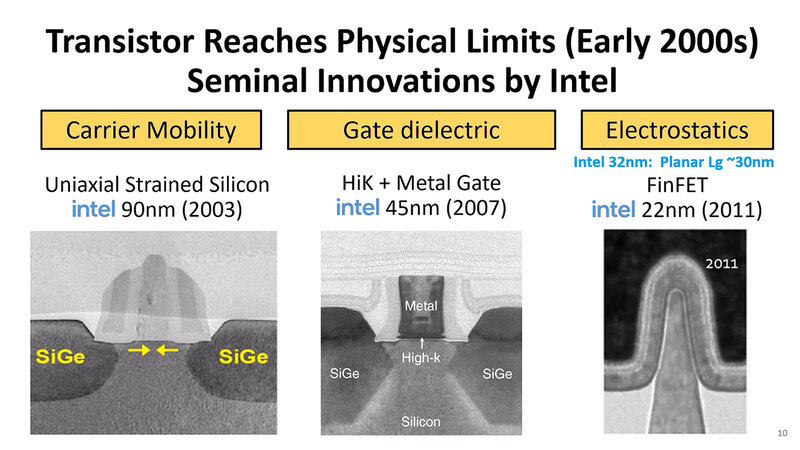

当然トランジスタそのものの改良も続けられてきた。まずは90nm世代で歪シリコンが導入されたが、45nm世代ではHKMG(High-K Metal Gate)、22nm世代ではFinFETが導入された。

このFinFETの導入までは、間違いなくインテルがプロセス技術の最先端を走っていた。ちなみに講演ではこの後、HKMGとFinFETがいかに画期的な技術であったかのスライドが2枚ほど続くが、これはこれまでも説明してきた話なので割愛する。

これに続くものがGAA(Gate All Around)で、Ribbon FETという名称で今まさに開発をしている最中であるが、逆に最中過ぎて細かい情報を出せないためか、Intel 20A/18Aに関する言及はすっぱり落ちている。Intel 20Aのキャンセルの話などはいろいろ生々しすぎるためだろう。おそらくあと10年くらいすれば、「なぜIntel 20Aがダメだったのか」という振り返りの話がでてくるかもしれない。

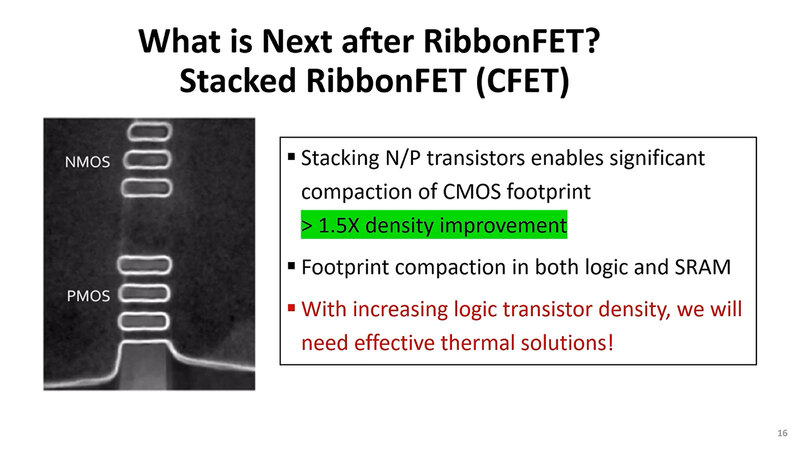

ここから今後のプロセスに関する話となる。まずトランジスタの構造で言えば、Ribbon FETの先にStacked Ribbon FETがCFETとして利用されるという見通しを示した。

連載236回で、CMOS(Complementary Metal Oxide Semiconductor)はP型とN型の2種類のトランジスタを組み合わせて構成される(よってComplementary:相補型という呼び方をされる)という話をしたが、プレナー型にしてもFinFETにしても、NMOSとPMOSを平面的に2つ並べて間を配線でつなぐことになるので、トランジスタ2個分の面積を必要とする。

ところが積層すると、面積がトランジスタ1個分で済むので、トランジスタの密度が倍になることになる(実際はそこまで向上せず、1.5倍程度だが)。ただ「トランジスタの密度向上にともない、効果的な放熱手段が必要」と書いてあるように、単純に重ねて終わりという話ではない。そもそも重ねるのも大変だし、間の配線の構築も必要であることを考えると、決して難易度は低くない。

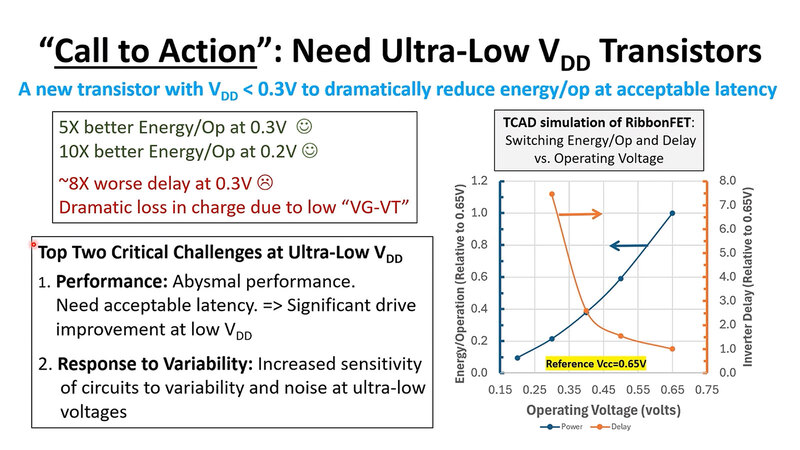

電圧を0.3V未満に抑えて動作効率を5倍以上に引き上げつつ 性能は0.65V動作のトランジスタの半分程度まで引き上げるのが目標

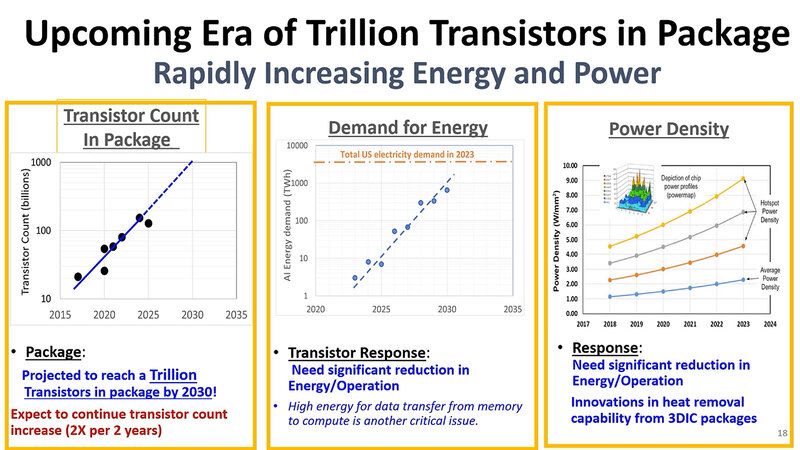

ただ、2030年を目指すにあたっては、単に面積の縮小だけでなく、消費電力と放熱の問題も解決する必要があるとする。まず消費電力にからむ話で、とにかく電圧を下げないことには消費電力が下がらないのだが、電圧を下げると同時にトランジスタの速度も大きく落ちてしまう。

0.6Vで動作するトランジスタを0.3Vまで落とすとエネルギー効率は5倍に向上するが、トランジスタのスイッチング速度が8分の1になってしまう。

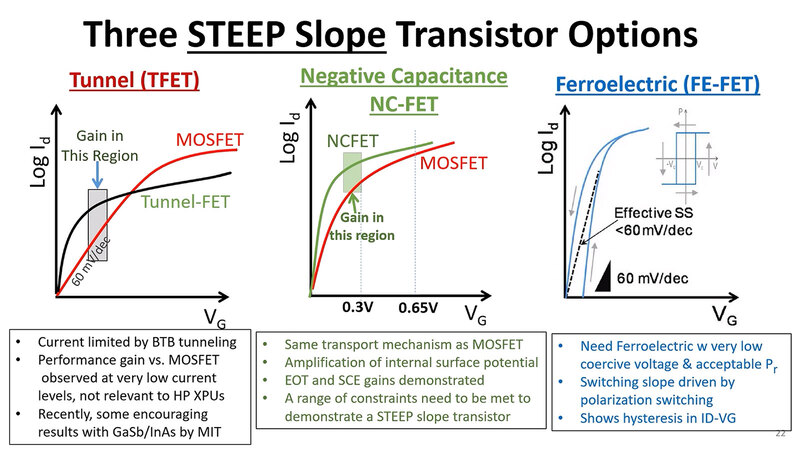

これを改善するトランジスタの構造をSteep Slope Transistorとして各社さまざまな技法を検討している。

そのSteep Slope Transistorの候補して現在はTunnel FET(トンネル効果を利用したトランジスタ)、Negative Capacitance FET(NC-FET:強誘電薄膜をゲート絶縁膜に利用することで、負の電界容量を持つ状態を作り出し、これを利用したトランジスタ)とFerroelectric FET(同様に強誘電体膜をゲート絶縁膜に用いる技法だが、Negative Capacitance FETとは異なる)の3つを候補として挙げている。

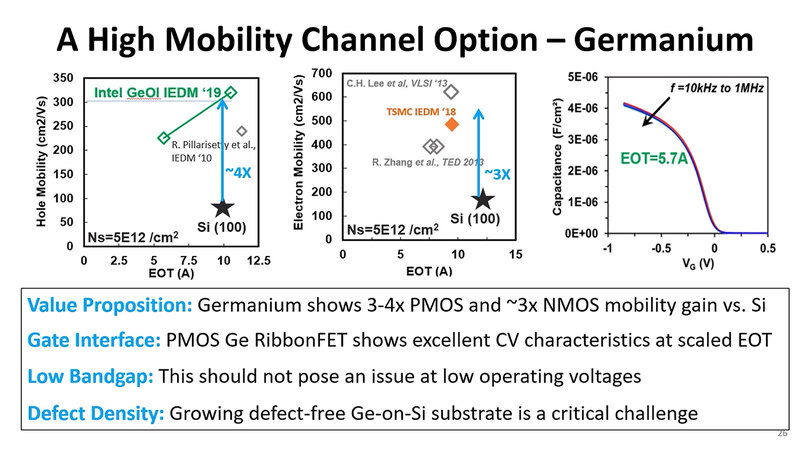

一方チャネルの電荷移動量の改善に関しては、シリコンをGe(ゲルマニウム)に変更することで、大幅に性能が改善される(PMOSで3~4倍、NMOSで3倍)ために有望である、としている。

これを組み合わせた、1つのビジョンが下の画像だ。電圧を0.3V未満に抑えて動作効率を5倍以上に引き上げつつ、性能は今の0.65V動作のトランジスタの半分程度まで引き上げることを目指している。

ただこれはトランジスタレベルでの改良であり、実際にはチップにする際にまた別の配慮が必要であるが、それは別の招待講演で説明されたので、次回はそちらをご紹介しよう。

この記事に関連するニュース

-

銅配線をルテニウム配線に変えると抵抗を25%削減できる IEDM 2024レポート

ASCII.jp / 2025年2月3日 12時0分

-

酸化ハフニウム(HfO2)でフィンをカバーすると性能が改善、TMD半導体の実現に近づく IEDM 2024レポート

ASCII.jp / 2025年1月27日 12時0分

-

パワー半導体「産業用LV100タイプ 1.2kV IGBTモジュール」サンプル提供開始

PR TIMES / 2025年1月14日 16時15分

-

トランジスタ最先端! RibbonFETに最適なゲート長とフィン厚が判明 IEDM 2024レポート

ASCII.jp / 2025年1月13日 12時0分

-

NVIDIAが新型GPU「GeForce RTX 50シリーズ」を発表 新アーキテクチャ「Blackwell」でパフォーマンスを約2倍向上 モバイル向けも

ITmedia PC USER / 2025年1月7日 18時50分

ランキング

-

1X、「コミュニティ」の投稿が誰にでも表示される仕様変更 ユーザー当惑「最悪のアプデ」

ITmedia NEWS / 2025年2月4日 19時13分

-

2現役の情シスが考える、KDDIのビジネスPC向け“月額費用なし”データ使い放題サービス「ConnectIN」の強み

ITmedia PC USER / 2025年2月4日 12時40分

-

3ゆたぼん、フジテレビ番組で“OA希望の発言”カットされ「許せへん」 スタッフ快諾も電波乗らず……「放送の仕方もヒドかった」「面白おかしく取り上げられて」

ねとらぼ / 2025年2月5日 17時0分

-

4ラップの空箱は捨てないで! “目からウロコ”な活用法が240万再生 「天才だ…」【リメイク】

ねとらぼ / 2025年2月4日 7時30分

-

5ニットの収納“生地が伸びる問題”を解決 目からウロコの裏ワザに「その手は思いつかなかった」「やってみます」

ねとらぼ / 2025年2月4日 7時30分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください