imecの研究者が解説 - 先端3D SoCにおける効率的なESD保護対策 第2回 3D相互接続密度の増加による0V ESD保護の必要性

マイナビニュース / 2024年7月25日 6時30分

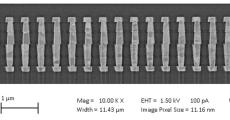

3D相互接続密度の継続的な増加により、内部インタフェースの保護が複雑になっている。半導体業界では、ロジック/メモリオンロジックタイプのスタッキングアプリケーションなどを対象に、各3D相互接続技術をより細分化した相互接続へと推し進めている。imecの研究者は最近、相互接続パッドピッチが2μmというダイ・ツー・ウェハのハイブリッドボンディングを実証した。ウェハ・ツー・ウェハのハイブリッドボンディングでは、わずか400nmの相互接続ピッチが達成され、ダイの表面で1mm2あたり100万を超えるCu相互接続に相当する[2][3]。

この進化のマイナス面は何だろうか? ボンディング中に内部I/O回路をESDから保護する保護回路に使用できるスペースがますます少なくなっている。最終的には、スペースがまったくなくなることが予想される。これにより、設計者はI/OインタフェースのESD保護回路をますます小さくせざるを得なくなる。ただし、これにより、スタッキングおよびアセンブリ中の内部I/OピンのESD耐性が低下する。そのため、ESDコミュニティは、ボンディング中のESDイベントの防止をますます推進し、最終的には可能な限り「内部」ESD保護回路の必要性を排除しようとしている。

ESD保護を少なくすることは、面積の消費量が少なくなるだけでなく、I/O回路のパフォーマンスにもメリットをもたらす。ESD保護回路は、寄生容量が追加されるため、保護対象の回路のパフォーマンスを直接低下させる可能性がある。したがって、ESD保護を追加することは、堅牢性とパフォーマンスのトレードオフになっている。

ESDの基礎的理解の強化

0V ESD保護に移行するには、ボンディング中にI/O内部ピンに発生する可能性のあるESDイベントに関する詳細な知識が必要である。「標準」モノリシックICの場合、ESD保護は比較的よく理解されている。しかし、2.5D/3Dテクノロジの内部I/Oインタフェースの場合、ESDイベントの影響はまだ明確ではない。

現在、2.5D/3DボンディングテクノロジにおけるESD保護対策の要件と目標レベルを規定した標準は存在しない。ESD関連の会議やワークショップで繰り返し報告されているように、テストに関する従来の想定は、高度なボンディングテクノロジや内部ピンには当てはまらないようである。測定結果から、ESDイベント後のESDパルスは、ピーク電流、パルス幅、立ち上がり時間に関して、たとえば標準CDMテストで想定されるものとは異なる動作をすることが示されている。

-

-

- 1

- 2

-

この記事に関連するニュース

-

imecの研究者が解説 - 先端3D SoCにおける効率的なESD保護対策 第1回 2.5D/3D ICでのESDの複雑さを増加させる内部I/Oインタフェース

マイナビニュース / 2024年7月24日 6時30分

-

阪大など、レーザー駆動中性子源で飛行時間計測装置の大幅な小型化を実現

マイナビニュース / 2024年7月18日 19時12分

-

TSMC、Intel、SK hynixが語る半導体産業/技術の将来展望 - ITF World 2024 第2回 TSMCのSVPが語った半導体の技術進化と産業の発展の密接な関係性

マイナビニュース / 2024年7月18日 11時29分

-

TSMC、Intel、SK hynixが語る半導体産業/技術の将来展望 - ITF World 2024 第1回 メモリの技術革新の重要性を語ったSK hynix

マイナビニュース / 2024年7月17日 6時50分

-

imecがロジック向け微細化ロードマップを更新、ASMLが超高NAのEUV装置の開発を開始

マイナビニュース / 2024年6月25日 14時51分

ランキング

-

1「ガンズ」スラッシュ義娘が急死 死後に更新されたインスタの内容が波紋「謝る必要なんてない」「こんな気持ちにならないでほしかった」

ねとらぼ / 2024年7月24日 16時51分

-

2全世界で発生したCrowdStrike“ブルスク”問題、原因からIT担当者が検討すべきセキュリティ対策を考察する

ITmedia PC USER / 2024年7月24日 15時5分

-

3プロが本気で“アンパンマンの塗り絵”をしたら…… 衝撃の仕上がりが360万再生「凄すぎて笑うしかないww」「チーズが、、、」

ねとらぼ / 2024年7月18日 22時0分

-

4小1の子どもに「オシャレノート」を買い与えたら“まさかの号泣”…… 納得の理由が「そりゃあ仕方ない」と810万回表示

ねとらぼ / 2024年7月24日 7時45分

-

5『ドラクエ』わずかな確率にかけて狩りまくった! 欲しすぎた、最強の「ドロップ装備」

マグミクス / 2024年7月24日 21時25分

複数ページをまたぐ記事です

記事の最終ページでミッション達成してください