VLSIシンポジウム2024プレビュー 第4回 次世代技術となる高密度2.5D実装や次世代3Dトランジスタ積層を目指す研究

マイナビニュース / 2024年5月10日 6時31分

VLSIシンポジウム 2024におけるプロセス・デバイス技術分野(従来のVLSI Technology Symposium)の採択論文数は95件。そのうち、今回はデバイス・プロセス部門の注目論文の最後として高密度2.5D実装および3Dトランジスタ垂直積層に向けた3件の取り組みを紹介する。

○Foveros Face-to-Faceアーキテクチャによるシリコンインターポーザと高密度MIMキャパシタ集積をIntelが発表

Integration of Si-Interposer and High Density MIM Capacitor on 2.5D Foveros Face-to-Face Architecture(論文番号:T9-1)

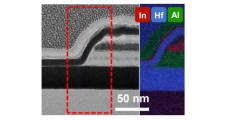

シリコンインターポーザを介して異なるコンピューティング要素を集積することで、ムーアの法則を超えたスケーリングの実現が期待されている。Intelは、パッシブシリコンインターポーザにより異なるチップレットを、バンプシリコン貫通電極を通じて、36μm間隔の微細マイクロバンプでデバイス面同士の貼り合わせ接続が可能であることを報告する。

このシリコンインターポーザには、電圧低下や雑音を抑制するための高密度MIMデカップリングキャパシタが集積されており、実際の製品においては、シリコンインターポーザ中あるいはチップレットに埋め込んだ高密度MIMキャパシタを用いることができるとしており、発表内容としては高密度MIMキャパシタの製造工程や電気特性、信頼性評価、高密度MIMキャパシタを集積したシリコンインターポーザによる性能向上などが予定されている模様である。

○熱影響を考慮したオングストローム世代のブロックレベルPPA性能評価をimecが発表

Thermal Considerations for Block-Level PPA Assessment in Angstrom Era: A Comparison Study of Nanosheet FETs (A10) & Complementary FETs (A5)(論文番号:T5-4)

imecは熱影響を考慮したブロックレベルPPA(性能・消費電力・面積)性能のNSFET(ナノシートFET)とCFET(コンプリメンタリFET)の比較結果を発表する。

NSFETとCFETはそれぞれA10、A5世代というオングストローム世代の技術として期待されている。オープンソースの多数コアアーキテクチャを用いた解析の結果、A10からA5世代で2.5%のFmax増加、25%の電力低下、27%のサイクル当たりの電力低下、35%の面積縮小が見積もられ、結果として0.7V/25℃の環境では15%の電力密度増加となるという。このPPA性能評価手法は動的な熱影響の管理が必要なアプリケーションにとって重要となるパッケージレベルの高速熱解析が可能なシミュレータを備えており、温度に対して指数関数的に発生するリーク電力増加を考慮したものとなっているとする。

この記事に関連するニュース

-

VLSIシンポジウム2024プレビュー 第8回 有線通信回路分野と光送受信回路分野の注目論文

マイナビニュース / 2024年5月17日 6時57分

-

VLSIシンポジウム2024プレビュー 第6回 プロセッサ/AI半導体/メモリアーキテクチャ分野の注目論文

マイナビニュース / 2024年5月15日 6時40分

-

VLSIシンポジウム2024プレビュー 第3回 メモリ分野では新型NVDRAMやNVSRAM、新構造3D NANDなどが登場

マイナビニュース / 2024年5月9日 6時28分

-

VLSIシンポジウム2024プレビュー 第2回 超微細化に向けた取り組みが多数発表されるプロセス・デバイス技術

マイナビニュース / 2024年5月8日 6時27分

-

プロセスノードに加えて新技術も売り込む! Intelが半導体の「受託生産」で使う“武器”【後編】

ITmedia PC USER / 2024年4月26日 17時5分

ランキング

-

1富士フイルム新機種に重くのしかかる為替レート 「X-T50」の値段は「X-T30 II」の倍以上に

ITmedia NEWS / 2024年5月18日 7時20分

-

2モトローラの新ミドル機は控えめ価格なのに、FeliCa&防水&薄型軽量に美しいデザインと贅沢な1台

ASCII.jp / 2024年5月19日 12時0分

-

3「思わず笑った」 ハードオフに4万4000円で売られていた“まさかのフィギュア”に仰天 「玄関に置いときたい」

ねとらぼ / 2024年5月19日 12時0分

-

4Apple Watchを外出時にほぼ持ち出さなくなった理由

ITmedia Mobile / 2024年5月19日 10時5分

-

5Googleドライブ、カーソルを合わせるだけでビデオのプレビューが可能に

マイナビニュース / 2024年5月20日 18時40分

複数ページをまたぐ記事です

記事の最終ページでミッション達成してください