「Lunar Lake」Deep Diveレポート - 【Part 2】Memory、GPU、NPUについて

マイナビニュース / 2024年7月4日 14時23分

前回はP-CoreとE-Coreの話に終始してしまったので、今回はもう少し広範な話をしたい。

謎のMemory Side Cache

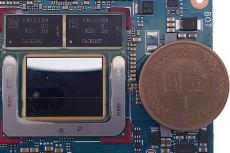

Photo01は基調講演のスライドから切り出して、ついでに複数のスライドの情報を重ね合わせたものである。上側がCompute Tileであるが、向かって右端にP-Core×4+12MB L3 Cache、その下にIPU(Image Processing Unit:通常ならISPと呼ばれるが、要するにカメラ入力に対応した画像処理エンジン)、右にNoCが入り、そのNoCの上にMedia EngineとMemory Side Cache、NOCの下にE-Core×4+4MB L2 CacheとDisplay Engine、その左がNPUとなり、一番左端がGPUとなっている。ちなみにCompute Tile右下の青い部分はD2D(Die to Die Interface)で、ここでPlatform Controller Tileと接続する形になる。

そこまでは良いとして、このMemory Side Cacheとは何者か? という話になる。実はこのMemory Side Cache、Technical Sessionでは一切説明が無かった。ただ基調講演のスライド(Photo02)の中にヒントが示されていた。このMemory Side Cache、容量は8MBとの事であるが、これを利用できるのはCPU(と一部I/O Device)のみで、少なくともGPUからは扱えない事は質疑応答の結果として判明している。要するにGPUでRay Tracingを行う時のWork Areaだったり、解像度を上げたときのWork BufferあるいはTexture Cache的な使い方は一切出来ない事になっているそうだ。

さて基調講演でも詳しい話は一切出なかったのだが、このMemory Side CacheがHome Agent、つまり全体のCache Coherencyの管理を行っており、P-CoreのL3やE-CoreのL2にはCoherency Agentのみが置かれている(あとはPlatform Controller TileにもI/O Coherency Agentが置かれる)という事は、このMemory Side CacheはP-CoreのL3、あるいはE-CoreのL2のBackside Cacheとしてだけ働くことになる形だ。ただこれがL4にならないところがポイントである(L4として働くのであれば、その旨がP-CoreやE-Coreの説明に当然あってしかるべきだからだ)。

この記事に関連するニュース

-

Lunar LakeではPコアのハイパースレッディングを廃止 インテル CPUロードマップ

ASCII.jp / 2024年7月1日 18時0分

-

「Lunar Lake」Deep Diveレポート - 【Part 1】P-Core&E-CoreとPackageについて

マイナビニュース / 2024年6月29日 12時31分

-

Intel Tech Talkで見えたLunar Lakeにおける低消費電力と高性能の両立へのこだわり

マイナビニュース / 2024年6月27日 6時45分

-

Lunar Lakeはウェハー1枚からMeteor Lakeの半分しか取れない インテル CPUロードマップ

ASCII.jp / 2024年6月24日 12時0分

-

Lunar Lakeは「Snapdragon X Eliteを凌駕し、x86だが電力効率が良い」とインテルCEOが断言

ASCII.jp / 2024年6月6日 12時0分

ランキング

-

1人気VTuber、サイバー攻撃余波?で本名公表 問われる妥当性、それでも「認めざるを得なかった」理由

J-CASTニュース / 2024年7月4日 12時58分

-

2こ、これは……! Netflixで見られる“まさかの映画”に思わず二度見 「まさかネトフリでやってくれるとは!!」

ねとらぼ / 2024年7月4日 7時0分

-

3「鬼すぎない?」 大正製薬の広告が“性差別”と物議…… 男女の“非対称性”に「昭和かな?」「時代にあってない」

ねとらぼ / 2024年7月4日 18時32分

-

4老後の趣味で気軽に“塗り絵”を始めて1年後…… めきめき上達した70代女性の美麗な水彩画に「本当にすごい…」「感動です」

ねとらぼ / 2024年6月29日 22時0分

-

5都知事選で「YouTube」存在感増す 候補者30人がチャンネル保有、タイトルに個人名が急増──エビリー調査

ITmedia NEWS / 2024年7月4日 12時46分

複数ページをまたぐ記事です

記事の最終ページでミッション達成してください