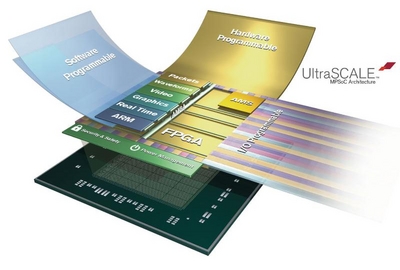

ザイリンクス、業界初の All Programmable MPSoC 向けUltraScale マルチプロセッシング アーキテクチャを発表

PR TIMES / 2014年5月7日 10時20分

次世代 Zynq UltraScale MPSoC により、タスクごとに適切なエンジンを提供し高付加価値化を追求

ザイリンクス社 (本社 : 米国カリフォルニア州サンノゼ、NASDQ : XLNX) は 2 月24 日 (米国時間)、「Embedded World 2014」において次世代Zynq(R) UltraScale MPSoC 向け UltraScale(TM) マルチプロセッシング (MP) アーキテクチャを発表した。業界で成功を収めた Zynq-7000 All Programmable SoC をベースに構築された新たな UltraScale MPSoC アーキテクチャは、ザイリンクスのASIC クラス UltraScale FPGA および 3D IC アーキテクチャを拡張することによりヘテロジニアス マルチプロセッシングを実現し、「タスクごとに適切なエンジンを提供する」ことを可能にした。Zynq-7000 によって業界初のAll Programmable SoC を実現したザイリンクスが、UltraScale MPSoC によって初の All Programmable MPSoC を実現したことになる。

新しい All Programmable MPSoC アーキテクチャは 仮想化のサポートにより、32 ビットから 64 ビットプロセッサのスケーラビリティを提供し、ソフトウェアとハードウェアエンジンの連携動作によるリアルタイム制御、グラフィックス/ビデオの処理、波形/パケットの処理などを実現する。さらに、次世代インターコネクトとメモリ、最新の電力管理機能などの技術強化によって、マルチレベルのセキュリティ/安全性/信頼性を提供する。UltraScale MPSoC アーキテクチャは、システム消費電力を低減しつつ、システムのパフォーマンスとインテグレーションを飛躍的に向上することが可能である。これは、TSMC 社の 16nm FinFET プロセスを活用することで、ヘテロジニアス マルチプロセッシングと業界最速の FinFET を組み合わせることが可能になったためである。

こうした新しいアーキテクチャ構成要素に加え、Vivado(R) Design Suite とさまざまなアブストラクションの設計環境も同時に提供されるため、プログラミングが大幅に簡素化され生産性を向上することができる。C、C++、OpenCL をベースとするデザイン アブストラクションをはじめ、Mathworks 社や National Instruments 社などのサードパーティ システム レベル アブストラクション、IP ベースのデザインアブストラクションおよびオートメーションなどが利用可能である。これらの環境では、デファクト スタンダードである 28nm Zynq-7000 All Programmable SoC からのソフトウェア マイグレーションも容易に行える。新しい MPSoC アーキテクチャをサポートするため、 Zynq SW エコシステムや OS サポート、デバッガ、各種IP ツール、基板、デザイン サービスなどが提供される。

UltraScale MPSoC アーキテクチャについて詳しくはjapan.xilinx.com/ultrascalempsoc を参照されたい。

■ザイリンクスについて

ザイリンクスは、All Programmable FPGA および SoC、3D IC の世界的なリーディング プロバイダーである。業界をリードするこれらデバイスを次世代設計環境および IP とともに提供することで、プログラマブル ロジックからプログラマブルシステム インテグレーションまで、幅広いユーザー ニーズに応える。詳しい情報は、ウェブサイト japan.xilinx.com で公開している。

※ザイリンクスの名称およびロゴ、Artix、ISE、Kintex、Spartan、Virtex、Vivado、Zynq、その他本プレスリリースに記載のブランド名は米国およびその他各国のザイリンクスの登録商標または商標です。その他すべての名称は、それぞれの所有者に帰属します。

下記のザイリンクス株式会社ウェブサイトもご参照ください。

・トップページ : http://japan.xilinx.com/index.htm

・プレスリリース (日本語) : http://japan.xilinx.com/japan/j_prs_rls/

・このリリースの全文は次の URL を参照のこと :

http://japan.xilinx.com/japan/j_prs_rls/2014/ultrascale/first-all-programmable-mpsoc.htm

企業プレスリリース詳細へ

PRTIMESトップへ

この記事に関連するニュース

-

マウザー、Intelから独立したFPGA専門の新会社「Altera」製品の在庫を拡充

PR TIMES / 2024年4月24日 14時15分

-

SUBARUがAMDとの協業を深化、AMDがVersal AI Edge Gen2ベースのカスタムSoCを提供へ

マイナビニュース / 2024年4月22日 17時4分

-

BlackBerry、ロボティクス産業の基盤的な精度と制御の進化に向けて、AMDとの協業を発表

PR TIMES / 2024年4月12日 12時45分

-

AMD、外付けSoCが不要となった第2世代「Versal」を発表

マイナビニュース / 2024年4月9日 19時28分

-

あらゆるAIニーズに旧Xilinxとのシナジーで対応を進めるAMD、日本でも市場を拡大

マイナビニュース / 2024年4月5日 10時45分

ランキング

-

1【解説】円安どこまで進む? 深刻…家計にも影響、為替介入の可能性は

日テレNEWS NNN / 2024年4月25日 20時5分

-

2なぜ歯磨き粉はミント味? ヒット商品の誕生には「無駄」が必要なワケ

ITmedia ビジネスオンライン / 2024年4月26日 8時0分

-

3濃口醤油と淡口醤油、塩分が高いのはどっち?…醤油の「色の濃さ」と「味の濃さ」の知られざる関係

プレジデントオンライン / 2024年4月26日 8時15分

-

4英郵便局の冤罪事件、会計システム原因の富士通社長「申し訳ない」と謝罪…1月にドラマ化され批判強まる

読売新聞 / 2024年4月25日 23時0分

-

5突然現場に現れて「良案」を言い出す上司の弊害 「気になったら即座に直したい」欲求への抗い方

東洋経済オンライン / 2024年4月26日 8時0分

記事ミッション中・・・

記事にリアクションする

![]()

記事ミッション中・・・

記事にリアクションする

エラーが発生しました

ページを再読み込みして

ください